Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной технике и систем управления.

Известно троичное счетное устройство (а.с. СССР №1506547 от 25.01.88, МКИ: Н 03 К 29/00 "Троичное счетное устройство", А.С.Галкин, В.Е.Гордиенко, В.П.Грибок, А.М.Воловик, опубликовано 27.09.89, бюл. №33), содержащее два RS-триггера (на двух элементах И-НЕ), четыре двухвходовых элемента И-НЕ и два многовходовых элемента И-НЕ, входная шина соединена с первым входом первого двухвходового элемента И-НЕ и с первым входом первого многовходового элемента И-НЕ, второй вход которого подключен к  -выходу первого RS-триггера, а выход соединен с первым входом второго двухвходового элемента И-НЕ и

-выходу первого RS-триггера, а выход соединен с первым входом второго двухвходового элемента И-НЕ и  -входом второго RS-триггера,

-входом второго RS-триггера,  -вход которого соединен с первым входом второго многовходового элемента И-НЕ и выходом первого двухвходового элемента И-НЕ, а

-вход которого соединен с первым входом второго многовходового элемента И-НЕ и выходом первого двухвходового элемента И-НЕ, а  -выход подключен к второму входу второго двухвходового элемента И-НЕ, выход которого соединен с S-входом первого RS-триггера,

-выход подключен к второму входу второго двухвходового элемента И-НЕ, выход которого соединен с S-входом первого RS-триггера,  -выход которого соединен с первым входом третьего двухвходового элемента И-НЕ, второй вход которого подключен к

-выход которого соединен с первым входом третьего двухвходового элемента И-НЕ, второй вход которого подключен к  -входу первого RS-триггера, второй вход первого двухвходового элемента И-НЕ соединен с выходом четвертого двухвходового элемента И-НЕ, первый вход которого подключен к выходу первого двухвходового элемента И-НЕ, а второй вход - к выходу второго двухвходового элемента И-НЕ и к второму входу второго многовходового элемента И-НЕ, третий вход которого соединен с входной шиной, а выход подключен к третьему входу первого многовходового элемента И-НЕ и к второму входу третьего двухвходового элемента И-НЕ, выход которого соединен с четвертым входом второго многовходового элемента И-НЕ.

-входу первого RS-триггера, второй вход первого двухвходового элемента И-НЕ соединен с выходом четвертого двухвходового элемента И-НЕ, первый вход которого подключен к выходу первого двухвходового элемента И-НЕ, а второй вход - к выходу второго двухвходового элемента И-НЕ и к второму входу второго многовходового элемента И-НЕ, третий вход которого соединен с входной шиной, а выход подключен к третьему входу первого многовходового элемента И-НЕ и к второму входу третьего двухвходового элемента И-НЕ, выход которого соединен с четвертым входом второго многовходового элемента И-НЕ.

Основным недостатком указанного устройства является низкая помехоустойчивость, определяемая помехоустойчивостью логических элементов интегральных микросхем.

Известно счетное устройство на многостабильных пересчетных схемах (см. книгу: Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. - М: Радио и связь, 1990. - с. 271, рис. 6.36в), содержащее в каждом разряде многостабильную пересчетную схему и первый и второй элементы совпадения, первые входы первых элементов совпадения каждого разряда соединены с входной шиной, выходы (инверсные) - с тактовыми входами многостабильных пересчетных схем, а вторые входы - с первыми входами вторых элементов совпадения и с выходами (прямыми) вторых элементов совпадения предыдущих разрядов, вторые входы вторых элементов совпадения каждого разряда соединены с соответствующими выходами многостабильных пересчетных схем, выход второго элемента совпадения последнего разряда соединен с выходной шиной.

Указанное счетное устройство при использовании трехстабильных пересчетных схем может работать в позиционном троичном коде. Трехстабильные пересчетные схемы строятся на основе логических элементов (см. книгу: Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. - М.: Радио и связь, 1990, с.246, рис. 6.16, с.249, рис. 6.18, с.255, рис. 6.23, с.261, рис. 6.28, а также а.с. СССР №1422405 от 21.01.87, МКИ: Н 03 К 29/00, "Троичный счетный триггер", А.С.Галкин, В.П.Грибок, Л.Б.Лимоновская, В.О Твердохлебова, опубликовано 07.09.88, бюл. №33). Известна трехстабильная пересчетная схема (а.с. СССР №1354414 от 17.01.86, МКИ: Н 03 К 29/40 "Делитель частоты на три", В.А.Никашин, С.Н.Фролов, опубликовано 23.11.87, бюл. №43), содержащая первый триггер, прямой выход которого соединен с D-входом второго триггера, инверсный выход которого соединен с D-входом первого триггера, С-вход которого соединен с С-входом второго триггера и с входной шиной, логический элемент, выход которого соединен с R-входом первого триггера, первый вход - с входной шиной, второй вход - с D-входом первого триггера.

Основным недостатком известных счетных устройств на многостабильных пересчетных схемах является низкая помехоустойчивость, определяемая помехоустойчивостью логических элементов интегральных микросхем.

Достигаемым техническим результатом является повышение помехоустойчивости троичного счетного устройства.

Указанный технический результат достигается тем, что троичное счетное устройство содержит в каждом разряде первый и второй элементы совпадения и трехстабильную пересчетную схему на основе двух D-триггеров, выходы первых элементов совпадения каждого разряда соединены с тактовыми входами трехстабильных пересчетных схем, первые входы первых элементов совпадения соединены с первыми входами вторых элементов совпадения и с выходами вторых элементов совпадения предыдущих разрядов, выход второго элемента совпадения последнего разряда соединен с выходной шиной. Новым является то, что дополнительно введены в каждый разряд третий элемент совпадения в виде элемента И и первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый элемент совпадения выполнен в виде элемента ИЛИ-НЕ, второй элемент совпадения - в виде элемента ИЛИ, первые входы элемента ИЛИ-НЕ и элемента ИЛИ первого разряда соединены с входной шиной, первый выход трехстабильной пересчетной схемы каждого разряда соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с инверсным входом третьего элемента совпадения И, второй выход - с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с управляющим входом трехстабильной пересчетной схемы и с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда, а выход - с прямым входом третьего элемента совпадения И, прямой и инверсный выходы которого соединены соответственно со вторыми входами элементов совпадения ИЛИ-НЕ и ИЛИ, второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последнего разряда соединен с управляющей шиной устройства, в трехстабильную пересчетную схему введены четвертый элемент совпадения И, комбинационный двухразрядный сумматор, два инвертора, два диода, три резистора и конденсатор, тактовый вход пересчетной схемы соединен с тактовыми входами первого и второго D-триггеров, с входом младшего разряда числа В комбинационного сумматора и с первым входом четвертого элемента совпадения И, второй вход которого соединен с управляющим входом пересчетной схемы, а выход - со входом старшего разряда числа А комбинационного сумматора, вход младшего разряда числа А которого соединен с выходом первого триггера, вход старшего разряда числа В - с выходом второго D-триггера, выход младшего разряда соединен со входом первого инвертора и через первый резистор с D-входом первого D-триггера, выход старшего разряда сумматора соединен со входом второго инвертора и через второй резистор с D-входом второго D-триггера, выход первого инвертора соединен с катодом первого диода, анод которого соединен с D-входом второго D-триггера и через последовательно соединенные третий резистор и конденсатор с D-входом первого D-триггера и с анодом второго диода, катод которого соединен с выходом второго инвертора.

Указанная совокупность признаков позволяет повысить помехоустойчивость счетного устройства за счет использования однопеременного кода, отличительной особенностью которого является изменение в каждом такте состояния только одного разряда, а также за счет введения в состав пересчетной схемы пассивного запоминающего элемента, обеспечивающего сохранение состояния при воздействии помех.

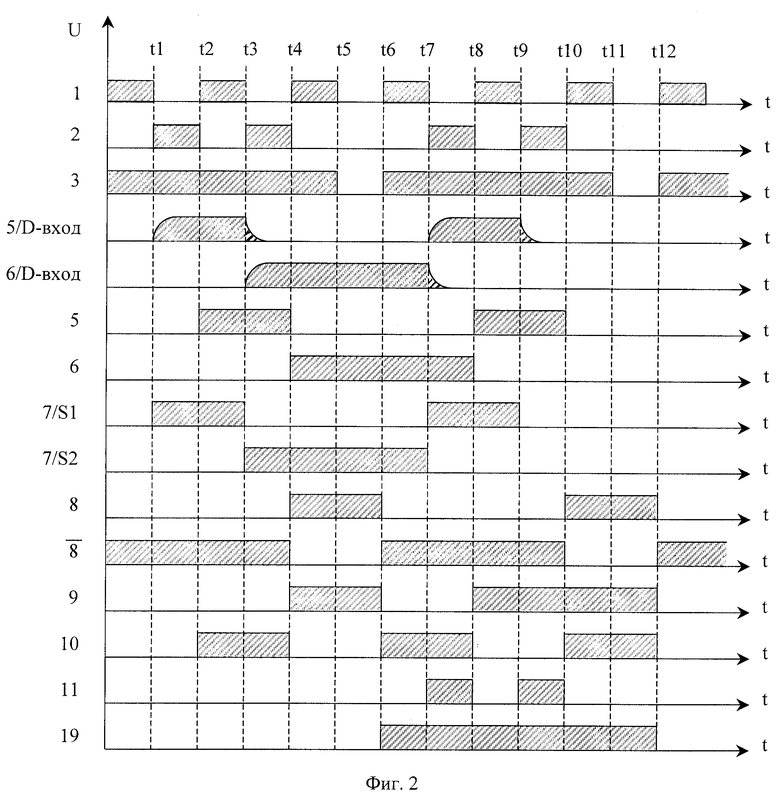

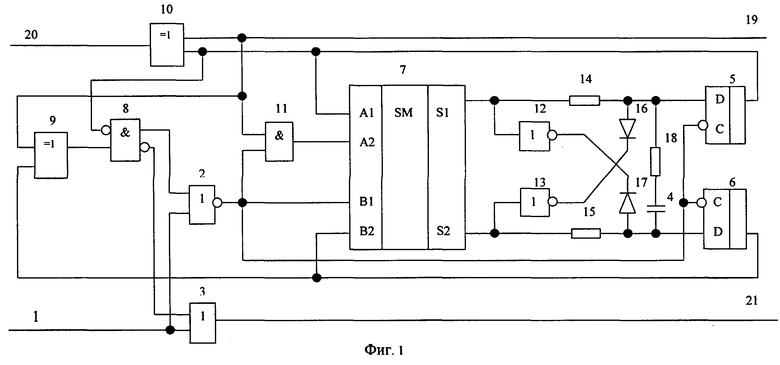

На фиг. 1 приведена схема троичного счетного устройства, на фиг. 2 - временные диаграммы на выходах элементов устройства.

Номер диаграммы на фиг.2 показывает номер элемента, на выходе которого формируется данный сигнал.

Троичное счетное устройство содержит входную шину 1, элемент 2 ИЛИ-НЕ, элемент 3 ИЛИ, конденсатор 4, первый 5 и второй 6 D-триггеры, комбинационный сумматор 7, первый 8 и второй 11 элементы И, первый 10 и второй 9 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 12 и второй 13 инверторы, первый 14, второй 15 и третий 18 резисторы, первый 16 и второй 17 диоды, управляющую шину 19 устройства, управляющую шину 20 предыдущего разряда и выходную шину 21.

Входная шина 1 подключена к первому входу элемента 3 ИЛИ и к первому входу элемента 2 ИЛИ-НЕ, выход которого подключен к первому входу элемента 11 И, к входу младшего разряда числа В комбинационного сумматора 7 и к тактовым входам первого 5 и второго 6 D-триггеров. Выход первого 5 D-триггера подключен к первому входу первого 10 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, к входу младшего разряда числа А комбинационного сумматора 7 и к инверсному входу элемента 8 И, прямой выход которого подключен к второму входу элемента 2 ИЛИ-НЕ, а инверсный выход - к второму входу элемента 3 ИЛИ. Выход второго 6 D-триггера подключен к старшему разряду числа В комбинационного сумматора 7 и к первому входу второго 9 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к второму входу элемента 11 И, к второму входу первого 10 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к управляющей шине 19, подключенной к выходу первого 10 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда. Выход элемента 9 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым входом элемента 8 И. Выход элемента 11 И подключен к старшему разряду числа А комбинационного сумматора 7, выход младшего разряда которого подключен к входу первого 12 инвертора и через первый 14 резистор - к аноду первого 16 диода и к D-входу первого 5 D-триггера. Выход старшего разряда комбинационного сумматора 7 соединен с входом второго 13 инвертора и через второй 15 резистор - с анодом второго 17 диода и D-входом второго 6 D-триггера. Катоды первого 16 и второго 17 диодов соединены с выходами соответственно второго 13 и первого 12 инверторов. D-входы триггеров соединены между собой через последовательно соединенные третий резистор 18 и конденсатор 4. Выход элемента 3 ИЛИ подключен к первому входу элемента 3 ИЛИ последующего разряда, выход элемента 3 ИЛИ старшего разряда подключен к выходной шине устройства. Выход первого элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к управляющей шине 20 предыдущего разряда. Второй вход элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ старшего разряда подключен к управляющей шине 19 устройства.

Устройство работает следующим образом. В начальный момент на входной шине 1 присутствует сигнал логической "1", на управляющей шине 19 сигнал логического "0". Сигнал логической "1" на входной шине 1 определяет формирование логической "1" на выходной шине 21 и логического "0" на выходе элемента 2 ИЛИ-НЕ, на тактовых входах триггеров 5 и 6, на входах старшего разряда числа А и младшего разряда числа В комбинационного сумматора 7. Сигналы логического "0" на прямых выходах триггеров 5 и 6 определяют формирование логического "0" на обоих выходах комбинационного сумматора 7, на выходе элемента 9 ИСКЛЮЧАЮЩЕЕ ИЛИ и на управляющей шине 20 предыдущего разряда. Конденсатор 4 разряжен, элемент 3 ИЛИ закрыт для прохождения тактовых сигналов на последующий разряд сигналом логической "1" с инверсного выхода элемента 8 И, элемент 2 ИЛИ-НЕ открыт сигналом логического "0" с прямого выхода элемента 8 И, элемент 11 закрыт сигналом логического "0" на управляющей шине 19, диоды 16 и 17 смещены в обратном направлении.

Рассмотрим момент времени t1 начала формирования первого тактового импульса на входной шине 1. При этом формируется сигнал логической "1" на входе младшего разряда числа В комбинационного сумматора 7, который приводит к формированию логической "1" на выходе его младшего разряда, на выходе инвертора 12 устанавливается сигнал логического "0", диод 17 открывается, диод 16 по-прежнему смещен в обратном направлении, подтверждая сигнал логической "1" на выходе младшего разряда сумматора 7. Начинается заряд конденсатора 4 через резисторы 14 и 18. Остальные сигналы на выходах элементов в момент времени t1 остаются неизменными.

К моменту времени t2 окончания первого тактового импульса конденсатор 4 зарядится до уровня сигнала логической "1", и в момент t2 на выходе D-триггера 5 сформируется сигнал логической "1", который поступает на младший разряд числа А комбинационного сумматора 7, на котором по входу младшего разряда числа В в этот момент формируется уровень логического "0", в результате чего на выходе младшего разряда сумматора 7 поддерживается сигнал логической "1". На выходе элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ также сформируется сигнал логической "1". Остальные сигналы на выходах элементов в момент времени t2 остаются неизменными.

В момент времени t3 начала второго тактового импульса на входе младшего разряда числа В комбинационного сумматора 7 формируется сигнал логической "1", который приводит к формированию сигнала логического "0" на выходе младшего разряда и сигнала логической "1" на выходе старшего разряда сумматора 7. Инверторы 12 и 13 устанавливаются в состояния логической "1" и логического "0" соответственно, диоды 16 и 17 подтверждают выходные сигналы сумматора 7, начинается перезаряд конденсатора 4 через резистор 15. Остальные сигналы на выходах элементов в момент времени t3 остаются неизменными.

К моменту времени t4 окончания второго тактового импульса процесс перезаряда конденсатора 4 завершится, на D-входе триггера 6 установится уровень логической "1", на D-входе триггера 5 установится уровень логического "0". В момент времени t4 на выходе D-триггера 5, на входах младшего разряда числа В и младшего разряда числа А сумматора 7, на втором входе элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ и на инверсном входе элемента 8 И установятся сигналы логического "0". На выходе D-триггера 6, на входе старшего разряда числа В комбинационного сумматора 7, на первом входе элемента 9 ИСКЛЮЧАЮЩЕЕ ИЛИ и соответственно на его выходе сформируется сигнал логической "1". В результате - на выходе старшего разряда комбинационного сумматора 7 будет поддерживаться сигнал логической "1", на второй вход элемента 2 ИЛИ-НЕ поступит запрет в виде сигнала логической "1", а на второй вход элемента 3 ИЛИ - разрешение для прохождения тактовых сигналов в виде сигнала логического "0". На выходе элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ в момент времени t4 устанавливается сигнал логического "0". Остальные сигналы на выходах элементов в момент времени t4 остаются неизменными.

В момент времени t5 начала третьего тактового импульса на выходе элемента 3 ИЛИ формируется сигнал логического "0", который по шине 21 поступает на первые входы элементов 2 ИЛИ-НЕ и 3 ИЛИ последующего разряда, в результате чего происходит подготовка последующего разряда к переключению. Процессы, протекающие в нем в это время, аналогичны процессам, протекавшим в момент времени t1 в рассматриваемом разряде. Остальные сигналы на выходах элементов в момент времени t5 остаются неизменными.

В момент времени t6 на выходе D-триггера 5 последующего разряда устанавливается сигнал логической "1", в результате чего на шине 19 также устанавливается сигнал логической "1", который открывает элемент 11 И и через элемент 9 ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент 8 И вновь дает запрет прохождению тактовых сигналов на последующий разряд сигналом логической "1" по второму входу элемента 3 ИЛИ и разрешает прохождение тактовых сигналов через элемент 2 ИЛИ-НЕ сигналом логического "0" по его второму входу. На выходе элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ под воздействием сигнала на шине 19 вновь сформируется сигнал логической "1". Остальные сигналы на выходах элементов в момент времени t6 остаются неизменными.

В момент времени t7 начала четвертого тактового импульса на входе младшего разряда числа В и на входе старшего разряда числа А комбинационного сумматора 7 формируются сигналы логической "1", в результате чего на выходе его младшего разряда устанавливается сигнал логической "1", а на выходе старшего разряда - сигнал логического "0", на выходах инверторов 12 и 13 сформируются противоположные предыдущему состоянию сигналы, диоды 16 и 17 подтверждают выходные состояния сумматора 7, начинается процесс перезаряда конденсатора 4. Остальные сигналы на выходах элементов в момент времени t7 остаются неизменными.

К моменту времени t8 завершится перезаряд конденсатора 4 и на D-входе триггера 5 установится сигнал логической "1", а на D-входе триггера 6 установится сигнал логического "0". В момент t8 на выходе триггера 5 установится сигнал логической "1", а на выходе триггера 6 установится сигнал логического "0". В результате этого на выходе младшего разряда сумматора 7 будет поддерживаться сигнал логической "1", на выходе старшего разряда - сигнал логического "0", на выходе элемента 9 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается сигнал логической "1", на выходе элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается сигнал логического "0". Остальные сигналы на выходах элементов в момент времени t8 остаются неизменными.

В момент времени t9 на входе младшего разряда числа В и старшего разряда числа А сумматора 7 установится сигнал логической "1", в результате этого на обоих выходах сумматора 7 установятся сигналы логического "0", соответственно на выходах инверторов 12 и 13 установятся сигналы логической "1", диоды 16 и 17 смещены в обратном направлении, начинается разряд конденсатора 4. Остальные сигналы на выходах элементов в момент времени t9 остаются неизменными.

В момент времени t10 окончания пятого тактового импульса будет завершен разряд конденсатора 4, и на выходах триггеров 5 и 6 установятся сигналы логического "0", которые будут поддерживать выходные состояния комбинационного сумматора 7 и через элементы 9 ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент 8 И установят запрет прохождению сигнала через элемент 2 ИЛИ-НЕ сигналом логической "1" по второму входу и откроют элемент 3 ИЛИ сигналом логического "0" по второму входу. На выходе элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ вновь установится сигнал логической "1". Остальные сигналы на выходах элементов в момент времени t10 остаются неизменными.

В момент времени t11 на выходе элемента 3 ИЛИ сформируется сигнал логического "0", который по шине 21 поступит на последующий разряд и вызовет изменение выходных состояний сумматора 7, начнется процесс перезаряда конденсатора 4 последующего разряда. Остальные сигналы на выходах элементов в момент времени t11 остаются неизменными.

В момент времени t12 последующий разряд меняет свое состояние по выходам триггеров 5 и 6 на противоположные и на шине 19 устанавливается уровень логического "0", в результате чего все логические элементы установятся в состояния, полностью совпадающие с состояниями, которые они имели перед подачей первого тактового импульса. Дальнейшая работа устройства происходит аналогичным образом.

Рассмотрим функционирование счетного устройства при воздействии помех. Допустим в произвольный момент времени, например, между t2 и t3 (на диаграмме не отражено) под воздействием помехи произошло самопроизвольное переключение триггера 5 в состояние логического "0", а триггера 6 в состояние логической "1", в результате этого, на выходе младшего разряда сумматора 7 установится сигнал логического "0", на выходе старшего - сигнал логической "1". Однако на D-входе триггера 5 с помощью конденсатора 4 будет поддерживаться сигнал логической "1", а на D-входе триггера 6 - сигнал логического "0", что позволит восстановить утраченные состояния триггерам 5 и 6, которые тактируются низким уровнем, присутствующим в этот момент на тактовых входах триггеров. Соответственно на выходе младшего разряда сумматора 7 установится сигнал логической "1", a на выходе его старшего разряда - сигнал логического "0", диоды 16 и 17 с помощью инверторов 12 и 13 будут поддерживать выходные сигналы сумматора 7, начнется подзаряд конденсатора 4, по завершении которого пересчетная схема полностью восстановит свое прежнее состояние.

Таким образом, в отсутствие тактовых сигналов на входной шине 1, помехоустойчивость разрядов счетного устройства обеспечивается за счет определенного заряда на конденсаторе 4, а во время действия каждого тактового сигнала на шине 1, когда тактовые сигналы на D-входах отсутствуют, происходит изменение состояния конденсатора 4 только в одном разряде счетного устройства, следовательно, сбой возможен только в одном разряде, состояние которого характеризуется неким промежуточным значением на конденсаторе 4.

Таким образом, из описания работы следует, что повышение помехоустойчивости счетного устройства достигается за счет введения в пересчетную схему пассивного запоминающего элемента и использования однопеременного кода, при котором в случае совпадения во времени импульса помехи с тактовым сигналом сбой возможен только в одном разряде, поэтому возможная ошибка в этом случае не будет превышать одного периода тактового сигнала, поступающего на входную шину 1.

С целью подтверждения осуществимости заявляемого объекта и достигнутого технического результата был изготовлен и испытан лабораторный макет троичного счетного устройства. Проведенные испытания показали осуществимость устройства и его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237969C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237970C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250558C1 |

| ТРЕХСТАБИЛЬНЫЙ СЧЕТНЫЙ ТРИГГЕР (ВАРИАНТЫ) | 1993 |

|

RU2093955C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ГРУППОВЫХ КОДОВ | 1990 |

|

RU2025049C1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления. Техническим результатом является повышение помехоустойчивости. Указанный технический результат достигается за счет того, что устройство содержит входную шину, элемент ИЛИ-НЕ, элемент ИЛИ, конденсатор, первый и второй D-триггеры, комбинационный сумматор, первый и второй элементы И, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй инверторы, первый, второй и третий резисторы, первый и второй диоды, управляющую шину устройства, управляющую шину предыдущего разряда и выходную шину. 2 ил.

Троичное счетное устройство, содержащее в каждом разряде первый и второй элементы совпадения и трехстабильную пересчетную схему на основе двух D-триггеров, выходы первых элементов совпадения каждого разряда соединены с тактовыми входами трехстабильных пересчетных схем, первые входы первых элементов совпадения соединены с первыми входами вторых элементов совпадения и с выходами вторых элементов совпадения предыдущих разрядов, выход второго элемента совпадения последнего разряда соединен с выходной шиной, отличающееся тем, что в каждый разряд введены первый элемент И, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый элемент совпадения выполнен в виде элемента ИЛИ-НЕ, второй элемент совпадения - в виде элемента ИЛИ, первые входы элемента ИЛИ-НЕ и элемента ИЛИ первого разряда соединены с входной шиной, первый выход трехстабильной пересчетной схемы каждого разряда соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с инверсным входом первого элемента И, второй выход - с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда, а выход - с прямым входом первого элемента И, прямой и инверсный выходы которого соединены соответственно со вторыми входами элементов ИЛИ-НЕ и ИЛИ, второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последнего разряда соединен с управляющей шиной устройства, в трехстабильную пересчетную схему введены второй элемент И, комбинационный двухразрядный сумматор, два инвертора, два диода, три резистора и конденсатор, тактовый вход пересчетной схемы соединен с тактовыми входами первого и второго D-триггеров, с входом младшего разряда числа В комбинационного сумматора и с первым входом второго элемента И, второй вход которого соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с входом старшего разряда числа А комбинационного сумматора, вход младшего разряда числа А соединен с выходом первого D-триггера, вход старшего разряда числа В - с выходом второго D-триггера, выход младшего разряда сумматора соединен с входом первого инвертора и через первый резистор - с D-входом первого D-триггера, выход старшего разряда сумматора соединен с входом второго инвертора и через второй резистор с D-входом второго D-триггера, выход второго инвертора соединен с катодом первого диода, анод которого соединен с D-входом первого D-триггера и через последовательно соединенные третий резистор и конденсатор с D-входом второго D-триггера и с анодом второго диода, катод которого соединен с выходом первого инвертора.

| БУКРЕЕВ Н.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Радио и связь, 1990, с.415 | |||

| Троичное счетное устройство | 1988 |

|

SU1506547A1 |

| Троичный счетный триггер | 1987 |

|

SU1422405A1 |

| Делитель частоты на три | 1986 |

|

SU1354414A1 |

Авторы

Даты

2004-06-27—Публикация

2002-06-21—Подача