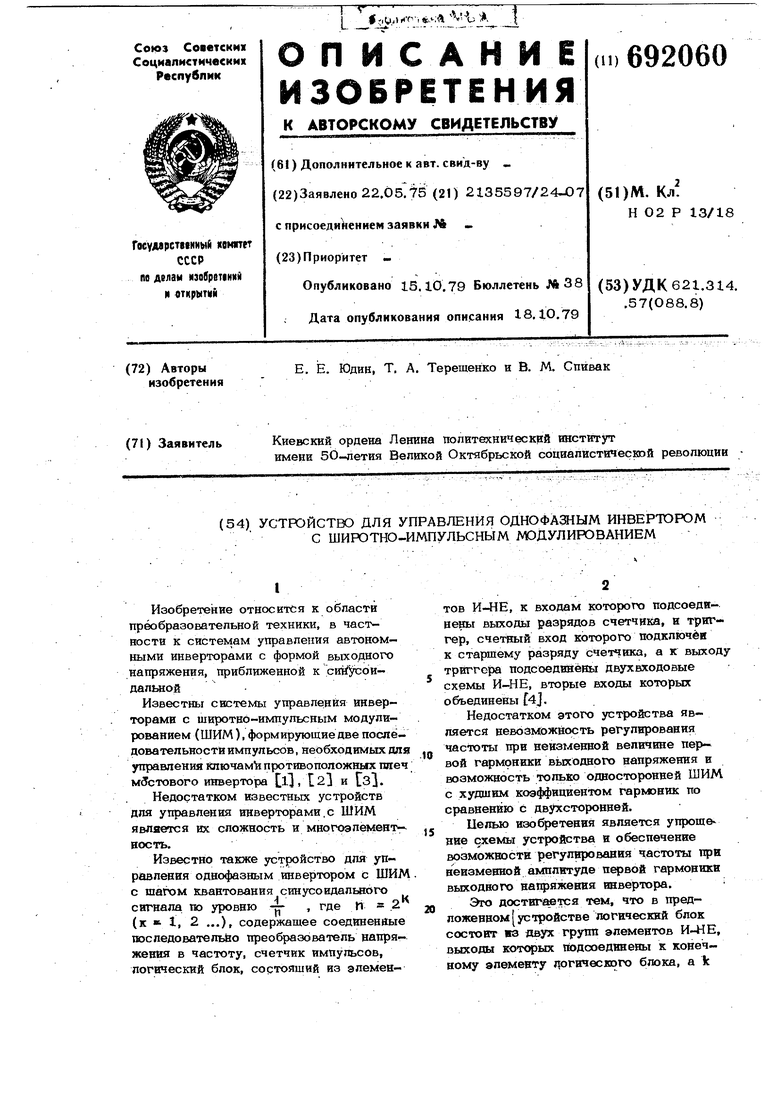

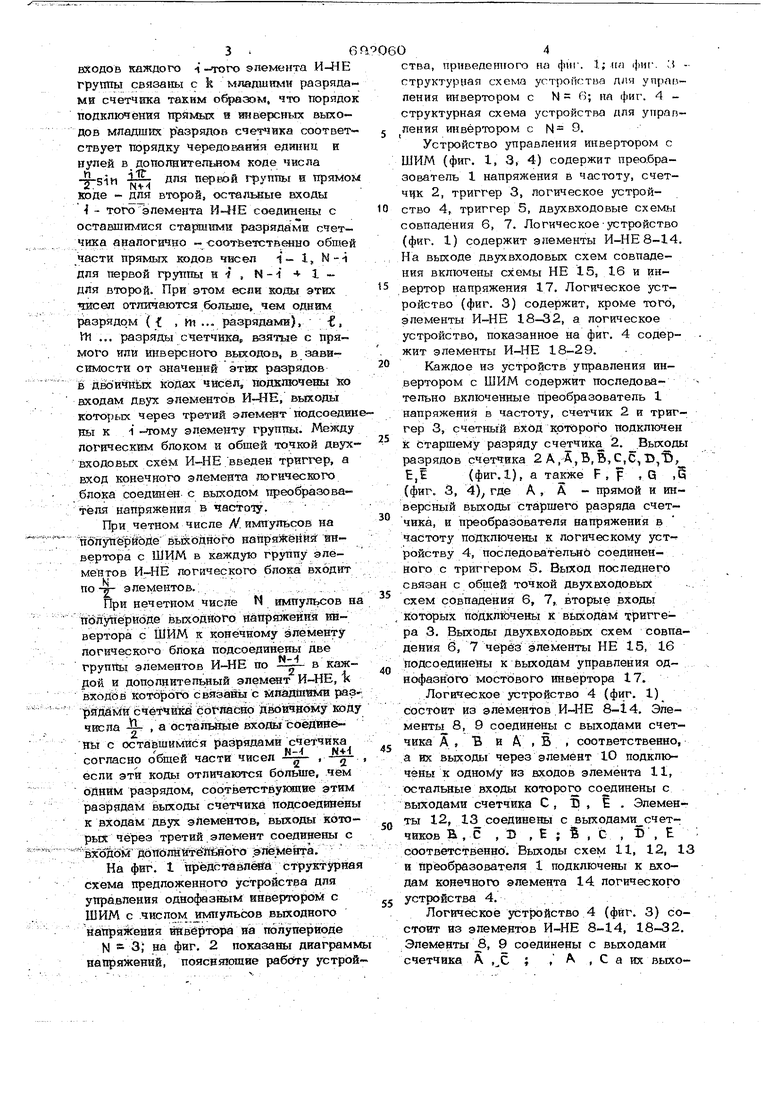

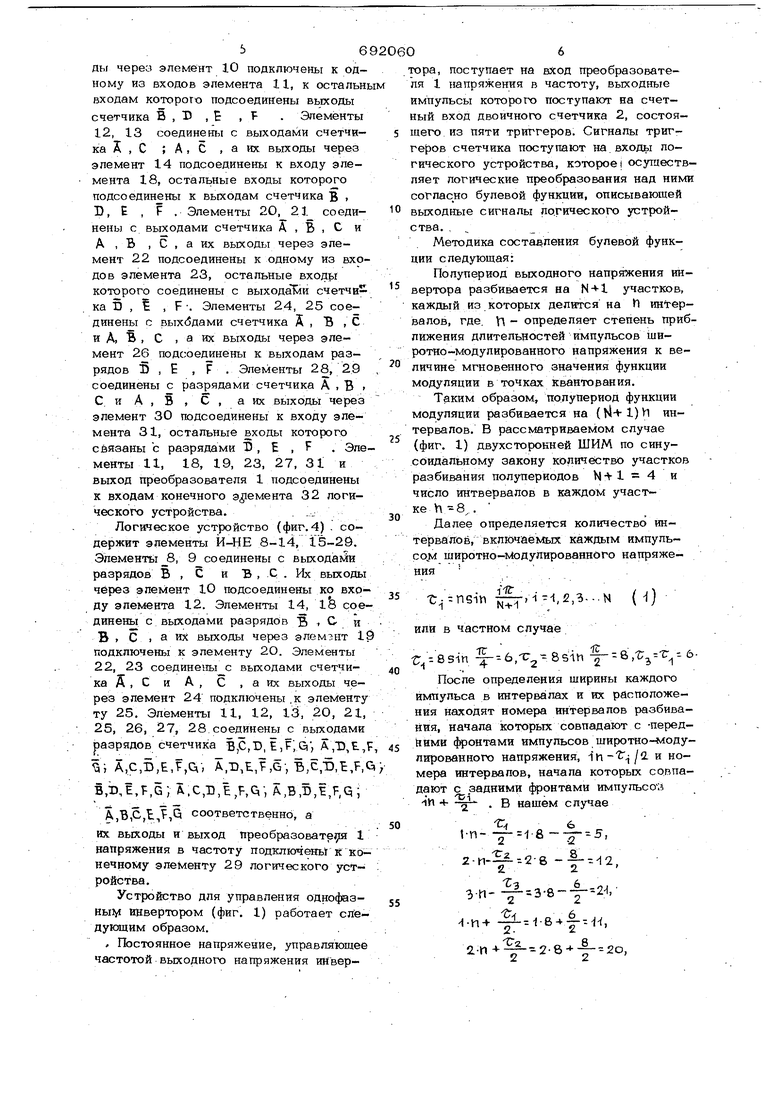

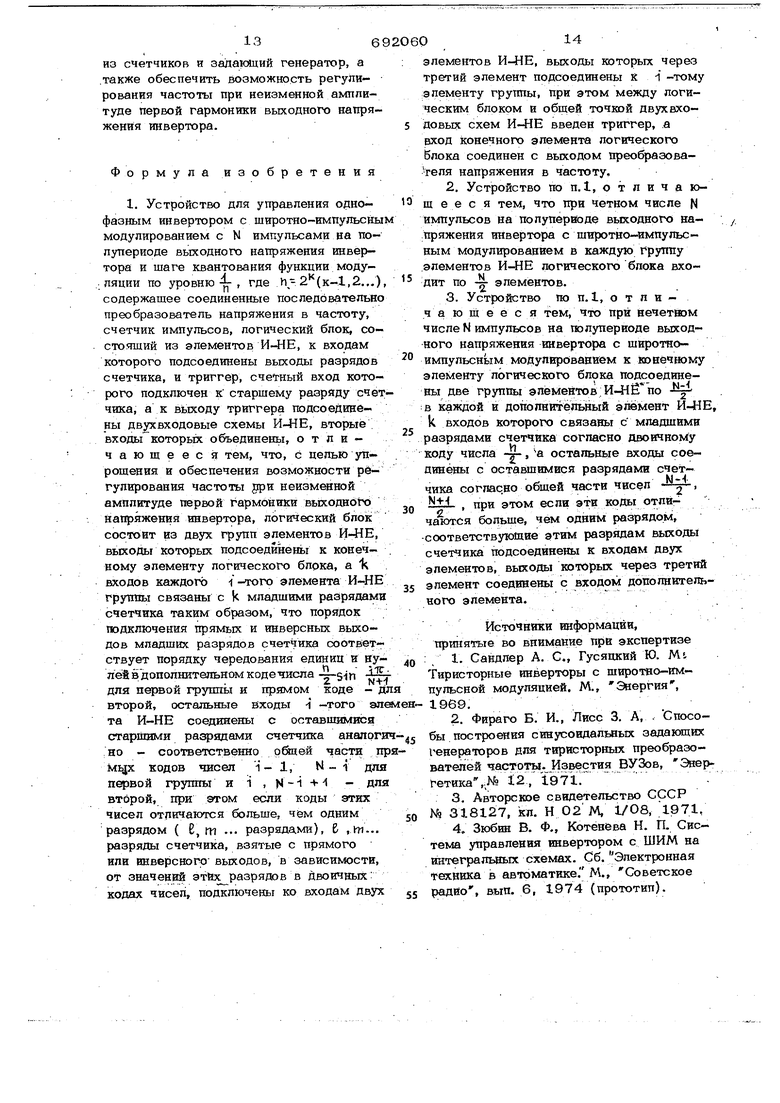

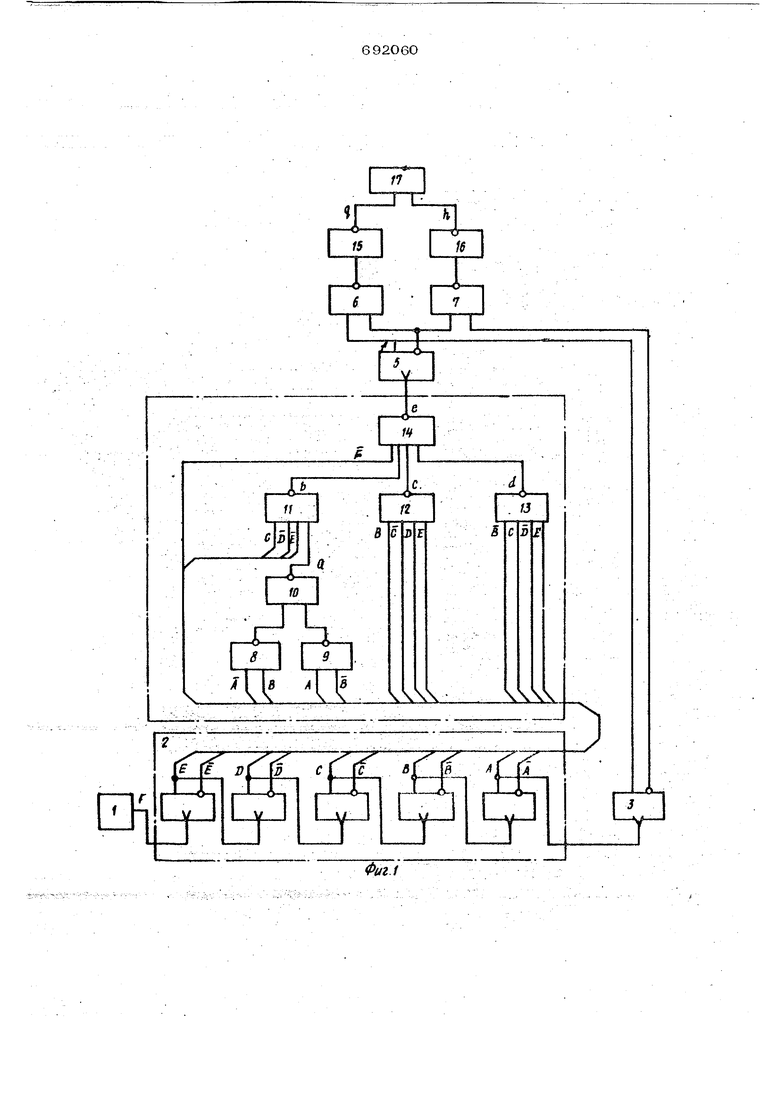

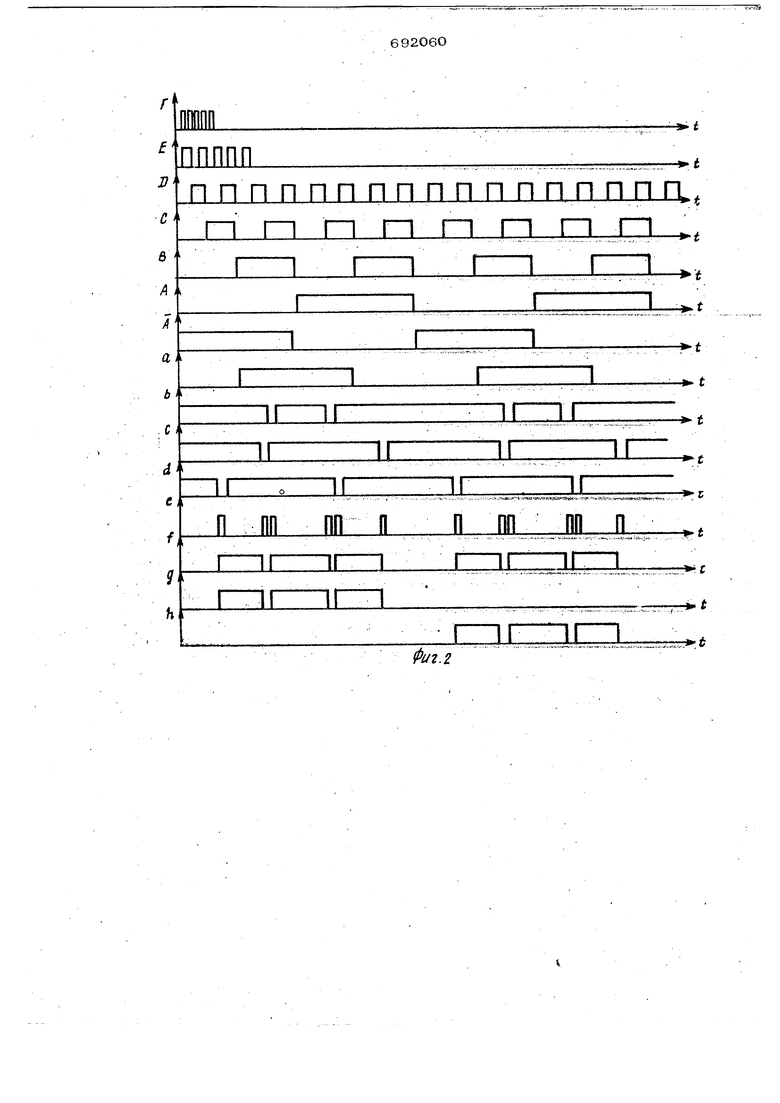

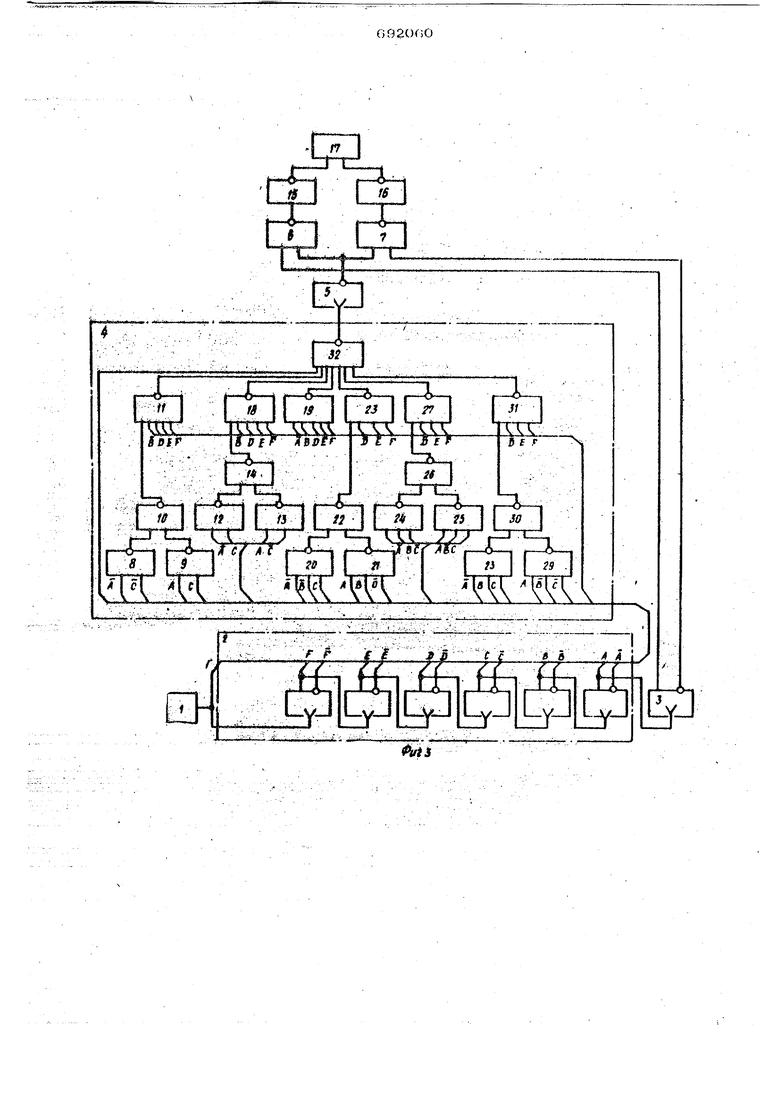

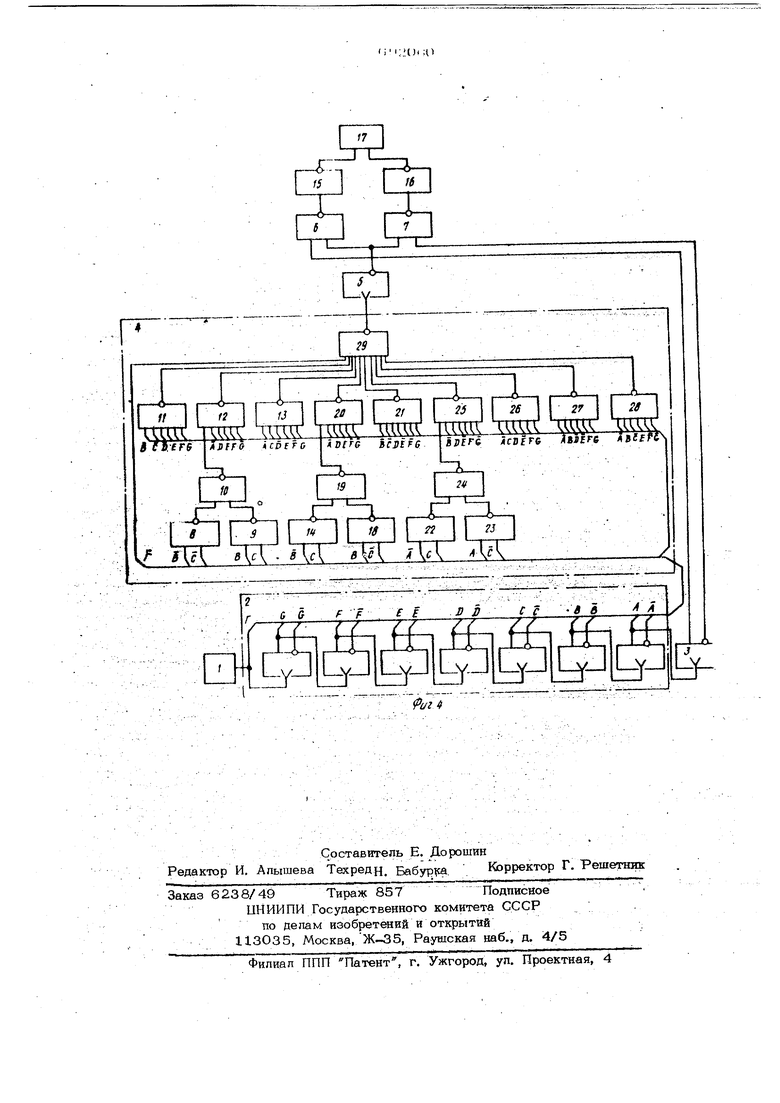

Изобретение относится к области преобразовательной техники, в частности к системам управления автономными инверторами с формой выходного напряжения, приближенной к сийхлсоидальнойИзвестны системы управления инверторами с шнротно-импульсным модулированием (ШИМ), формирующие две посяёдовательностйимпульсов, необходимых дл управления Ключам 1 противоположных пле мЗстового инвертора Ы. 12} и fs}. Недостатком вкзвестных устройств для управления инверторами,с ШИМ является их сложность и многх)элемент ность. Известно также устройство для унравлевия однофазным инвертором с ШИМ с шагом квантования синусоидального сигнала, по уровню -рр , где И -2 (к «ь 1, 2 ...), содержащее соединенйые последоватвльйо преобразователь напряжения в частоту, счетчик импульсов, логический блок, состоящий из элементов И-НЕ, к входам которого подсоеднвены выходы разрядов счетчика, н триггер, счетный вход которого подключён к старщему разряду счетчика, а к выходу триггера подсоедийёвы двухвходовые схемы И-НЕ, вторые входы которых объединены C4j. Недостатком этого устройства яв ляется невозможность регулирования частоты при неизменной величине первой гармоники вькодного напряжения и возможность только односторонней ШИМ с худшЕМ коэффициентом гармоник по сравнению с двухсторонней. Цепью изобретения является упрощение схемы устройства и обеспечение возможности регулировгшия частоты при неизменно и амплитуде первой гармоники выходного напряжения швертора. Это достигоэтся тем, что в предложенном устройстве логический блок состоит ва двух групп элементов И-НЕ, выходы которых подсоединены к конечному элементу | огического блока, а k входов каждого ч-того элемента И-ЛЕ группы связаны с k младшими разряда ми счетчйка таким образом, что порядо подключения прямых @ инверсных выходов младших разрядов счетчика соответ ствует порядку чередевання единиц н нулей в дотюпннтельном коде числа я 4pq Дпя первой группы н прямо коде - для BToiK)fi, остальные входы 4 - того элемента И-НЕ соединены с останшголися старш15Мй разрядамн счетчика аналогично - соответственно общей части прямых кодов чисел 1- 1, N--i для первой rpyttnbj а i , N--i 1 - для второй. При этом еспн коды этнх чисел отличаются больше, чем одним разрядом ( i , щ ... разрядами), €. Ж ... разряды счетчиквр взятые с прямого или инверсного выходов, в ;за.в0 снмости от значеикй этих разрядов JB дюнчнЬсс кодах чжёл, подключены ко входам двух элементов , выходы которых через третий элемент нодсоедин ны к 1 -JTOMy элементу группы. Между логическим блоком и обшей точкой двух входовых схем И-НЕ введен триггер, а вход конечного элемента к гического блока соединен с выходом преобразователя напряжения в часто1у. При четном числе Ж импульсов на пбпуПфйбДе вькоднбго напряжения инвертора с ШНМ в каждую группу элементов И-НЕ логического блока входит по- элементов.; ... ... ., . . При нечетном числе N импульсов н пЬл | ёрйоде вькоДйбГо яамряжейия инвертора с ШЙМ к конечному элементу Логического блока подсоединены Две группы элементов И-НЕ по - В каждои и дополнительный элемент И-НЕ, 1 вхоДЬв Которого связаны с мпадшами раз ||йдййй счётчики cbrnafcHO дбойчзбму коД числа -й- , а остагпйые Bxoffer соединены с оставшимися разрядами счетчика согласно общей части чисел --- . если эти коды отличаются бопыне, чем одним разрядом, соответствукяцие этим раз1р5 дам въткоцы счетчика подсоединены к входам двух элементов, выходы которых через третий .элемент соединены с ВзйздЙй дЙт$олШйгёй1ёнЬЬэ эЛекшнта, На фйг. I прёдс-равл а структурна схема предложенного устройства для управления однофазным инвертором с ШИМ с числом гмпульсов выходного йапряжения ййвёртора на шпупериоде N 3, на фиг. 2 показаны диаграмм напряжений, поясняющие рабсигу устрой ства, приведенпого на фиг. I; ira фш. 3 структурная схема устройства nnvi управления инвертором с N в; на фиг. 4 структурная схема устройства для управления инвертором с N 9. Устройство управления инвертором с ШИМ (фиг. 1, 3, 4) содержит преобразователь 1 напряжения в частоту, счетч к 2, триггер 3, логическое устройство 4, триггер 5, двухвходовые схемы совпадения 6, 7, Логическое-устройство (фиг. 1) содержит элементы И-НЕ 8-14. На выходе двухвходовых схем совпадения включены схемы НЕ 15, 16 и инвертор напряжения 17. Логическое устройство (фиг. 3) содержит, кроме того, элементы И-НЕ 18-32, а логическое устройство, показанное на фиг. 4 содержит элементы И-НЕ 18-29. Каждое из устройств управления инвертором с ШИМ содержит последовательно включенные преобразователь 1 напряжений в частоту, счетчик 2 и триггер 3, счетный вход которого подключен К Старшему ра;зряду счетчика 2. Выходы разрядов счетчйка 2 А, А,Б,Б,С,С, , Е,Ё(фиг.1), а также F , р , Q ,§ (фиг. 3, 4) где А , А - прямой и инверсный выходы старшего разряда счетчика, и преобразователя напряжения в частоту подключены к логическому уст-т ройству 4, последовательнб соединенйого с триггером 5. Выход Последнего связан с общей точкой двухвхоДовых схем совпадения 6, 7,. вторые входы которых ПодклтЬчеНь к выходам триггера 3. Выходы двухвходовых схем совпадения 6, 7 через элементы НЕ 15, 16 подсоединены к быходам управления однофазного мостово Го инвертора 17. Логическое устройство 4 (фиг. 1) состоит из элементов И-НЕ 8-14. Элементь 8, 9 соединень с выходами счетчика А , В и А , Б , соответственно, а их вьрсоды через элемент 1О подключены к одному из входов элемента 11, остальные входы которотх соединены с выходами счетчика С , 5 , 1 . Элементы 12, 13 соединены с выходами счетчиков В , С ,13 , Е J S , С , Т , Е соответственно. Выходь схем 11, 12, 13 и преобразователя 1 подключены к входам конечного элемента 14 логического устройства 4. Логическое уст{эойство 4 (фиг. 3) состоит из элементов И.-НЕ 8-14, 18-32. Элементы 8, 9 соединены с выходами счетчика А ,С ; , А , С а их выхоЬ6ды через элемент 10 подключены к одному из входов элемента II, к остальн входам которого подсоединены выходы счетчика В , Б , Е , F . Элементы 12, 13 соединены с выходами счетчика X , С ; А, С , а их выходы через элемент 14 подсоединены к входу элемента 18, остальные входы которого подсоединены к выходам счетчика В . Б, Е , F . Элементы 20, 21 соединены с выходами счетчика А , В , С- и А , В , С , а их выходы через элемент 22 подсоединены к одному из входов элемента 23, остальные входы которого соединены с выходами счетчи. ка D , t , F . Элементы 24, 25 соединены с выходами счетчика S , В , С и А, S , С , а их выходы через элемент 26 подсоединены к выходам разрядов D , Е , Г . Элементы 2 8, 29 соединены с разрядами счетчика А , В С, и А , В , С , а их выходы через элемент 30 подсоединены к входу элемента 31, остальные входы которого связаны с разрядами D , Е , F . Эле менты 11, 18, 19, 23, 27, 31 и выход преобразователя 1 подсоединены к входам конечного элемента 32 логического устройства.. Ij Логняеское уст ройство (фиг. 4) . содержит элементы Й-НЕ 8-14, 15-29. Элементы 8, 9 соединены с выходами разрядов Б , С и Б , С . Их выходы через элемент 10 подсоединены ко входу элемента 12. Элементы 14, is сое динены с выходами разрядов В i С- и В . С , а их выходы через элемент 1 подключены к элементу 2О. Элементы 22, 23 соединены с выходами счетчикаД,С и А, С ,аих выходы через элемент 24 подключены ,к элементу ту 25. Элементы II, 12, 13, 2О, 21, 25, 26, 27, 28 соединены с выходами разрядов счетчика Б С D E,FCi, А Т) t F 45 , А,С,5,Е,,С.-, A,i;,E,,e- Б,, B,:D,I,F,G; A.c,B,E,f,G,-A,B,D,F,Q; A,B,C,b,,Q соответственно, a их выходы и выход преобразователя I напряжения в частоту подключеньГ к конечному элементу 29 логического устройства. Устройство для управления однофазным инвертором (фиг. 1) работает следующим образом.. ГЪстоянное напряжение, управляющее частотой выходного напряжения инвер5055 6 тора, поступает на вход преобразователя 1 напряжения в частоту, выходные импульсы которого поступают на счетный вход двоичного счетчика 2, состояшего из пяти триггеров. Сигналы триггеров счетчика поступают на.входь логического устройства, которое осуществляет логические преобразования над ними согласно булевой функции, описывающей выходные сигналы логического устройства. , Методика составления булевой функции следующая: Полупериод выходного напряжения инвертора разбивается на N-+-1 участков, каждый из которых делится на Я интервалов, где. Y - определяет степень приближения длительностей импульсов ши- ротно-модулированного напряжения к величине мгновенного значения функции модуляции в точках квантования. Таким образом, полупериод функции модуляции разбивается на ()11 интервалов, В рассматриваемом случае (фиг. 1) двухсторонней ШИМ по синусоидальному закону количество участков разбивания полупериодов N-vl 4 и число интвервалов в каждом участке h 8. Далее определяется количество интервалов, вклйчаёмых каждым импульсо 1 широтно-Модулированного напряжения . ,1-.с.з.-.м () t.-nsivi или в частном случае ;--8sin --6,C2-8sin --Q,t,--- --bПосле определения ширины каждого импульса в интервалах и их расположения находят номера интервалов разбивания, начала которых совпадают с -перед фронтами импульсов широтно-моду «- «-- напряжения, 1.-Г,/а и номера интервалов, начала которых совпадают с задними фронтами импульсо-; чи 4- - . в нашем случае , 2-и- --2-в --|--И2, -1 и Ll-.-i. 2 - 2 -|i- - -6- |--H-f, 2-П- - -2-в- --20,

3.у,ч12.,з.8 - -|---27. Затем составляется логическая функ- дня, опйсывакяпая периодическое импуиьс йоё йагфяжение, которое равно едййине J3 йй ёрбйпах, с Нбмерами, ойреяёленным Ъ поряйке возрастания и равно нулю Q остальных ннтервапах: -IlVtij, где аомера интервалов в nopsyi te воарастаf-his- vn -m j- m o m vn -, (2 Функция m J представляет собой погн ческое произведенйге выходных сигнаяов счётчика, взятых с тфямбго или инверсного выхода каждого , начиная со CTapmetxt, в той же последовате1льно стн, что и единицы и нулк соответственяо в. двончных кодах чвсеп П . lit . и . itl 1-п--sin-j и 1ЧИ--sihV -i .;.. NJ., ; S нашем случае . ABCSE-s-ABCDE- АЪСБЫ.-4SbC5E-+ABC5E-t-ABCDE. . После Минимизации методами булевой алгебры функция имеет вид jf верь cSi СД.) ипа в базисе операций И-НЕ f (ВСВЕ)СВС5Е)СТ5ЁСАВХАВ): 5 Возможно формализовать мшймизацшо функции (2), т.е. составление связ между элементами Й41Е логического блока сдедукяцее. Число разрядов водов чисел Т должно быть одинаковым, а именно равным togr -CK-i-OVi. При ( (KS 1,2...) tog-(Кч-f) и - (Н EOgg «7 где .og,jCN-H) , .fL... , TaKKaK Sit, доста- то для aatracpf кода S1 точно К разрядов.

Toraafn- - JTn КН 4..(o2°Cl-, Так как в записи mj должны участвовать все разряды счетчика, число i следует записать с 11|омощью разрядов (если для записи i нужно меньше, чем 6 разрядов, старпуие разряды приравниваются О) Таким образом tt4.- l-s-ivi rb 2 +fi -2n g b-in De-2 -.a,.:,.,,.. ..Ъ„2 ..... bb,,2 --va...c,2° .Сл едо1ватеп ьно: (Ье-Л-2 o } -i -2 -/ДЙОИЧН Cl-,2...NX де .. e- Е,-2--- числа -t) кн «к-2--«о ° числа -|1-. налогично можно показать, что С„ С - ... С., - прямой код B- -2 о числа 1-tj d г1rJ дополнитепь- ный . Логическая функция (2) минимизнруется методами булевой алгебры с уче том равенств/. з;1;Ж. „.,,„ iblt,s,i . Уго означает, что младшнх разряов в кодах, соответствующих передним (задним) фронтам нмЪупьсов Hanpsoke- НИН- с lUHJvC равноотдапенных от , .одинаковы. Если к тому же, воды чисел 1-1, N-i ( i , N--1 I) отличаю ся лишь одним разрядом; вместо суммы j Л можно записать общую часть этих кодов ( U.J ).

I-сJill коды отличаются vn разрядами, us |;умму можно представить как t.-v e-ni -i e-ni-2 -m-(€-ni-a K-- . е-п1-2 o beM-: e-niH t-i e-w-( e-tn2 o t H -«o e-f- e-ni-i I ИЛИ в общем иде . Следовательно, функция будет иметь слагаемые виды U f--U ,-K V Второе слагаемое реализуется следующим образом: два элемента И-НЕ, соединенные с 5 ... € о Ш выходами счет чика согласно кодам Ь. ....Ь. .„ .и В . -л . « А-1t 9-ги- через элемент И-НЪ подаются на вход элемента, к остальНь1М входам которого подключены остальные разряды счетчика согласно обшей части двух кодов b.j.- oOK-f 9оПри нечетном числе N импульсов появляются еще два слагаемых tn , соответствующие переднему и заднему фронтами среднего - импульса. При этом , младших разрядо представляют собой код числа §- , а 2 старших - двоичный код чисел М и И соответственно. Операции с этими кодами производят аналогично. Общий вид f при этом не изменяется. Из всего сказанного можно сделать вывод: к конечному элементу И-НЕ логического блока в общем виде подсоединяются две группы элементов И-НЕ первая вырабатывает импульсы, совпадакнцие с передним фронтами импульсов выходного напряжения инвертора с ШИМ При этом k входов элементов И-НЕ пер вой rpymibi соединены с k младшими разрядами счетчика таким образом что порядок подключения прямЕлх и инверсны выходов -счетчика соответствует ПООЯПКУ

чередования единиц и нулей в двоичном де ( .5 ),т.е. допол2 Sin . Младших читепьном коде числа разрядов второй группы, вырабатывающей импульсы, совпадающие с задними фронтами импульсов выходного напряжения инвертора с ШИМ, соединяются анало ичнокоду С1. d.2-. do (f) т.е. прямому коду числа Оставшиеся старщие разряды счетчика подключаются к i -тому элементу каждой группы согласно обшей части двоичных кодов чисел аналогично i - 1, N-i для первой группы и i , N-i-y для второй (6). Если коды этих чисел отличаются больще, чел одним разрядом, выходы счетчика, соответствующие этим разрядам, подключаются к двугл элементам И-НЕ, выходь которых через третий элемент И-НЕ подключатся к одному из входов -i элемента. При нечетном числе импульсов на поЛупериоде выходного напряжения инвертора с ШИМ к конечному элементу погического стройства подключается дополнительный элемент, реализующий гт -г.ъ TTVi rt ty«««« « гК ль tr/ ЛГ4ТТ .импульсы, совпадаюшие с передним и задним фронтом среднего - импульса. При этом k младших разрядов счет- к этому элементу чшса подключаются h согласно коду - , а старшие согласно кодам чисел J и . В нашем случае (фиг. 1) к конечному элементу 14 логического блока подключены первая группа элементов И-НЕ (13 элемент), вторая (12) и дополнительный элемент 11. Три входа элемента 13 соединяются с выходами счетчика С , Ё Е согласно дотюлнвтельному коду числа .оп. Три входа элемента 14 соединяются с выходами счетчика 13 Е согласно прямому коду числа 3 ОН. Старшие разряды счетчика подключаются к элементу первой группы 13 согласно общей части кодов 1-1 , N-l (0,2) т.е. ОО и 1О. Следовательно мо входу Iэлемента 13 подключается В. Аналогично к элементу 12 подключаются старшие разряды, в зависимости от обшей части кода чисел 1, 3, т.е. 01 11, - I. Следовательно подключается выход счетчика В. 1169 Допопнитепьный .элемент 11 связан младшими разрядами с выходами СDE (100 - 4), а старшими - с выхо дом элемента 10, реализующего функцию (АВ АВ). так как (J ,-) Ф (01,10). 2. Соединение эпементов И-НЕ поги ческого блока, соответствует поспедо ватепьности операций И-НЕ минимизиро ванной булевой функции (3), опнсываюшей вь1ходйое напряжение логического бйойа. Сигналы счетчика 2 А,В и Л, В (фиг. 2) поступают на схемь И-НВ 8,9, сШйсОЯов последних. - на схему 10, которая формирует импульсы, вид которых показан на диаграмме а. СиГнагы счетчика 2 побтупают также на логические элементы 12, 13, форма им It/ntcoB на выходах KOTbpbix преде тавпена на диаграммах с, d Импульсы с вькода схемы Ю (диаграмма а) и сигааль С , 5 , I Поступают на вход элемента 11, осушёствляюшего логическую операцию И-НЁ над входвьгмй сигналами. Импульсы, с выхода элемента 11 (диаграмма Ь) поступают на схему 14. На вход схемы 14 поступают такж и:ШуПьсы с выхода преобразователя ва пряжения в частоту (диаграмма Г). Они создают паузу между соседними импульсами с выхода логического устройства 4 с номерами интервалов i ,, тик как 1ЙХ длительность в два раза меньше длительности интервалов разбивания попупе)иода синусоидального сигнала. Импульсы с выхода элемента 14 (диаграм ма а) подаются на счетиь1й вход триггера 5, который фо{5Мйруе Ыпульсы 1ПИ(рМШййодулированного ю синусоидапь Ному закону напряжения (диаграмма ) С выхода триггера 5 поспедователь -.--- -....л,: :,-S. -i iBtsctVeMnynbcoB при помощи схем совпадения 6, 7 и триггера 3 преобразуетс в виде рспедовательности, несводимые /для управления аЕ.тономным инвертором 1 Формы напряжений с вьгходр в схем 15, Ь 1ёдставлены на диаграммах и li . ЙзМ1енением напряжения на входе пре образоватепя I напряжения в частоту регулируют частоту счетньпс импульсов счетчика 2 и, в конечном счете, часто Fy BfiSOflHotx) напряжения инвертора. При этом амплитуд апервой гйрмоники этого натч яжения остается неизменной, так кй п|ЙйОрцШналы5Ь изменению частоты импульсов Г будут измевяться длительност импульсов широтно-адодулированного натфяжёнйя инвертора. Схемы устройств управления (фиг. 3,4) инверторов отличаются лишь работой ло- гвяеского устройства. Логическое устройство применительно к ШИМ с шестью импульсами на полупериоде выходного напряжения инвертора (фиг.З) осуществляет над выходными сигналами счетчика булевую функцию, составленную.по методике: BTlEFCAC- ACb - ;B13EF(AC4AC)4A3CT)F. ()SE (ABCtAUC + + T)EF(SBC-v-ABC. При этом первое слагаемое мод;епируется элементами 8, 9. Ю, JLJL также, КИК модепируется слагаемое CDЕ( в функции, описывающий сигналы логического устройства на фиг. 1 (см. ди- аграммы а, Ь), Аналогично моделируются остальные слагаемые функции, кроме третьего. Третье слагаемое моделируется элементом 19. Логическое устройство управления инвертора с дебятыо импульсами на, толупериоде (фиг.4) описывается функцией вида: i BCT)EFG-f ADtFQ ) В Gi- ATlt Q (BC-t ВС) §c5t PQ- 4bT QCAC- AC)-v -ЬДС5tPG.- S-BCБ G . Второе, четвертое и шесггое слагаемы йодёШрукУгся группами элементов 8 11, 12, 14, 18-20, 22-25 соответственно, а остальные слагаемые элементами 11, 13, 21, 26, 27, 28. Введение и устройство управления инёёртор Ом между логическим устройством и общей точкойДвух входобых схем совйадёНйя триггера, подсое)1Инение выхода преобразбватёйя В1ап яжения в частоту к входу конечйого элемента И-НЕ логического устройства, а тйкже соединение элементов H-4iE последнего в соответствий с операдиями И-НЕ минимизиро- л 1ванной булевой функции, описывакшей выходные сигналы логического устройства, гюэвОШяет упростить схему устройCTjaa управпетйя, исключив из нее один из счетчиков и задакяций генератор, а .также обеспечить возможность регулирования частоты при неизменной амплитуде первой гармоники выходного напряжения инвертора. Формула изобретения 1. Устройство для управления однофазным инвертором с широтно-импульсны модулированием с N импульсами на попупериоде выходного напряжения инвертора и шаге квантования функции модуляции по уровню-, где (к-1,2.,,) содержащее соединенные последовательно преобразователь напряжения в частоту, счетчик импульсов, логический блок, состоящий из элементов И-ЛЕ, к входам которого подсоединены выходы разрядов счетчика, и триггер, счетный вход которого подключен к старщему разряду счет чика, а к вьссоду триггера подсоединены двухвходовые схемы И-НЕ, вторые входы которьгх объединеньг, отличающееся тем, что, с цепью упрощения и обеспечения возможности регулирования частоты 5ри неизменной амплитуде первой гармоники выходнотх напряжения инвертора, логический блок состоит из двух групп элементов И-41Е, выходы которых подсоедйнень к конечному элементу логического блока, а k входов каждого -i-того элемента И-НЕ группы связаны с k младшими разрядами счетчика таким образом, что порядок подключения прямых и инверсных выходов младших разрядов счетчика соответствует порядку чередования единиц и нуrs-i if лей в допопнитепьном коде числа для первой группы и прямом коде - д второй, остальные входы -i -того эл та И-НЕ соединены с оставшзямися сзтаршими разрядами счетчика анапрги но - соответственно рйц ей части пр кодов чисел 1-1, N- I для первой группы и i , )Ц - i -И - для второй, при этом если коды этих чисел отличаются больше, чем одним разрядом ( В, tn ... разряда.ми), 6 ,№-.. разряды счетчика, взятые с прямого или инверсного выходов, в зависикюсти, от значений этих разрядов в двоичных: кодах чисел, подключены ко входам двух 6 14 элементов И-НЕ, выходы которых через третий элемент подсоединены к i -тому :Элементу группы, при этом между логическим блоком и общей точкой двухвходовых схем И-НЕ введен триггер, .а вход конечного элемента логического Впока соединен с выходом преобразовагеля напряжения в частоту, 2, Устройство по п. 1, о т л и ч а ющ е е с я тем, что при четном числе N импульсов на полуперводе выходного напряжения инвертора с широтно-импульсным модулированием в каждую Группу элементов И-НЕ логического блока входит по -- элементов. 3. Устройство по п. 1, о т п и ч а ю П1 е е с я тем, что при нечетном числе N импульсов на голупериоде выходного напряжения инвертора с широтноимпульсным модулированием к конечному элементу логического блока подсоединены две группы элементов: И-НЁ по в каждой и допопнитёпьный элемент И-НЕ, k входов которого связаны с младщими разрядами счетчика согласно двоичному коду числа -и остальные входы соединены с оставшимися разрядами счетчика сргпас.но обшей части чисел 2 при этом если эти коды от лйчаются больше, чем одним разрядом, соответствующие этим разрядам выходы счетчика подсоединены к входам двух элементов, выходы которых через третий элемент соединены с входом дополнительного элемента, Источники информации, принятые во внимание при экспертизе I. Сандпер А. С., Гусяпкий Ю. Ms. Тиристорные инверторы с широтно-импульсной модуляцией. М., Энергия, 1969. 2.Фираго Б. И., Лисе 3, А, Способы построения синусоидальных задающих генераторов для тиристорных преобразователей частоты. Известия ВУЗов, Эшр етика%,,№ i2, Г971. 3.Авторское свидетельство СССР N9 318127, кп. Н 02 М, 1/О8, l971, 4.Зюбин В. Ф., Котенева Н. П. Система управления инвертором с ШИМ на штегральных схемах. Сб. Электронная техника в автоматике. М., Советское радио , вып. 6, 1974 (прототип).

яъ

IF

171 D С

L±(

Фиг. п п п п п п п п п п гп п п п гп

в

г L

J1

г Л

п п п п п п ГУ гп п m

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство управления трехфазным мостовым инвертором | 1985 |

|

SU1312740A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1385294A1 |

| Устройство для управления инвертором | 1990 |

|

SU1709482A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1728968A1 |

| Устройство для управления 3-фазным инвертором | 1979 |

|

SU1039014A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1983 |

|

SU1144174A1 |

| ЦИФРОВОЙ СЧЕТЧИК ЭЛЕКТРОЭНЕРГИИ КСР-ТИПА | 1991 |

|

RU2061243C1 |

| Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное | 1981 |

|

SU991564A2 |

| Устройство для управления тиристорным инвертором | 1986 |

|

SU1418873A1 |

a

и 11 П ПП nn п

ILJi

t

Я

rtrs-i

Йуг. .. , -.--v,.Ar.-i - trcSi e b H; i|Saf 5tp«-i,.---T i:r.-.JDП чтгщ

j f Sfre лхлггъ tcDfFi

егз

к Ef

Авторы

Даты

1979-10-15—Публикация

1975-05-22—Подача