1

Изобретение относится к вычислительной и измерительной технике и может быть использовано при постров НИИ следящих систем.

Целью изобретения является расшире- ние динамического диапазона преобразо- вяния за счет формирования кода старших разрядов путем определения количества переходов входного сигнала за пределы групп эталонных уровней с учетом направления зтих переходов.

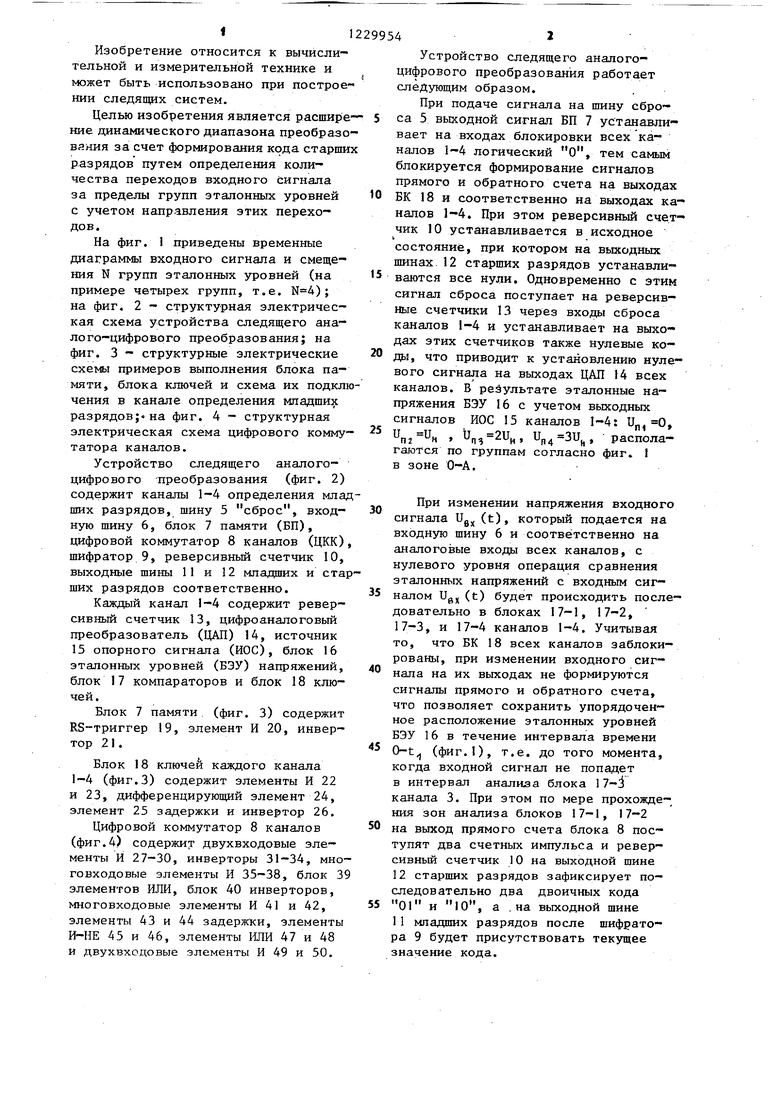

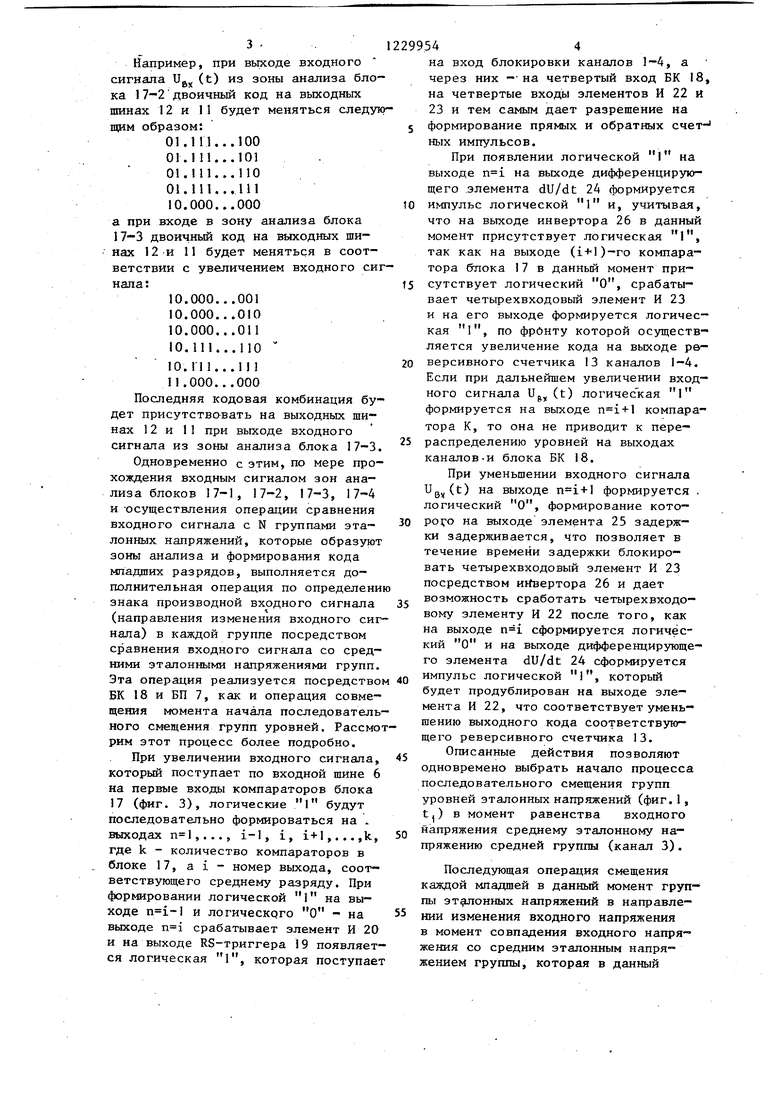

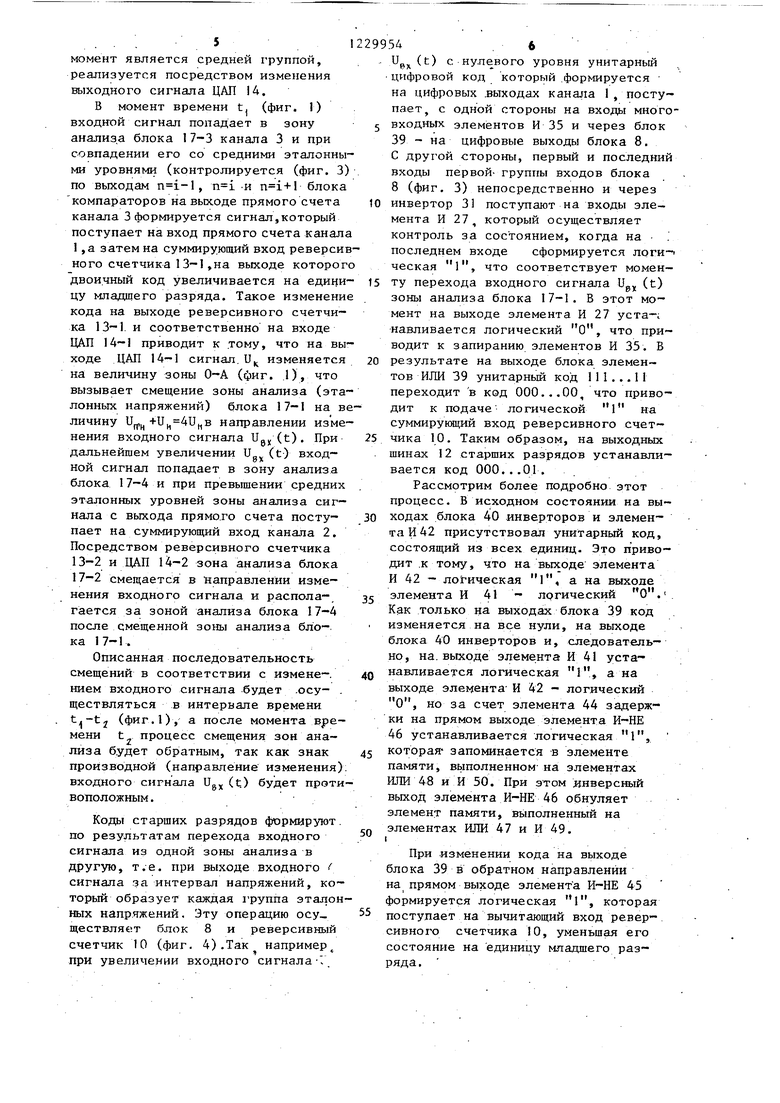

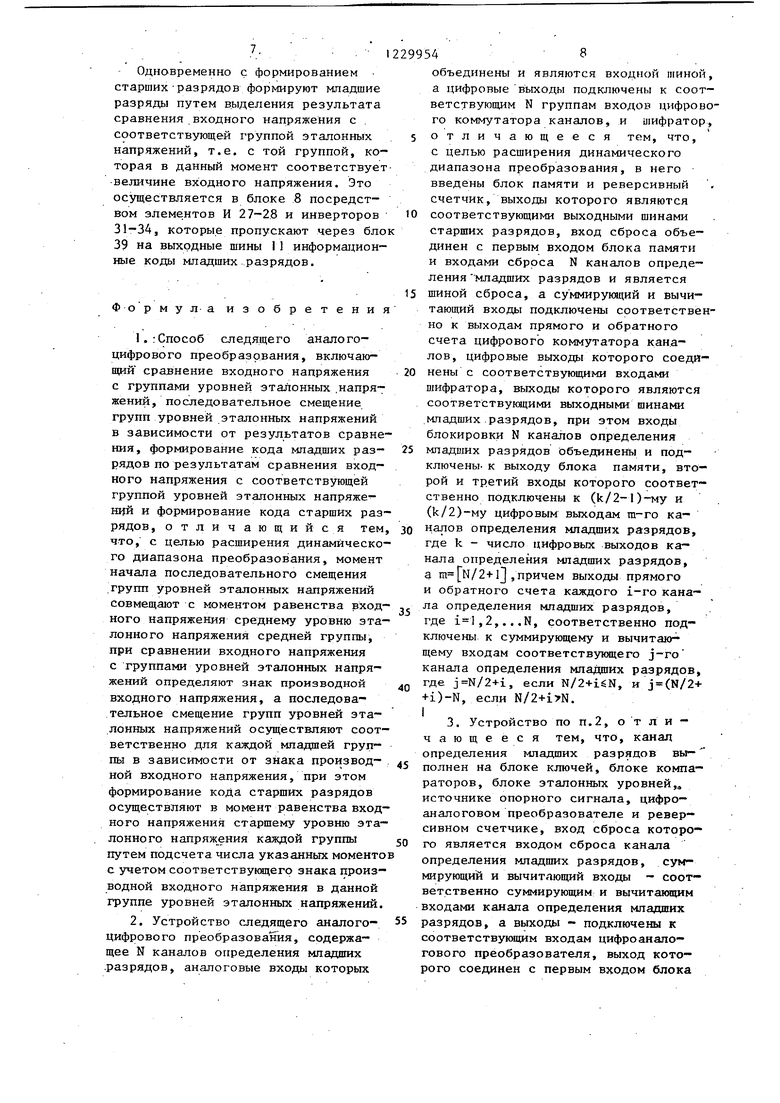

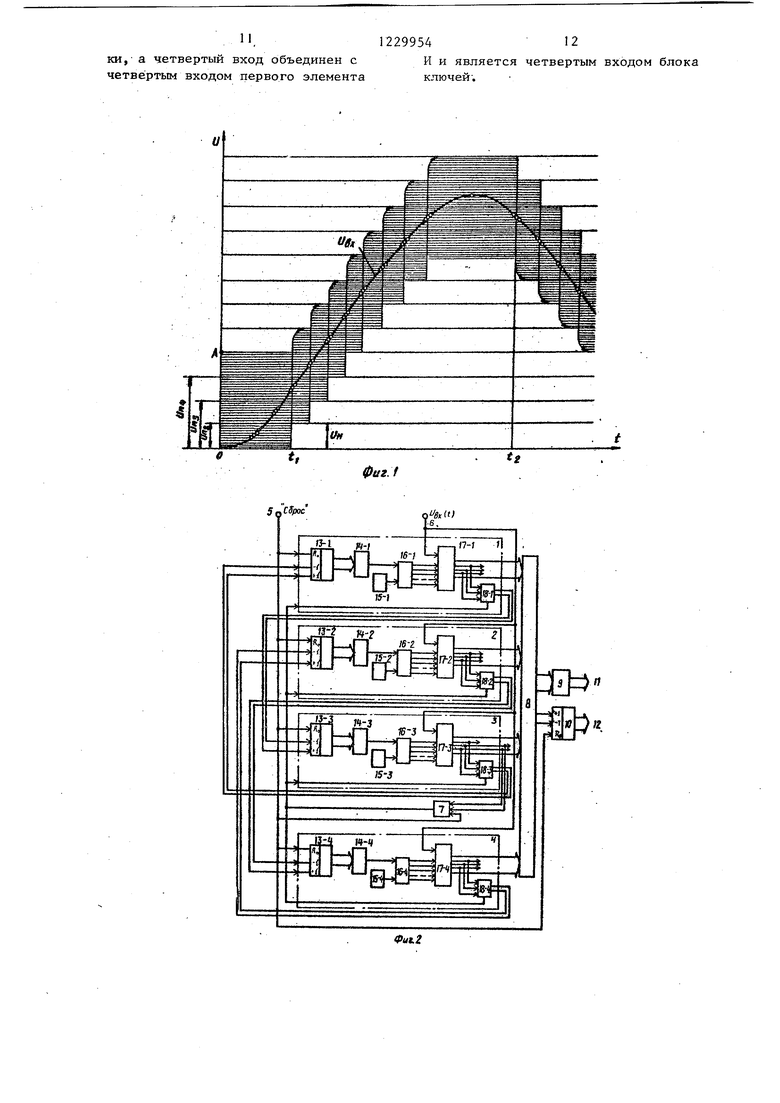

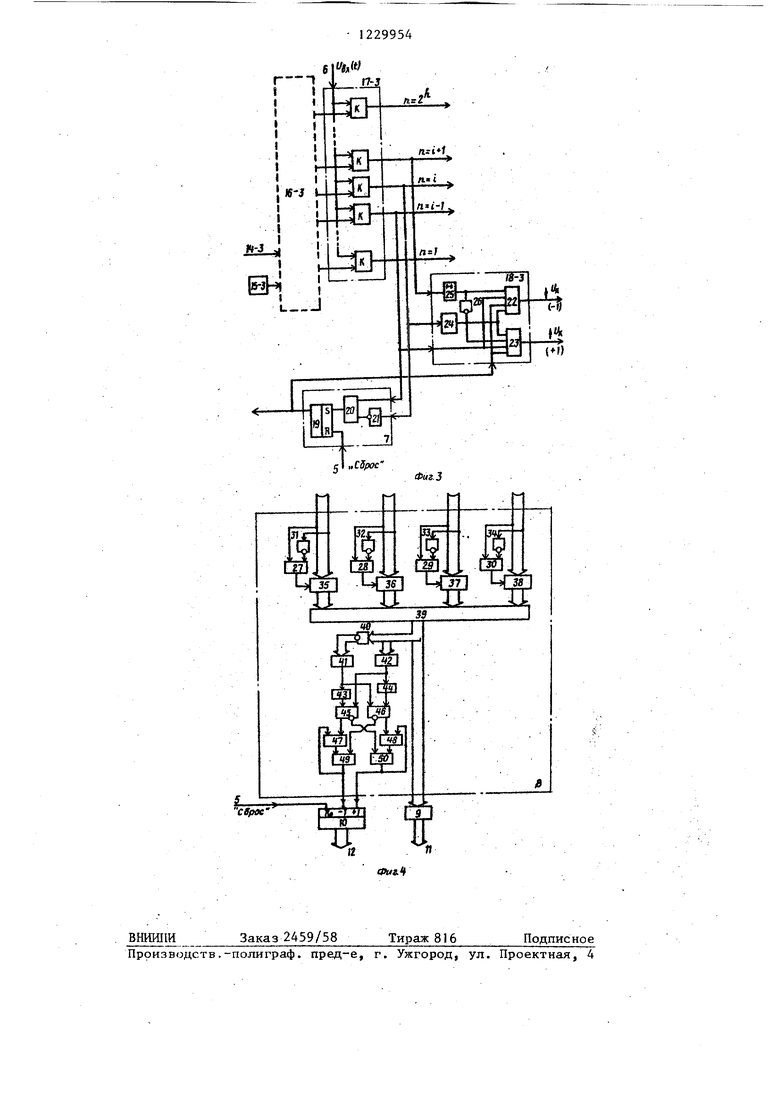

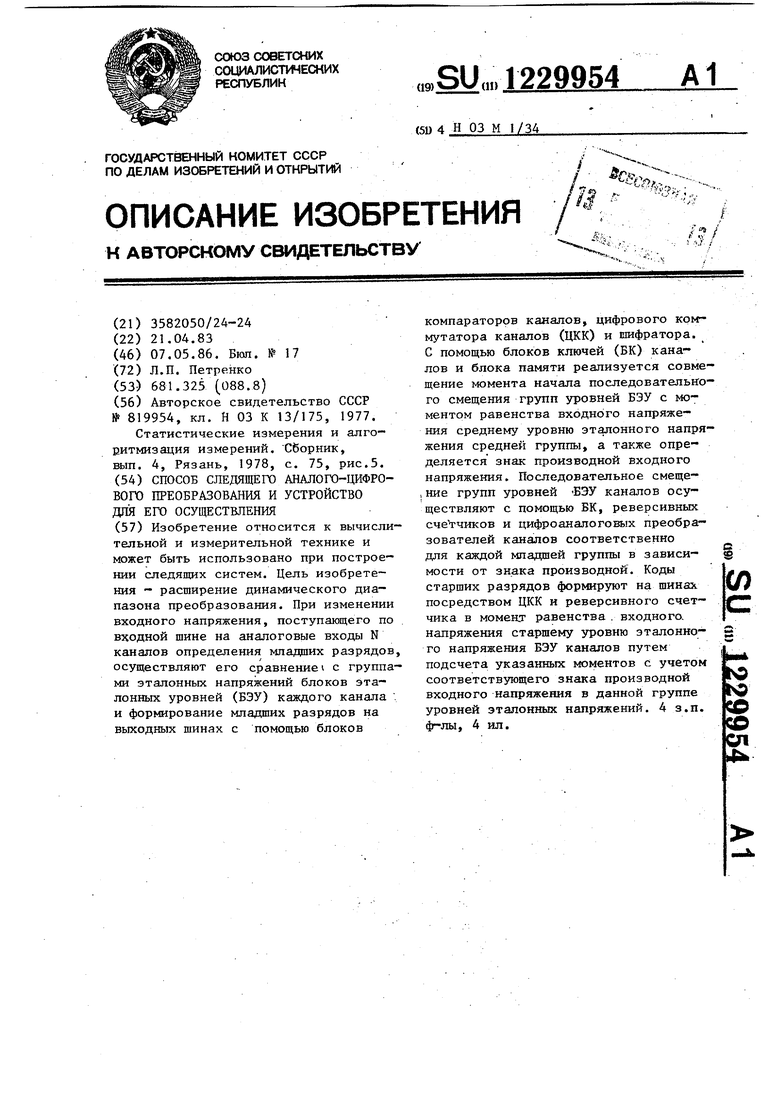

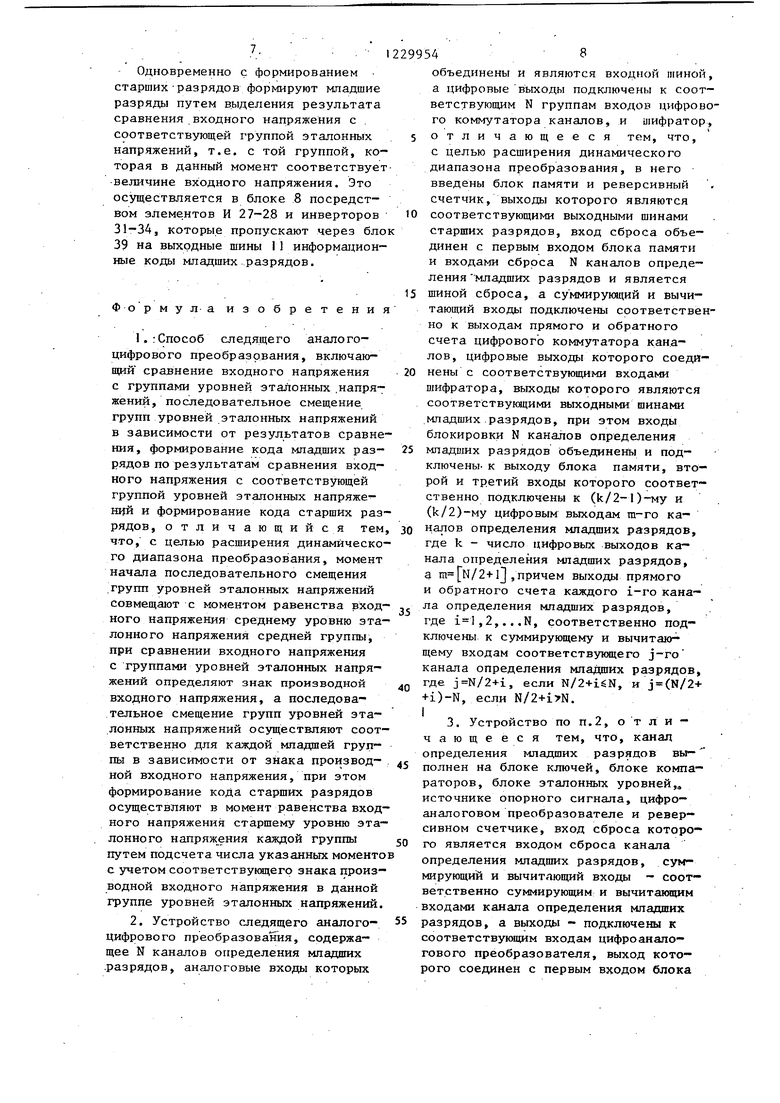

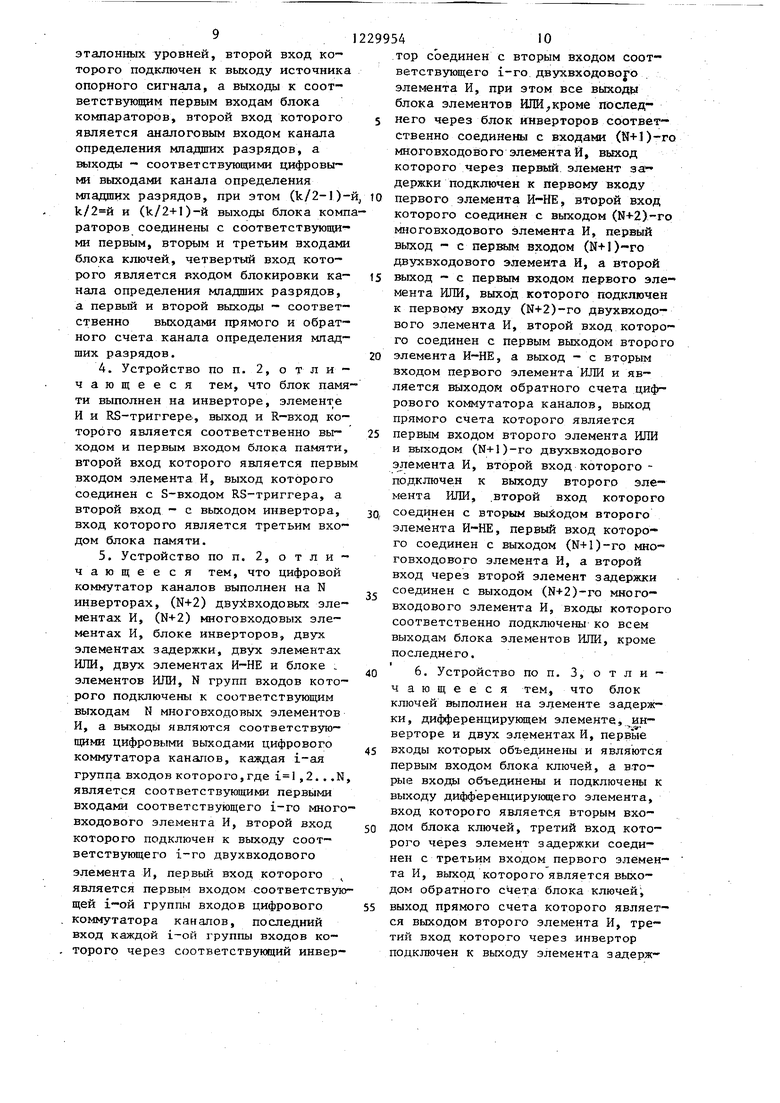

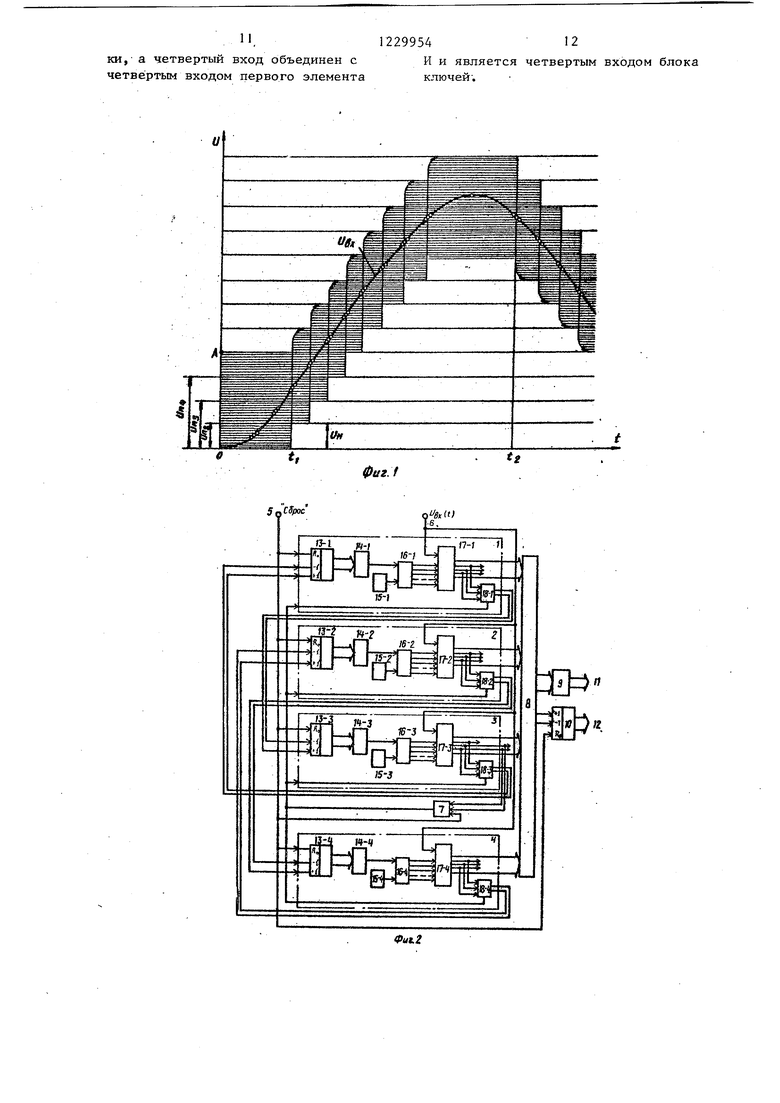

На фиг. 1 приведены временные диаграммы входного сигнала и смещения N групп эталонных уровней (на примере четырех групп, т.е. ); на фиг. 2 - структурная электрическая схема устройства следящего аналого-цифрового преобразования; на фиг. 3 - структурные электрические схемы примеров выполнения блока памяти, блока ключей и схема их подключения в канале определения младших разрядов;« на фиг. 4 - структурная электрическая схема цифрового коммутатора каналов.

Устройство следящего аналого- цифрового преобразования (фиг. 2) содержит каналы 1-4 определения младших разрядов, шину 5 сброс, входную шину 6, блок 7 памяти (БП), цифровой коммутатор 8 каналов (ЦКК), шифратор 9, реверсивный счетчик 10, выходные шины 11 и 12 младших и старших разрядов соответственно.

Каждый канал 1-4 содержит реверсивный счетчик 13, цифроаналоговый преобразователь (ЦАП) 14, источник 15 опорного сигнала (ИОС), блок 16 эталонных уровней (БЭУ) напряжений, блок 17 компараторов и блок 18 ключей.

Блок 7 памяти (фиг. 3) содержит RS-триггер 19, элемент И 20, инвертор 21.

Блок 18 ключей каждого канала 1-4 (фиг.З) содержит элементы И 22 и 23, дифференцирующий элемент 24, элемент 25 задержки и инвертор 26.

Цифровой коммутатор 8 каналов (фиг.4) содержит двухвходовые элементы И 27-30, инверторы 31-34, много входовые элементы И 35-38, блок 39 элементов ИЛИ, блок 40 инверторов, многовходовые элементы И 41 и 42, элементы 43 и 44 задержки, элементы И-НЕ 45 и 46, элементы ИЛИ 47 и 48 и двухвходовые элементы И 49 и 50.

5 0

5

Устройство следящего аналого- цифрового преобразования работает следующим образом.

При подаче сигнала на шину сброса 5 выходной сигнал БП 7 устанавливает на входах блокировки всех каналов 1-4 логический О, тем самым блокируется формирование сигналов прямого и обратного счета на выходах БК 18 и соответственно на выходах каналов 1-4. При этом реверсивный счетчик 10 устанавливается в исходное состояние, при котором на выходных шинах 12 старших разрядов устанавливаются все нули. Одновременно с этим сигнал сброса поступает на реверсивные счетчики 13 через входы сброса каналов 1-4 и устанавливает на выходах этих счетчиков также нулевые коды, что приводит к установлению нуле- вого сигнала на выходах ЦАП 14 всех каналов. В результате эталонные напряжения БЭУ 16 с учетом выходных сигналов ИОС 15 каналов 1-4: U 0,

UH.UH

. ,.

и„.зи,.

располагаются по группам согласно фиг. 1 в зоне 0-А.

При изменении напряжения входного сигнала Ug (t), который подается на входную шину 6 и соответственно на аналоговые входы всех каналов, с нулевого уровня операция сравнения эталонных напряжений с входным сигналом Ugj(t) будет происходить последовательно в блоках 17-1, 17-2, 17-3, и 17-4 каналов 1-4. Учитывая то, что БК 18 всех каналов заблокированы, при изменении входного сигнала на их выходах не формируются сигналы прямого и обратного счета, что позволяет сохранить упорядоченное расположение эталонных уровней БЭУ 16 в течение интервала времени 0-t (фиг.1), т.е. до того момента, когда входной сигнал не попадет в интервал аналнза блока 17- канала 3. При этом по мере прохождения зон анализа блоков 17-1, 17-2 на выход прямого счета блока 8 поступят два счетных импульса и реверсивный счетчик 10 на выходной шине 12 старших разрядов зафиксирует последовательно два двоичных кода

01 и 10, а .на выходной шине 11 младших разрядов после шифратора 9 будет присутствовать текущее значение кода.

Например, при выходе входного сигнала U (t) из зоны анализа блока 17-2 двоичньй код на выходных шинах 12 и 11 будет меняться следующим образом:

01.111...100

01.111...101

01. 111... ПО

01. 111... 111

10.000...000

а при входе в зону анализа блока 17-3 двоичный код на выходных шинах 12 и 11 будет меняться в соответствии с увеличением входного сигнала:

10.000...001

10.000...010

10.000...Oil

10.111...по

10.111...Ill

11.000...000

Последняя кодовая комбинация будет присутствовать на выходных шинах 12 и 11 при выходе входного сигнала из зоны анализа блока 17-3.

Одновременно с этим, по мере прохождения входным сигналом зон анализа блоков 17-1, 17-2, 17-3, 17-4 и осуществления операции сравнения входного сигнала с N группами эта- лонных напряжений, которые образуют зоны анализа и формирования кода мпадших разрядов, выполняется дополнительная операция по определени знака производной входного сигнала (направления изменения входного сигнала) в каждой группе посредством сравнения входного сигнала со средними эталонными напряжениями групп. Эта операция реализуется посредство БК 18 и БП 7, как и операция совмещения момента начала последовательного смещения групп уровней. Рассморим этот процесс более подробно.

При увеличении входного сигнала, который поступает по входной шине 6 на первые входы компараторов блока 17 (фиг. 3), логические l будут последовательно формироваться на . выходах ,..., i-1, i, i+l,...,k, где k - количество компараторов в блоке 17, а i - номер выхода, соответствующего среднему разряду. При формировании логической 1 на выходе и логического О - на выходе срабатывает элемент И 20 и на выходе RS-триггера 19 появляется логическая 1, которая поступает

5

5

0

5

0

на вход блокировки каналов 1-4, а через них - на четвертый вход БК 18, на четвертые входы элементов И 22 и 23 и тем самым дает разрешение на формирование прямых и обратных счет- ных импульсов.

При появлении логической 1 на выходе на выходе дифференцирующего элемента dU/dt 24 формируется импульс логической 1 и, учитывая, что на выходе инвертора 26 в данный момент присутствует логическая 1, так как на выходе (i+O-ro компаратора блока 17 в данньй момент присутствует логический О, срабатывает четырехвходовый элемент И 23 и на его выходе формируется логическая 1, по фронту которой осуществляется увеличение кода на выходе реверсивного счетчика 13 каналов 1-4. Если при дальнейшем увеличении входного сигнала U (t) логичес кая 1 формируется на выходе компаратора К, то она не приводит к перераспределению уровней на выходах каналов-и блока БК 18.

При уменьшении входного сигнала Ug(t) на выходе формируется . логический О, формирование кото- на выходе элемента 25 задержки задерживается, что позволяет в течение времени задержки блокировать четырехвходовый элемент И 23 посредством ийвертора 26 и дает возможность сработать четырехвходо- вому элементу И 22 после того, как на выходе сформируется логический О и на выходе дифференцирующего элемента dU/dt 24 сформируется импульс логической 1, который будет продублирован на выходе элемента И 22, что соответствует уменьшению выходного кода соответствующего реверсивного счетчика 13.

Описанные действия позволяют одновремено выбрать начало процесса последовательного смещения групп уровней эталонных напряжений (фиг. 1, t) в момент равенства входного напряжения среднему эталонному напряжению средней группы (канал 3).

Последующая операция смещения каждой младшей в данный момент группы эт онных напряжений в направлении изменения входного напряжения в момент совпадения входного напряжения со средним эталонным напряжением группы, которая в данный

.... . 5

момент является средней группой, реализуется посредством изменения выходного сигнала ЦАП 14.

В момент времени t (фиг. 1) входной сигнал попадает в зону анализа блока 17-3 канала 3 и при совпадении его со средними эталонными уровнями (контролируется (фиг. 3) по выходам , .и блока компараторов на выходе прямого счета канала 3 формируется сигнал,который поступает на вход прямого счета канала 1 ,а затем на суммирующий вход реверсивного счетчика 13-I,на выходе которого двоичный код увеличивается на едици- цу младшего разряда. Такое изменение кода на выходе реверсивного счетчика 13-1. и соответственно на входе ЦАП 14-1 приводит к тому, что на выходе ЦАП 14-1 сигнал.и изменяется на величину зоны 0-А (фиг. .1), что вызывает смещение зоны анализа (эталонных напряжений) блока 17-1 на величину направлении изменения входного сигнала Ug,, (t) . При дальнейшем увеличении и„ (t-) вход-

О X

ной сигнал попадает в зону анализа блока 17-4 и при превышении средних эталонных уровней зоны анализа сигнала с выхода прямого счета поступает на суммирующий вход канала 2. Посредством реверсивного счетчика 13-2 и ЦАП 14-2 зона анализа блока 17-2 смещается в Направлении изменения входного сигнала и распола- гается за зоной анализа блока 17-4 после смещенной зоны анализа блока 1 7-1 .

Описанная последовательность смещений в соответствии с измене-, нием входного сигнала будет .осу- . ществляться в интервале времени (фиг.1), а после момента времени t процесс смещения зон анализа будет обратным, так как знак производной (направление изменения): входного сигнала U (t.) будет противоположным.

Коды старших разрядов формируют, по результатам перехода входного сигнала из одной зоны анализа в другую, т.е. при выходе входного сигнала .за интервал напряжений, который образует каждая I pynna эталонных напр.чжений. Эту операцию осу ществляет блок 8 и реверсивный счетчик 10 (фиг. 4).Так например, при увеличении входного сигнала .

99.54

. и,

РХ

(t) с ну.певого уровня унитарный

o

.цифровой код который .формируется на цифровых .выходах канала 1 , поступает с одной стороны на входы много- 5 входных элементов И 35 и через блок 39 - на цифровые выходы блока 8. С другой стороны, первый и последний входы первой- группы входов блока 8 (фиг. 3) непосредственно и через инвертор 31 поступают на входы элемента И 27 , который осуществляет контроль за состоянием, когда на последнем входе сформируется логи-i ческая 1, что соответствует момен-

5 ту перехода входного сигнала Ug (t) зоны анализа блока 17-1. В этот момент на выходе элемента И 27 уста-; навливается логический О, что приводит к запиранию элементов И 35. В

0 результате на выходе блока элементов ИЛИ 39 унитарный код 111... 11 переходит в кед 000...00, что приводит к подаче логической 1 на суммирующий вход реверсивного счет-

5 чика 10. Таким образом, на выходных шинах 12 старших разрядов устанавливается код 000...01.

Рассмотрим более подробно этот процесс. В исходном состоянии на выходах блока 40 инверторов и элемента И 42 присутствовал унитарный код, состоящий из всех единиц. Это приводит .к тому, что на выходе элемента И 42 - логическая 1, а на выходе элемента И 41 - логический О. Как только на выходах блока 39 код изменяется на вс.е нули, на выходе блока 40 инверторов и, следовательно, на.выходе элемента И 41 устанавливается логическая 1, а на выходе элемента- И 42 - логический

0

5

0

О , но за счет элемента 44 задержки на прямом выходе элемента И-НЕ 46 устанавливается логическая 1, которая- запоминается в элементе памяти, выполненном- на элементах ИЛИ 48 и И 50. При этом инверсный выход элемента И-НЕ 46 обнуляет элемент памяти, выполненный на

элементах ИЛИ 47 и И 49.

I

При .изменении кода на выходе блока 39 в обратном направлении на прямом выходе элемента И-НЕ 45 формируется логическая 1, которая поступает на вычитающий вход реверсивного счетчика 10, уменьшая его состояние на единицу младшего разряда.

Одновременно с фор дарованием старшихразрядов формируют младшие разряды путем выделения результата сравнения .входного напряжения с . соответствующей группой эталонных напряжений, т.е. с той группой, которая в данный момент соответствует- величине входного напряжения. Это осуществляется в блоке 8 посредством элементов И 27-28 и инверторов 31-34, которые пропускают через блок 39 на выходные шины 1 1 информагдион- ные коды младших.разрядов.

Фо рмула изобретения

1.:Способ следящего аналого- цифрового преобразования, включающий сравнение входного напряжения с группами уровней эталонных .напряжений, последовательное смещение групп уровней эталонных напряжений в зависимости от результатов сравнения, формирование кода младших разрядов по результатам сравнения входного напряжения с соответствующей группой уровней эталонных напряже- и формирование кода старших разрядов, о тли ч ающийся тем,

го диапазона преобразования, момент начала последовательного смещения групп уровней эталонных напряжений совмещают с моментом равенства входного напряжения среднему уровню эталонного напряжения средней группы, при сравнении входного напряжения с группами уровней эталонных напряжений определяют знак производной входного напряжения, а последовательное смещение групп уровней эталонных напряжений осуществляют соответственно для каждой мпадшей группы в зависимости от знака производ- ной входного напряжения, при этом формирование кода старших разрядов осуществляют в момент р1авенства входного напряжения старшему уровню эта лонного нaпpяжJeния каждой группы путем подсчета числа указанных моменто с учетом соответствукщегр знака производной входного напряжения в данной группе уровней эталонных напряжений.

2. Устройство следящего аналого- цифрового преобразования, содержащее N каналов определения младших .разрядов, аналоговые входы которых

10

зо

35

40

. 50 в

229954

объединены и являются входной шиной, а цифровые выходы подключены к соответствующим N группам входов цифрового коммутатора каналов, и шифратор, 5 отличающееся тем, что, с целью расширения динамического диапазона преобразования, в него введены блок памяти и реверсивный счетчик, выходы которого являются соответствующими выходными шинами старших разрядов, вход сброса объединен с первым входом блока памяти и входами сброса N каналов определения младших разрядов и является 15 шиной сброса, а су ммиругаций и вычитающий входы подключены соответственно к выходам прямого и обратного счета цифрового коммутатора кан.а- лов, цифровые выходы которого соединены с соответствующими входами шифратора, выходы которого являются соответствуклцими выходными шинами .младших разрядов, при этом входы блокировки N каналов определения младших разрядов Объединены и подключены- к выходу блока памяти, второй и третий входы которого соответственно подключены к (k/2-l)-My и (k/2)-My цифровым выходам т-го каналов определения младших разрядов, где k - число цифровых выходов канала определения младших разрядов, а т N/2+Q,причем выходы прямого и обратного счета каждого i-ro канала определения младших разрядов, где i,2,...N, соответственно подключены к суммирующему и вычитающему входам соответствунмцего j-Го канала определения младших разрядов, где j N/2+i, если N/2+i N, и j(N/2+

20

25

45

55

+i)-N, если N/2+i N.

3. Устройство по п.2, отличающееся тем, что, канал определения младших разрядов вы- полнен на блоке ключей, блоке компараторов, блоке эталонных уровней,, источнике опорного сигнала, цифро- аналоговом преобразователе и реверсивном счетчике, вход сброса которо го является входом сброса канала определения младших разрядов, суммирующий и вычитающий входы - соответственно суммирующим и вычитающим входами канала определения младших разрядов, а выходы - подключены к соответствующим входам цифроаналогового преобразователя, выход которого соединен с первым входом блока

эталонных уровней, второй вход которого подключен к выходу источника опорного сигнала, а выходы к соответствующим первым входам блока Koi iapaTOpoB, второй вход которого является аналоговым входом канала определения младших разрядов, а выходы - соответствующими цифровы- NM выходами канала определения

младших разрядов, при этом (и/2-1)-й/ ю первого элемента И-НЕ, второй вход и (k/2+l)-й выходы блока компа- которого соединен с выходом (Ы-ь2)-го

многовходового элемента И, первый выход - с перилм входом (N+l)-ro двухвходового элемента И, а второй выход - с первым входом первого элемента ИЛИ, выход которого подключен к первому входу (N+2)-ro двухвходового элемента И, второй вход которого соединен с первым выходом второго элемента И-НЕ, а выход - с вторым входом первого элемента ИЛИ и является выходом обратного счета цифрового коьмутатора каналов, выход прямого счета которого является первым входом второго элемента ИЛИ и выходом (N+l)-ro двухвходового э гемента И, второй вход которого - подключен к выходу второго элемента ИЛИ, .второй вход которого соединен с вторым вы содом второго элемента И-НЕ, первый вход которого соединен с выходом (N+1)-го мно говходового элемента И, а второй вход через второй элемент задержки соединен с выходом (N+2)-ro многовходового элемента И, входы которого соответственно подключены ко всем выходам блока элементов ИЛИ, кроме последнего.

6. Устройство по п, 3, о т л и чающееся тем, что блок ключей выполнен на элементе задержки, дифференцируклцем элементе, .инверторе и двух элементах И, первые входы которых объединены и являются первым входом блока ключей, а вторые входы объединены и подключены к выходу дифференцирующего элемента, вход которого является вторым входом блока ключей, третий вход которого через элемент задержки соединен с третьим входом первого элемента И, выход которого является выходом обратного счета блока ключей; выход прямого счета которого является выходом второго элемента И, третий вход которого через инвертор подключен к выходу элемента задерж-

раторов соединены с соответствующими первым, вторым и третьим входами блока ключей, четвертый вход которого является входом блокировки ка- is нала определения младших разрядов, а первый и второй выходы - соответственно выходами прямого и обратного счета канала определения младших разрядов.20

4.Устройство по п. 2, о т л и - чающееся тем, что блок памяти выполнен на инверторе, элемент е

И и RS-триггере-, выход и R-вход которого является соответственно вы- 25 ходом и первым входом блока памяти, второй вход которого является первым входом элемента И, выход которого соединен с S-входом RS-триггера, а второй вход - с выходом инвертора, зо, вход которого является третьим входом блока памяти.

5.Устройство по п. 2, о т л и чающееся тем, что цифровой коммутатор каналов выполнен на N инверторах, (N+2) дву входовых элементах И, (N+2) многовходовых элементах И, блоке инверторов, двух элементах задержки, двух элементах ИЛИ, двух элементах И-НЕ и блоке . элементов ИЛИ, N групп входов которого подключены к соответствующим выходам N многовходовых элементов И, а выходы являются соответствую- цифровыми выходами цифрового коммутатора каналов, каждая i-ая группа входов которого,где ,2. . .N, является соответствующими первыми входами соответствующего i-ro многовходового элемента И, второй вход которого подключен к выходу соответствующего i-ro двухвходового элемента И, первый вход которого является первым входом соответствующей 1-ой группы входов цифрового 55 коммутатора каналов, последний

вход каждой группы входов которого через соответствующий инвер35

40

45

50

тор соединен с вторым входом соответствующего i-ro двухвходовр| о элемента И, при этом все выходы блока элементов ШlИ кpoмe последнего через блок инверторов соответственно соединены с входами (N+1)-го ьшоговходового элемента И, выход которого через первый элемент за держки подключен к первому входу

11,122995412

ки,- а четвертый вход объединен с И и является четвертым входом блока

четвёртым входом первого элемента

ключей;

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Способ многоканального аналого-цифрового преобразования сигналов и устройство для его осуществления | 1986 |

|

SU1411972A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1193809A1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1202055A1 |

Изобретение относится к вычислительной и измерительной технике и может быть использовано при построении следящих систем. Цель изобретения - расширение динамического диапазона преобразования. При изменении входного напряжения, поступающего по входной шине на аналоговые входы N каналов определения младших разрядов, осуществляют его сравнение с группами эталонных напряжений блоков эталонных уровней (БЭУ) каждого канала , и формирование младших разрядов на выходных шинах с помощью блоков компараторов каналов, цифрового крьг мутатора каналов (ЦКК) и шифратора. С помощью блоков ключей (БК) кана лов и блока памяти реализуется совмещение момента начала последовательного смещения групп зфовней БЭУ с моментом равенства входного напряжения среднему уровню эталонного напряжения средней группы, а также определяется знак производной входного напряжения. Последовательное смеще- ,ние групп уровней БЭУ каналов осуществляют с помощью БК, реверсивных счетчиков и цифроаналоговых преобразователей каналов соответственно для каждой мпадшей группы в зависимости от знака производной. Коды старших разрядов формируют на шинах посредством ЦКК и реверсивного счетчика в момент равенства . входного, напряжения старшему уровню эталонного напряжения БЭУ каналов путем подсчета указанных моментов с учетом соответствующего знака производной входного напряжения в данной группе уровней эталонных напряжений. 4 з.п. , 4 ил. (Л

фиг. t

S CSpoc

Г ,

Фиг.З

Т

серж

ЖМЦИ Заказ 2459/58 Тираж 816Подписное

Производств.-полиграф, пред-е, г. Ужгород, ул. Проектная, 4

| Способ параллельно-последовательногопРЕОбРАзОВАНия НАпРяжЕНия B КОд | 1977 |

|

SU819954A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Статистические измерения и алго- Еитмизация измерений | |||

| Сборник, вып | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Фальцовая черепица | 0 |

|

SU75A1 |

Авторы

Даты

1986-05-07—Публикация

1983-04-21—Подача