ответственно первого и второго элементов И-HEj управляющие входы которых соединены соответственно с прямым и инверсным выходами переноса сумматора и с управляющими входами схемы сравнения. Первая и вторая группы информанионных входов последней соединены соответственно с выходами младших разрядов сумматора и выходами элементов И, первые входы которых соединены с выходами счетчика заполнения, а вторые - со вторым синхронизирующим входом устройства.

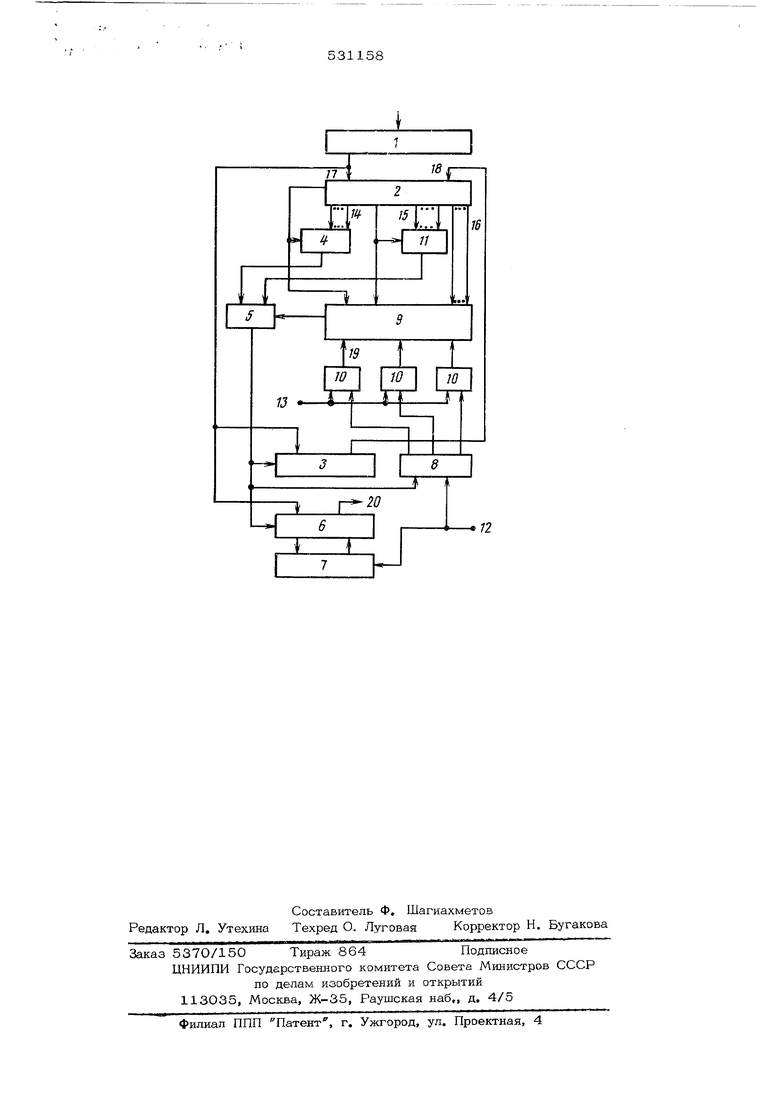

На чертеже представлена блок-схема усройства.

Устройство для сжатия информации содержит регистр 1 текущей выборки, сумматор 2, оперативную память 3, первый элемент И-НЕ 4, элемент ИЛИ 5, регистр числа 6, буферную память 7, счетчик заполнения 8, схему сравнения 9, элементы И 10, второй элемент И-НЕ 11,

На чертеже обозначены: 12 первый и второй 13 синхронизирующие входы устройства, прямые 14 и инверсные 1.5 выходы старщих разрядов сумматора, 16 выходы младщих разрядов сумматора первого 17 и вход второго 18 слагаемых сумматора , 19 -. входы схемы сравнения и ,20 - выход устройства

Предлагаемое устройство может быть использовано для любой разрядности двоичного кода выборок и допустимого отклонеНИЯл

Предположим, что код выборки - двоичный десятиразрядный, а максимальная аппаратура равна (111 ). На рассмат-L J

риваемом шаге апертура равна 4 (100

Рассмотрим работу устройства для однОканальной системы,,

На регистр текущей выборки 1 поступаю через равные промех утки времени кодь выборок, С выхода этого регистра параллельным кодом выборка поступает на вход первого слагаемого сумматора.

На вход второго слагаемого поступает параллельный обратный код с выхода оперативной памяти, где хранится значение последней неизбыточной выборки.

Сумматор - параллельный, причем выход переноса старшего разряда соединен со входом переноса. Рассмотрим случай, когда величина текущей выборки (содержимое регистра 1) больше неизбыточной выборки (содержимого оперативной памяти). В этом случае сумматор дает единичный сигнал переноса, и на прямых выходах сумматора появляется прямой код разности, а на инверсных - обратный. Если разность больше максимальной апертуры (для рассматриваемого случая 111), то хотя бы

на первом выходе из семи старших разрядов сумматора будет нулевой инверсный сигнал. В этом случае на выходе первого элемента И-НЕ оказывается единичный сигнал (поскольку на входы элемента 5 подаются инверсные выходы семи старших разрядов сумматора). Единичный сигнал проходит через элемент ИЛИ 5 и разрешает запись содержимого регистра текущей выборки и регистр числа, оперативную память и буферную память, а также прибавляет единицу в счетчик 8 заполнения. Если разность, найденная сумматором, меныле максимальной апертуры, то схема сравне ния для трехразрядных ходов производит сравнение разности с величиной апертуры. При этом код апертуры поступает с выходов 16 на Труппу входов апертуры схемы сравнения и с выходов счетчика 8 через элементы И 1О, Если разность между текущей и неизбыточной выборками; найденная сумматором и поступившая на входы схемы сравнения, больше значения апертуры (для рассматриваемого случая 100 ),

то схема сравнения выдает сигнал на элемент ИЛИ 5. При этом содержимое регист-ра 1 записывается в регистр числа, оперативную память и буферн то память, и к содержимому счетчика прибавляется единица.

Если содержимое регистра текуш.ей выборки меньше неизбыточной выборки на оперативной памяти, то сумматор выдает единичный сигнал инверсии переноса и обратный код разности на прямые выходы. Если модуль разности, найденный сумматором, превыщает величину максимальной апертуры (111 ), то хотя бьг на одном из семи старших разрядо. cyMviax-opa ока- зывается нулевой сигнал, В этом случае при единичной инверсии сигнала переноса старшего разряда на выходе второго элемента И-НЕ 11 формируется единичный сигнал, который, пройдя элемент ИЛИ 5, разрешает запись в регистр 6, оперативную

5 память, буферную память и прибавление единицы в счетчик. Если модуль разности не превышает максимальную апертуру, то схема сравнения определяет больше ли модуль разности, чем значение апертуры, коBторое nocTynaef на группу входов апертуры 19 схемы сравнения, В случае превышения сигнал подается на схему ИЛИ 5, и содержимое регистра 1 переписывается в регистр 6, оперативную память, буферную

5 память и к содержимому счетчика прибавляется единица.

Таким образом, на буферную память поо тупает неравномерный поток выборок из ре.fHCTpa 1 (неизбыточные выборки). Буфер- ная память предназначена для выравнивания во времени потока неизбыточных выборок, поэтому считывание с буферной памяти на выход устройства 2О происходит с равномерной частотой по сигналам, поступающи на первый синхронизирующий вход устройст ва. При считывании содержимое счетчика уменьшается на единицу. Для считывания информации из буферной памяти 7 вместо регистра числа может быть использован специальный вспомогательный регистр. Счетчик заполнения 8 в зависимости от числа заполненных ячеек буферной памяти по сигналам, подаваемым на второй синхро низирующий вход устройства, устанавливает значение апертуры, с 4oтopoй производится сравнение в схеме сравнения, причем большему запош1ению соответствуют большие апертуры. С приходом новой текущей выборки цикл работы устройства для обработки и сжати информации повторяется. Изобретение позволяет примерно вдвое повысить быстродействие устройства и упр тить схему сравнения (за счет сравнения лишь младших разрядов), Формула изобретения Устройство для обработки и сжатия информации, содержащее регистр текущей выборки, информационный вход которого со входом устройства, сумматор, один вход которого соединен с выходом регистра текушей выборки, с информадионным входом оперативной памяти и информа ционным входом регистра числа, выход которого соединен с выходом устройства первый С1шхронизир тощий вход которого сое- дршен с тактовым входом буферной памяти и вычитающим входом счетчика заполнения суммирующий вход которого соедш1ен с уП равляющими входами оперативной памяти и регистра числа, соед -шенного двз-хсторэк-ней связью с буферной памяп ью. элемент ИЛИ, элемент И и схему сравления; о тличаюшееся , что. с целью повышения быстродействия i; сокрашекия количества оборудования, оно содержит первый и второй элементы И-НЕ,. выходы которых и выход схемы сравненн ; сэедтшены со входами элемента НЛИ, выход которого соединен с друпчк; входол: сумматора, прямые и инверсные выходы старших разрядов которого соединены с ршформашюш ым. вхо далп-1 соответстве1шо первого и второго элементов I--I-НЕ, управляющие которых соединены соотсетстзедшо с прямых и 1Ыверсным выхода:- и переноса cyNMaTOpa к с управляющими Exoдa n : схемы срзвкения, первая и вторая группа лнфзрлшщюьных входов которой соед1шекь саотьотственно с выходами младп;их разрядг з сул;матора и выходами злементов Г1; первь;е входь; которых соед1шены с вь:хэаам1; счетчкка заполнения, а вторые - со вторык-; синхронизирующим входом устройства. Источники 1шформецк -: принятые во внимание прк экспертизе: Is Авторское свидетельстзэ СССР № 435552, кло GOS с 15/00, 1972, 2. Патент США Xs 3501750, кл. .5, 1970,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки и сжатияиНфОРМАции | 1979 |

|

SU840914A2 |

| Адаптивное устройство для передачи информации | 1977 |

|

SU696520A1 |

| Устройство для передачи информации со сжатием данных | 1976 |

|

SU748484A1 |

| Многоканальное устройство для передачи информации с временным уплотнением каналов | 1978 |

|

SU720754A1 |

| Устройство для обработки и сжатия информации | 1983 |

|

SU1101832A1 |

| Устройство для обработки и сжатия информации | 1986 |

|

SU1381572A1 |

| Устройство для сжатия и передачиизМЕРиТЕльНОй иНфОРМАции | 1979 |

|

SU841009A1 |

| Устройство для передачи телеметрической информации | 1974 |

|

SU512484A1 |

| Устройство для сжатия информации | 1976 |

|

SU567174A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

Авторы

Даты

1976-10-05—Публикация

1974-06-14—Подача