(Л

оо оо

ел

N3

Изобретение относитci к вычислито.чьной и измери ie:ihiK i технике и может быть использовано в измер11ге. 1ьных системах, ис юльзук)и1и.х временное разле.. 1ение каналов при донусковом контроле или квазиобратимом сжатии информации.

He.ib изобретения 1ов1)анение быстродействия устройства.

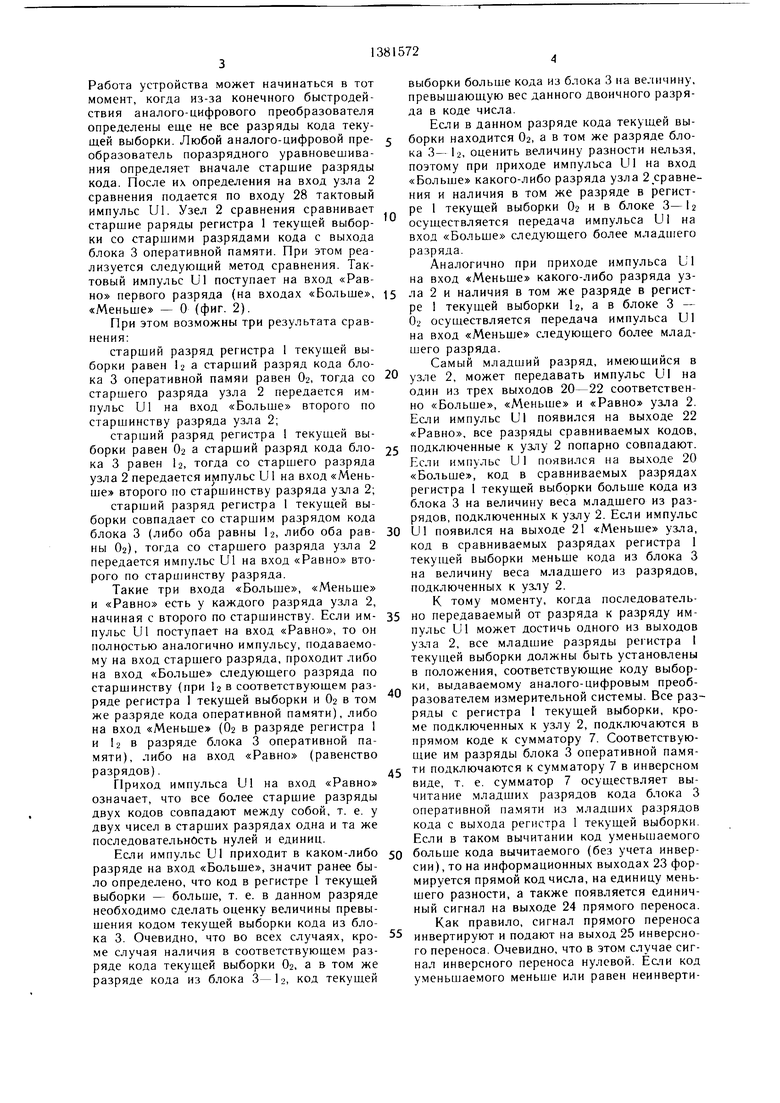

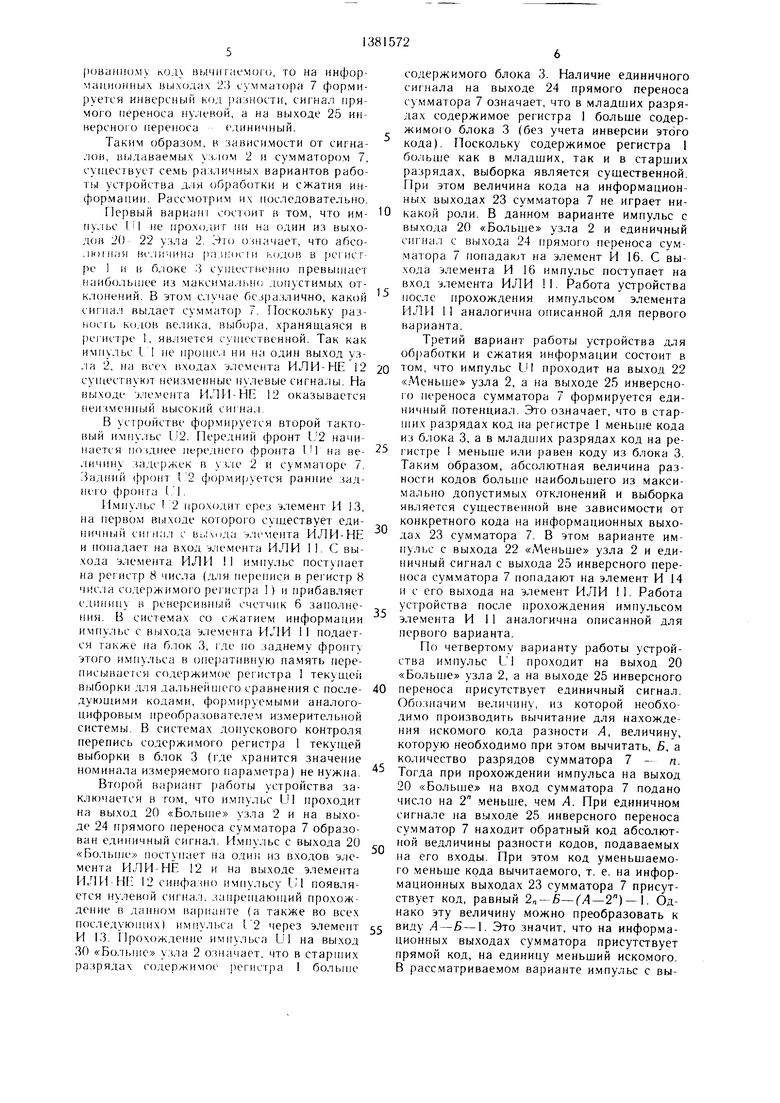

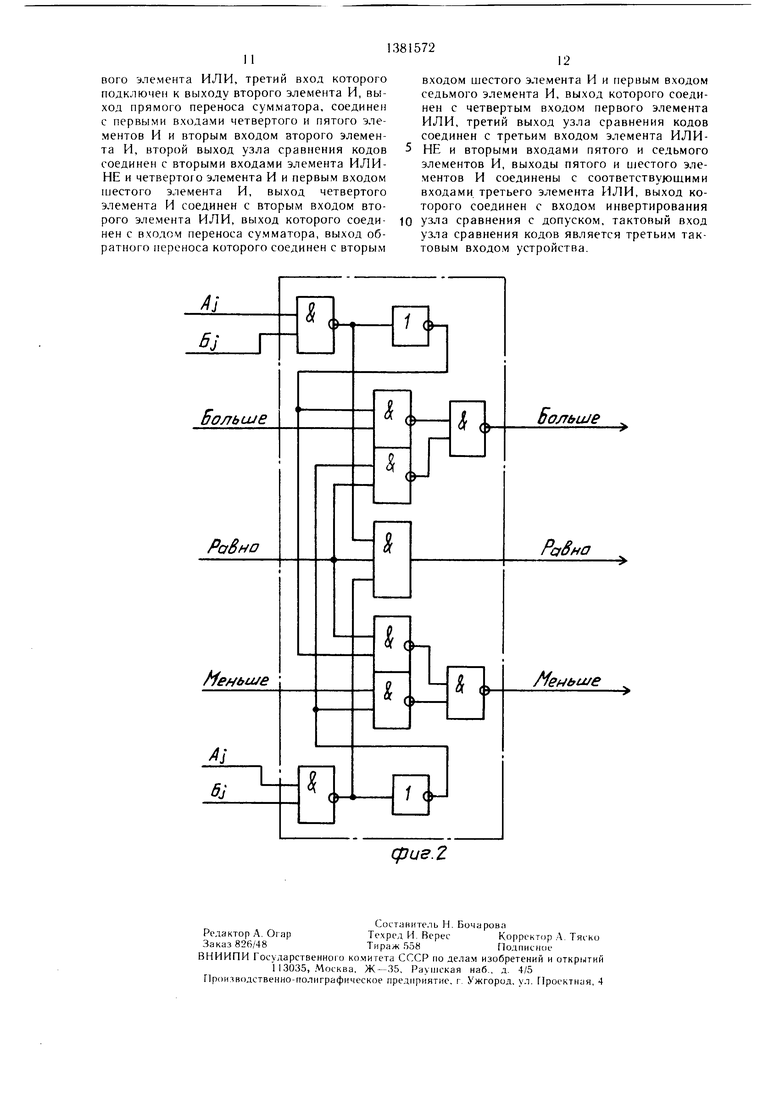

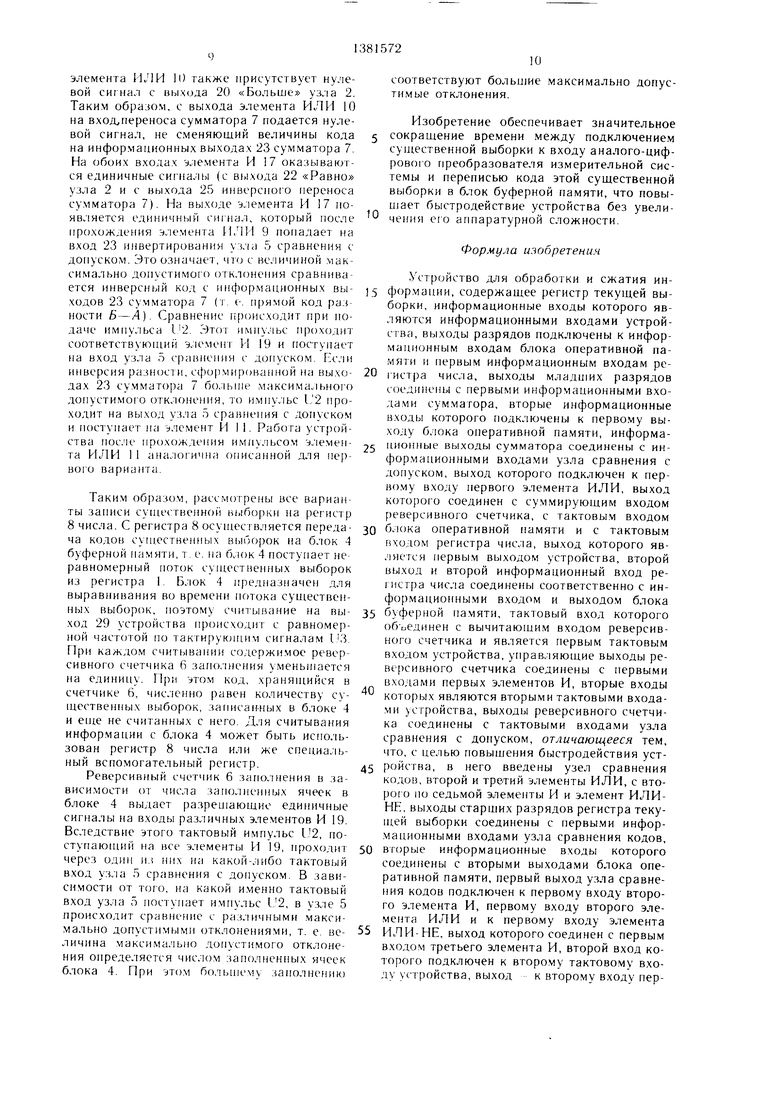

На фиг. 1 иредставлена структурная схема устр(.)йс-тва: на (}1иг. 2 э.пектрическая схе.ма одного нч узла сравнения кодов.

Устройство соде)жи регистр 1 текчией выборки, узел 2 сравнения кодов, блок 3 оперативио на.мяти, б.тик 4 буферной памяти, узел 5 сравпеиия с допуском, реверсивный c leit iiK 6, сумма1()|1 7, 8 чис. 1а, :.лементы ИЛИ 9 11. элемент ИЛИ-НН 12 и улеме1ггы И 3 И .

На фиг. 1 I обо (начены в1)Гходы 20 22 соответсгвенно «lio.iijHie, «Мепыпе, «Равно узла 2 с()а1М1ения кодов, информационные выходы 23, выходы 24 и 25 соответственно прямого и обратного переноса сумматора, первый 26, второй 27 и третий 28 тактовые входы и вьгход 29 устройства.

При этом регистр 1 текущей выборки и регистр 8 числа MOIAT быть выполнены но стандартной схеме на трип ерах D-гииа.

Узе;1 2 нередаег импу,1ьс, приходящий на его тактов1)1Й вход, fia выход 22 «Равно, если все старшие с регист)а 1 теку выборки блока нонарно совпадают. Узе.т 2 передает импульс. н|)нходян1ий на его тактовый вход, па в(гход 20 «Больп1е, если код старпшх разрядов в )егист)е 1 текущей выборки превьмнает код ста)П1их разрядов в блоке 3 ровно па единицу младп1его из подключаемых к нему разрядов. Узел 2 передает имиульс, приходящий на его тактовый вход, на выход 21 «Л ены11е, если код старн1их разрядов в регистре 1 гекуншй выборки ровно на единицу младнкмо из подключаемых к узлу разрядов меныне кода старпшх раз)я- дов блока 3.

Блок 3 оперативп(й памяти в однока- нальных системах выполнен в виде регистра (например, па i e)ax), на котором запоминается в системах киазиобратимо| о сжатия последняя и:; (ыборок, переданных в )е- гистр 8 числа и далее в блок 4, в системах допускового контро.г|я в iTOM регистре хранится код ио.мина;1ьио1 о значения пара.метра, с которым сравнивается рассматриваемая выборка. В мног оканальных измерительньгх системах в б/юк 3 оперативной памяти, кроме регист)а, входит накопитель памяти, из которого на регистр нерегп сывается код, с которым необходимо 1.-ра) ве.тичину выборки в рассматpHiuiCMOM канале измерительной системы.

Узе.т 5 сравнения с допуском имеет в своем составе блок инвертирования кода и схему сравнения (иа фиг. 1 не показаны). Блок инвертирования кода инвертирует все вход

ные сигналы, приходящие на информационные входы узла 5 с сумматора 7, если на входе инвертирования присутствует единичный сигнал. EcvTn на входе инвертирования 5 ну/к вой сигнал, блок инвертирования кода не осуществляет инверсию, В простейшем случае каждый разряд блока инвертирования кодов может включать в свой состав два элемента И, первый вход первого из которых непосредственно соединен с соответствую- Пими информационным входом, который через инвертор подключен к первому входу вто)ого элемента И, Второй вход второго элемента И соединен с входом инвертирования, который через инвертор подключен к

2 второму входу первого элемента И. Выходом данного разряда обратителя кодов является :.темент ИЛИ, входы KOTOporcj 1тодключены к выходам первого и второго элементов И. Схема сравнения состоит из ряда элементов И, выходы которых подключены к входам

0 выход)1ого эле.мента ИЛИ, выход которог О яв:1яется выходом узла 5 сравнения, К первым входам каждого из элементов И схемы сравнения узла 5 сравнения с допуском подключен соответствующий тактовый вход

, узла 5 сравнения с допуском. Остальные входь: элементов И в схеме сравнения подключены к выходам блока инвертирования кодов так, чтобы осун1ествлялось сравнение с вь1бранным допуском. Например, если для трехразрядных кодов необходимо определить

0 коды, большие числа , то все эти коды имеют единицу в третьем разряде и на элемент И достаточно подать один сигнал с гретьего разряда. Все трехразрядные коды, большие , имеют единицы в двух cTapiHHx разрядах, поэтому на элемент И

5 достаточно подать два сигнала (с третьего и второго разрядов).

Сумматор 7 выполнен по схеме параллельного сум.матора, в котором сигнал прямого нерепоса на выходе 24 через инвертор под- ключе п к выходу 25.

0 Все остальные элементы устройства для обработки и сжатия информации являются стандартными.

Устройство д. 1Я обработки и сжатия информации работает следующим образом.

Предлагаемое устройство может быть ис- нользовано для любой разрядности двоичного кода выборок и допустимого отклонения. Нредположим, что код выборки - двоичный десятиразрядный, а наибольшее из максимально допустимых отклонений не превы0 1нает 7io (ПЬ). Иусть на рассматриваемом Hiare максимально допустимое отклонение равно 3|п (0112).

/1ля простоты работу устройства рассмотрим для одноканальной измерительной системы.

5 На информационные входы регистра 1 текун1ей выборки поступают коды текущих выборок с аналого-цифрового преобразователя (не показан) измерительной системы.

Работа устройства может начинаться в тот момент, когда из-за конечного быстродействия аналого-цифрового преобразователя определены еще не все разряды кода текущей выборки. Любой аналого-цифровой пре- образователь поразрядного уравновешивания определяет вначале старшие разряды кода. После их определения на вход узла 2 сравнения подается по входу 28 тактовый импульс U1. Узел 2 сравнения сравнивает старшие раряды регистра 1 текушей выбор- ки со старшими разрядами кода с выхода блока 3 оперативной памяти. При этом реализуется следующий метод сравнения. Тактовый импульс U1 поступает на вход «Равно первого разряда (на входах «Больше, «Меньше - О (фиг. 2).

При этом возможны три результата сравнения:

старший разряд регистра 1 текущей выборки равен 12 а старший разряд кода блока 3 оперативной памяи равен 02, тогда со старшего разряда узла 2 передается импульс U1 на вход «Больше второго по старшинству разряда узла 2;

старший разряд регистра 1 текущей выборки равен 02 а старший разряд кода бло- ка 3 равен 12, тогда со старшего разряда узла 2 передается импульс U1 на вход «Меньше второго по старшинству разряда узла 2;

старший разряд регистра 1 текущей выборки совпадает со старшим разрядом кода блока 3 (либо оба равны h, либо оба рав- ны 02), тогда со старшего разряда узла 2 передается импульс U1 на вход «Равно второго по стари инству разряда.

Такие три входа «Больше, «Меньше и «Равно есть у каждого разряда узла 2, начиная с второго по старшинству. Если им- пульс U1 поступает на вход «Равно, то он полностью аналогично импульсу, подаваемому на вход старшего разряда, проходит либо на вход «Больше следующего разряда по старшинству (при 2 в соответствующем разряде регистра 1 текущей выборки и 02 в том же разряде кода оперативной памяти), либо на вход «Меньще (02 в разряде регистра 1 и Ь в разряде блока 3 оперативной памяти), либо на вход «Равно (равенство разрядов).

Приход импульса U1 на вход «Равно означает, что все более старшие разряды двух кодов совпадают между собой, т. е. у двух чисел в старших разрядах одна и та же последовательность нулей и единиц.

Если импульс U1 приходит в каком-либо разряде на вход «Больще, значит ранее было определено, что код в регистре 1 текущей выборки - больше, т. е. в данном разряде необходимо сделать оценку величины превышения кодом текущей выборки кода из блока 3. Очевидно, что во всех случаях, кро- ме случая наличия в соответствующем разряде кода текущей выборки 02, а в том же разряде кода из блока 3-12, код текушей

выборки больше кода из блока 3 на величину, превышающую вес данного двоичного разряда в коде числа.

Если в данном разряде кода текущей выборки находится 02, а в том же разряде блока 3--h, оценить величину разности нельзя, поэтому при приходе импульса U1 на вход «Больше какого-либо разряда узла 2 сравне- ния и наличия в том же разряде в регистре 1 текущей выборки 02 и в блоке 3-Ij осуществляется передача импульса U1 на вход «Больше следующего более младшего разряда.

Аналогично при приходе импульса U1 на вход «Меньще какого-либо разряда узла 2 и наличия в том же разряде в регистре 1 текущей выборки Ь, а в блоке 3 - 02 осуществляется передача импульса U1 на вход «Меньще следующего более младшего разряда.

Самый младший разряд, имеющийся в узле 2, может передавать импульс UI на один из трех выходов 20-22 соответственно «Больше, «Меньше и «Равно узла 2. Ести импульс U1 появился на выходе 22 «Равно, все разряды сравниваемых кодов, подключенные к 2 попарно совпадают. Если импульс U1 появился на выходе 20 «Больше, код в сравниваемых разрядах регистра 1 текущей выборки больще кода из блока 3 на величину веса младщего из разрядов, подключенных к узлу 2. Если импульс U1 появился на выходе 21 «Меньще узла, код в сравниваемых разрядах регистра 1 текущей выборки меньще кода из блока 3 на величину веса младшего из разрядов, подключенных к узлу 2.

К тому моменту, когда последовательно передаваемый от разряда к разряду импульс U1 может достичь одного из выходов узла 2, все младшие разряды регистра I текущей выборки должны быть установлены в положения, соответствующие коду выборки, выдаваемому аналого-цифровы.м преобразователем измерительной системы. Все разряды с регистра 1 текущей выборки, кроме подключенных к узлу 2, подключаются в прямом коде к сумматору 7. Соответствующие им разряды блока 3 оперативной памяти подключаются к сумматору 7 в инверсном виде, т. е. сумматор 7 осуществляет вычитание младших разрядов кода блока 3 оперативной памяти из младших разрядов кода с выхода регистра 1 текущей выборки. Если в таком вычитании код уменьшаемого больше кода вычитаемого (без учета инверсии) , то на информационных выходах 23 формируется прямой код числа, на единицу меньшего разности, а также появляется единичный сигнал на выходе 24 прямого переноса.

Как правило, сигнал прямого переноса инвертируют и подают на выход 25 инверсного переноса. Очевидно, что в этом случае сигнал инверсного переноса нулевой. Если код уменьшаемого меньше или равен неинверти()BaHiiu.iy код вычк ae.MOiii, то на информационных выходах 2:i сумматора 7 формируется инверсный кол разности, сигнал прямого переноса ну.тевой, а на выходе 25 ин- HepcHOio переноса единичный.

Таким образом, в зависимости от сигналов, выдаваемых узлом 2 и сумматором 7, существует семь различных вариантов работы устройства для обработки и сжатия ин- формапии. Рассмотрим их последовательно.

Первый вариа Г1 состоит в том, что импульс III не проходит пи на один из выходов 20 22 узла 2. Эго означает, что абсо- :1К)111.чя ве.;1ичина кг.инкли к(;дов в iiei3icT- ре 1 и в б;1оке . 5 cyiuecriieHH(j превышает наибольшее из максима.илн; допустимых отклонений. В этом с.тучае безразлично, какой сигнал выдает сумматор 7. Поскольку раз- носгь кодов велика, выбора, хранящаяся в ()еги(. 1ре 1, является существенной. Так как импульс 11 не npoHje.i ни Fia один выход уз- .ла 2, на всех входах „чемента ИЛИ-НЕ 12 существуют неизменные нулевые сигна;1ы. На выходе . ента ИЛИ-НП 12 оказывается неизменный высокий сигнал.

В устройстве формируется второй тактовый импульс 1,12. Передний фронт U2 начинается позднее переднего фронта 1М на величину задс)жек в уз-лс 2 и суммаюре 7. .Задний if))OHT I 2 формируется ранние заднего фронта (Л ,

Импу. И)С 12 проходит ерез элемент И 13, на первом вьгходе которого существует еди- пичный с в.лпд,а элемента ИЛИ-НЕ и попадает на вход э.лемента ИЛИ 1 1. С выхода элемента ИЛИ 11 импульс поступает на регистр 8 числа (для переписи в ре1 истр 8 чис.ла c(jдepжимol o регистра 1) и прибавляет единицу в реверсивный счетчик 6 заполпе- пия. В системах со сжатием информации импульс с выхода элемента ИЛИ 11 подается также на б.лок 3, где по заднему фронту этого импульса в оператив(1ую память пере- писынаегся содержимое регистра I текущей В1)1борки для дальнейшего сравнения с последующими кодами, фор.мируемыми аналого- цифровым преобразоЕштелем измерительной системы. В системах допускового контроля перепись содержимого регистра 1 текущей выборки в блок 3 (где хранится значение номинала измеряемого ггара.метра) не нужна.

Второй вариант аботы устройства заключается в том, что и.мпульс U1 проходит на выход 20 «Больше узла 2 и на выходе 24 прямого переноса сумматора 7 образован единичный сигнал. И.мггульс с выхода 20 «Bo. ibHje постуггает на один из входов элемента ИЛИ-НЕ 12 и на выходе элемента ИЛИ-НГ: 12 синфазно импульсу Ь 1 появляется нулевой сигна;|. запрегцающий прохождение в данном варианте (а также во всех последуюпгих) импульса Г2 через элемент И 13. Прохождение импульса Ul на выход 30 «Больше у.зла 2 означает, что в старпгих разрядах содержимое регистра 1 больгне

5

5

содержимого блока 3. Наличие единичного сигнала на выходе 24 прямого переноса сумматора 7 означает, что в младщих разрядах содержимое регистра 1 больше содержимою блока 3 (без учета инверсии этого кода). Поскольку содержимое регистра 1 больще как в младщих, так и в старщих разрядах, выборка является существенной. При этом величина кода на информационных выходах 23 сум.матора 7 не играет ни0 какой роли. В данном варианте иг пульс с выхода 20 «Больще узла 2 и единичный сигна.л с вьгхода 24 ггрямого переноса сумматора 7 пoпaдaкJT па элемент И 16. С выхода эле.мента И 16 импульс поступает на вход элемента ИЛИ 11. Работа устройства после прохождения импульсом элемента ИЛИ 11 аналогична описанной для первого варианта.

Третий вариант работы устройства для об|)аботки и сжатия инфор.мации состоит в

0 том, что импу.тьс IJI проходит на выход 22 «Меньше узла 2, а на выходе 25 инверсного переноса сумматора 7 формируется единичный потенциал. Это означает, что в стар- 1ПИХ разрядах код на регистре 1 меньше кода из блока 3, а в младпгих разрядах код на регистре I меньше или равен коду из блока 3. Таким образом, абсолютная величина разности кодов больп1е наибольшего из максимально допустимых отклонений и выборка является существенной вне зависимости от конкретного кода на информационных выходах 23 сумматора 7. В этом варианте им- гульс с выхода 22 «ЛАеньще узла 2 и единичный сигнал с выхода 25 инверсного переноса сум.матора 7 попалтают на элемент И 14 и с его выхода на элемент ИЛИ II. Работа устройства после прохождения импульсом элемента И 11 аналогична описанной для первого варианта.

По четвертому варианту работы устройства импульс Ul проходит на выход 20 «Больц е узла 2, а на выходе 25 инверсного

0 переноса присутствует единичный сигнал. Обозначим величину, из которой необхо- ди.мо производить вычитание для нахождения иско.мого кода разности А, величину, которую необходимо при этом вычитать. Б, а количество разрядов сумматора 7 - п. Тогда при прохождении импульса на выход 20 «Больше на вход сумматора 7 подано число на 2 меньше, чем А. При единичном сигнале на выходе 25 инверсного переноса су.мматор 7 находит обратный код абсолютной ведличины разности кодов, подаваемых на его входы. При этом код уменьшаемого меньще кода вычитаемого, т. е. на информационных выходах 23 сумматора 7 присутствует код, равный 2п (А-2) - 1. Однако эту величину можно преобразовать к

5 виду А-5-1. Это значит, что на информационных выходах сумматора присутствует прямой код, на единицу меньший искомого. В расс.матриваемом варианте импульс с вы0

5

5

0

хода 20 « больше узла 2 поступает через элемент ИЛИ 10 на вход циклического переноса сумматора 7, что увеличивает на единицу код на выходе 23 этого сумматора (т. е. на выходе 23 формируется точная величина искомого кода А-Б разности). Посколь ку сигналы на выхода 21 и 22 «Меньше и «Равно узла 2 являются нулевыми, на выходах элементов И 17 и 18 также находятся нулевые сигналы. Это определяет нулевую величину выходного сигнала элемента ИЛИ 9.

При подаче нулевого сигнала с выхода элемента ИЛИ 9 на вход инвертирования узла 5 сравнения с допуском выходные коды сумматора 7 без инвертирования сравниваются с кодом максимально допустимого отклонения. Если разность больше максимально допустимого отклонения, то импульс U2 после прохождения соответствующего элемента И 19 проходит на выход узла 5 сравнения с допуском, после чего поступает на элемент ИЛИ И. Работа устройства после прохождения импульсом элемента ИЛИ 1 аналогична описанной для первого варианта.

Пятый вариант работы устройства состоит в том, что импульс U1 проходит на выход 21 «Меньше узла 2, а на выходе 24 прямого переноса сумматора 7 существует единичный сигнал. В этом варианте сумматор 7 формирует на своем выходе 25 прямой код разности кодов младших разрядов регистра 1 и блока 3, причем из этой разности вычтена единица младшего разряда. Поскольку узел 2 выдал импульс на выходе «Меньше, то код, который необходимо сравнивать, превышает величину кода младших разрядов блока 3 на 2 , т.е. на выходе 23 сумматора 7 присутствует код, равный А - (Б-2) - 1. Однако этот код можно представить в виде (Б-А) - 1, т. е. на выходе 23 сумматора 7 присутствует обратный код искомой разности Б-А. В данном варианте на выходе 22 «Равно узла 2 присутствует сигнал нулевого уровня, вызывающий нулевой сигнал на выходе элемента И. Поскольку на выходах 20 «Больше узла 2 также присутствует нулевой сигнал, на выходе элемента ИЛИ 10, подключенном к входу переноса сумматора 7, оказывается нулевой сигнал, т. е. увеличение выходного кода сумматора 7 не происходит. На обоих выходах элемента И 18 оказываются единичные сигналы (с выхода 22 «Меньше узла 2 и с выхода 24 прямого переноса сумматора 7). На выходе элемента И 18 оказывается единичный сигнал, который после прохождения элемента ИЛИ 9 попадает на вход инвертирования узла 5 сравнения с допуском,т. е. с допуском сравнивается инвертированный выходной код сумматора 7, равный прямому коду искомой разности Б-А. Если эта разность больше максимально допустимого отклонения, то импульс U2 после прохождения соответствующего эле.мента И 19 проходит на выход узла 5 сравнения с допуском, после чего поступает на элемент ИЛИ 11. Работа устройства после прохождения им- пульсо.м элемента ИЛИ 11 аналогична опи- г санной для первого варианта.

По шестому варианту работы устройства импульс U1 проходит на выход 22 «Равно узла 2, а на выходе 24 прямого переноса сумматора 7 присутствует единичный сигнал. В этом варианте старшие разряды сравни0 ваемых кодов равны, и сумматор 7 выдает на своем выходе 23 истинное значение у.мень- щенного на единицу прямого кода искомой разности А - Б-1. В рассматриваемом варианте на входах элемента И 15 присут5 ствуют единичные сигналы с выхода 22 «Равно узла 2 и с выхода 24 прямого переноса сумматора 7. На выходе элемента И 5 оказывается единичный сигнал, который, пройдя через элемент ИЛИ 10, попадает на вход переноса сумматора 7. Это обеспечивает при0 бавление единицы к коду на выходе 23 сумматора 7: на информационных выходах 23 оказывается точное значение искомого кода разности А-Б. Нулевой сигнал с выхода 21 «Меньше узла 2 вызывает появление нуле5 вого сигнала на выходе элемента И 18. Нулевой сигнал на выходе 25 инверсного переноса сумматора 7 вызывает появление нулевого сигнала на выходе элмента И 17. Таким образом, на обоих входах элемента ИЛИ 9 присутствуют нулевые сигналы и на входе инвер0 тирования узла 5 сравнения с допуском оказывается нулевой сигнал с выхода элемента ИЛИ 9. Это означает, что выходные сигналы сумматора 7 без инвертирования (т. е. прямой код искомой разности А - Б} сравниваются в узле 5 сравнения с допуско.м с

5 максимально допустимым отклонением. Сравнение происходит при подаче импульса U2. Этот импульс проходит соответствующий элемент И 19 и поступает на вход узла 5 .-равнения с допуском. Если разность, сфор0

мированная на выходе 23 сумматора 7, больше максимально допустимого отклонения, то импульс L 2 проходит на выход узла 3 сравнения с допуском и поступает на эле.мент ИЛИ 11. Работа устройства после прохождения импульсом элемента ИЛИ 1 1 ана5 логична описанной для первого варианта. Седьмой вариант работы устройства д.пя обработки и сжатия информации состоит в том, что импульс U1 проходит на выход 22 «Равно узла 2, а на выходе 25 инверсного переноса сумматора 7 присутствует единич0 ный сигнал. В этом варианте старпже разряды сравниваемых кодов равны и сумматор 7 выдает на своих информационных выходах 23 обратный код истинного значения искомой разности (Б-А)- 1. В рассматриваемом варианте нулевой сигнал поступает на вход

элемента И 15 с выхода 24 прямого переноса сумматора 7, т. е. на выходе элемента И 15 оказывается нулевой сигнал, приложенный к входу элемента ИЛИ 10. На втором входе

элемента ИЛИ II) также присутствует нулевой сигнал с выхода 20 «Больше узла 2. Таким образом, с выхода элемента ИЛИ 10 на вход,переноса сумматора 7 подается нулевой сигнал, не сменяющий величины кода на информационных выходах 23 сумматора 7. На обоих входах элемента И 17 оказываются единичные сигналы (с выхода 22 «Равно узла 2 и с выхода 25 инверсного переноса сумматора 7). Иа выходе элемента И 17 по- яв:1яется единичный сшиал, который после прохождения элемента И/111 9 попадает на вход 23 инвертировании уз.ма 5 сравнения с допуском. Это означает, что с величиной максимально допустимого отклонения сравнивается инверсный код с информационных выходов 23 сумматора 7 (т. е. прямой код разности Б-А). Сравнение происходит при ио- даче импульса 12. Этог импульс проходит соответствующий э;1емепт И 19 и поступает па вход узла 5 сранпенин с допуском. Р сли инверсия разпости, сформировапной на выходах 23 сумматора 7 болыпе максимального допустимого отклонения, то и.мпу;1ьс L 2 проходит на выход узла 5 сравнения с допуском и поступает на элемент И II. Работа устройства после 1рохождепия импульсо.м э.чемен- та ИЛИ 1 1 аналогична описанной для пер- BOi O варианта.

Таким образом, рассмотрены все варианты записи cyniecTBeiiHoii выборки на регистр 8 числа. С регистра 8 осун1ествляется передача кодоЕ суп.ественных ))ок на блок 4 буферной памяти, т. е. на блок 4 поступает неравномерный поток существепных выборок из регистра I. Блок 4 предназначен для выравнивания во времени потока суи1ествен- ных выборок, поэтому считывание на выход 29 устройства происходит с равномерной частотой по тактируюпи1м сигналам I 3. Ири каждом считывании содержи.мое реверсивного счетчика 6 запо.чнения уменьп1ается на единицу. Tlpii этом код, хранян1ийся в счетчике 6, чис.ченно равен количеству существенных выборок, записан-ных в блоке 4 и еще не считанных с него. Для считывания инфор.мапии с блока 4 .может быть использован регистр 8 числа или же специальный вспомогательный регистр.

Реверсивный счетчик 6 загголнения в зависимости от числа .чаполненных ячеек в блоке 4 выдает разрешающие единичные сигналы на входы различных элементов И 19. Вследствие этого тактовый импульс U2, по- ступаюпи1Й на все элементы И 19, нроходит через один n.t них на какой-либо тактовый вход узла 5 сравнения с допуском. В зависимости от того, на какой и.менно тактовый вход узла 5 поступает импульс L 2, в узле 5 происходит сравнение с различными максимально допустимыми отклонениями, т. е. величина .максимально допустимого отклонения онределяется числом заполненных ячеек блока 4. Ири этом большему заполпению

соответствуют большие максимально допустимые отклонения.

Изобретение обеспечивает значительное сокращение времени между подключением суп1ественной выборки к входу аналого-цифрового преобразователя измерительной системы и переписью кода этой существенной выборки в блок буферной памяти, что повы- ujaeT быстродействие устройства без увели

чения его аппаратурной сложности. Формула изобретения

0

0

Устройство для обработки и сжатия ин5 формации, содержащее регистр текущей выборки, информационные входы которого являются информационными входами устройства, выходы разрядов подключены к информационным входам блока оперативной памяти и цервым информационным входам ре- |-истра числа, выходы младших разрядов соединены с первыми информационными вхо- да.ми сумматора, вторые информационные входы которого подключены к первому выходу блока оперативной памяти, информа5 иион}1ые выходы сумматора соединены с информационными входами узла сравнения с допуском, выход которого подключен к пер- во.му входу первого элемента ИЛИ, выход которого соединен с суммирующим входом реверсивного счетчика, с тактовым входом

0 блока оперативной памяти и с тактовым входом регистра числа, выход которого является первым выходом устройства, второй выход и второй информационный вход регистра числа соединены соответственно с информационными входом и выходом блока

5 буферной па.мяти, тактовый вход которого объединен с вычитающим входом реверсивного счетчика и является первым тактовым входом устройства, управляющие выходы реверсивного счетчика соединены с первыми входами первых элементов И, вторые входы которых являются вторыми тактовыми входами устройства, выходы реверсивного счетчика соединены с тактовыми входами узла сравнения с допуском, отличающееся тем, что, с целью повышения быстродействия уст5 ройства, в него введены узел сравнения кодов, второй и третий элементы ИЛИ, с второго цо седьмой элементы И и элемент ИЛИ- НЕ, выходы старщих разрядов регистра текущей выборки соединены с первыми информационными входами узла сравнения кодов,

0 вторые информационные входы которого соединены с вторыми выходами блока оперативной памяти, первый выход узла сравнения кодов подключен к первому входу второго элемента И, первому входу второго элемента ИЛИ и к первому входу элемента

5 ИЛИ-ИЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к второму тактовому входу устройства, выход к второму входу пер11

Boro элемента ИЛИ, третий вход которого подключен к выходу второго элемента И, выход прямого переноса сумматора, соединен с первыми входами четвертого и пятого элементов И и вторым входом второго элемента И, второй выход узла сравнения кодов соединен с вторыми входами элемента ИЛИ- НЕ и четвертого элемента И и первым входом шестого элемента И, выход четвертого элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входом переноса сумматора, выход обратного переноса которого соединен с вторым

1381572

12

входом шестого элемента И и первым входом седьмого элемента И, выход которого соединен с четвертым входом первого элемента ИЛИ, третий выход узла сравнения кодов соединен с третьим входом элемента ИЛИ- НЕ и вторыми входами пятого и седьмого элементов И, выходы пятого и ujecToro элементов И соединены с соответствующими входами третьего элемента ИЛИ, выход которого соединен с входом инвертирования узла сравнения с допуском, тактовый вход узла сравнения кодов является третьим тактовым входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки и сжатияиНфОРМАции | 1979 |

|

SU840914A2 |

| Устройство для сокращения избыточности информации | 1986 |

|

SU1372348A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для обработки и сжатия информации | 1974 |

|

SU531158A1 |

| Устройство опроса информационных каналов | 1980 |

|

SU911727A2 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056251A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Адаптивный статистический анализатор | 1980 |

|

SU877564A1 |

| Устройство для поиска чисел в заданном диапазоне | 1981 |

|

SU993250A1 |

Изобретение относится к вычислительной и измерительной технике и может быть использовано в измерительных системах при допусковом контроле или квазиобратимом сжатии. Устройство содержит регистр 1 текущей выборки, специализированный узел сравнения 2, имеющий три выхода «Больше 20, «Меньше 21 и «Равно 22, блок 3 оперативной памяти, сумматор 7, имеющий информационные выходы 23 и выходы прямого 24 и инверсного 25 переносов, регистр 8 числа, реверсивный счетчик 6 заполнения, узел 5 сравнения с допуском, имеющий вход инвертирования, блок 4 буферной памяти. Кроме того, в состав устройства входят элементы И 13-19, ИЛИ 9-11, ИЛИ- НЕ 12. Путем сравнения текущей выборки, находящейся в регистре 1, с информацией на выходе блока 3 оперативной памяти в узле 2 сравнения и сумматоре 7 определяется существенность текущей выборки. Устройство обеспечивает повышение быстродей ствия на 30-40%. 2 ил.

| Устройство для обработки и сжатия информации | 1974 |

|

SU531158A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-09-29—Подача