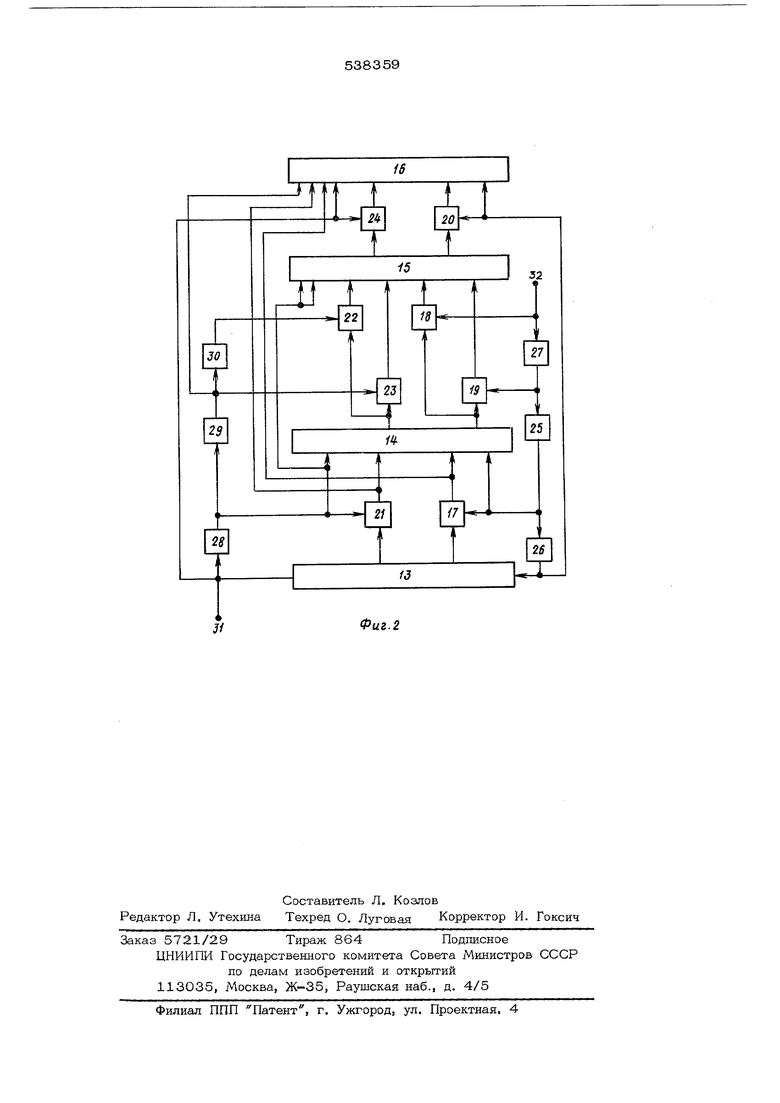

(54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ ДВОИЧНОГО ЧИСЛА В ЧЕТВЕРТУЮ СТЕПЕНЬ Эта цель достигается тем, что в пред ложенном устройстве входная шина соединена с другими входами второй группы элементов И, а через первый элемент задержки, выход которого подключен ко входу второго элемента, с другими входами третьей группы элементов И . Выход второго элемента задержки подключен к другим входам первой группы элементов И и ко второму входу первого сумматор а через третий элемент задержки - кг вхо ду двоичного счетчика, к другим входакх четвертой группы элементов И и ко второму входу третьего сумматора. Выходы первой группы элементов И соединены с третьими входами третьего сумматора. На фиг. 1 дана блок-схема предложенного устройства. Устройство содержит двоичный счетчик 1, сумматоры 2-4, группы элементов И 5-8, элементы задержки 9-11 и входную шину 12. На фиг. 2 дан вариант схемы устройства, предназначенного для возведения в четвертую степень непрерывных функций, представленных последовательностью импул сов. Устройство содержит двоичный реверсивный счетчик 13, сумматоры 14, 15, 16, группы элементов И 17-23 и 24 и элементы задержки 25-3О. Предложенное устройство работает следующим образом. Начальное состояние двоичного счетчика 1 и сумматоров 2-4 нулевое. Каждый импульс, поступивший на входную шину 12, добавляет - в первом такте к содержимому второго сумматора 3 код из первого сумматора 2; во втором такте к содержимому второго сумматора 3 удвоенный (со сдвигом на один разряд влево) код из первого сумматора 2; в третьем такте единицу младшего разряда в первый сумматор 2 и удвоенный (со сдвигом на один разряд влево) код из двоичного счетчгша 1 к содержимому первого сумматора 2 , содержимому третьего сумматора 4; в четвертом тшсте единицу младшего разряда в двоичный счетчик 1 и третий сумматор 4, а также учетверенный (со сдвигом на дьа разряда влево) код из второго сумматора 3 к содержимому третьего сумматора 4. После четырех тактов в первом 2 и третьем 4 сумматорах получается текущее значение кода соответственно квадрата и четвертой степени от последовательности импульсов, поступившей на входную шину 12. Работа устройства иллюстрируется табицей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения двоичного числа в четвертную степень | 1976 |

|

SU595728A1 |

| Устройство для возведения двоичных чисел в степень | 1974 |

|

SU541168A1 |

| Устройство для возведения в куб | 1985 |

|

SU1257640A1 |

| Устройство для извлечения корня третьей степени | 1974 |

|

SU551641A1 |

| Устройство для возведения в степень | 1987 |

|

SU1499338A1 |

| Устройство для возведения в степень | 1976 |

|

SU888106A1 |

| Устройство для возведения двоичных чисел в третью степень | 1974 |

|

SU491129A1 |

| Устройство для возведения в куб | 1979 |

|

SU868755A1 |

| Устройство для вычисления @ , @ , @ аргумента,заданного параллельным и число-импульсным кодом | 1980 |

|

SU999047A1 |

| Устройство для возведения двоичных чисел в третью степень | 1978 |

|

SU746505A2 |

О

1 2

3

4

+1

четырех тактов

1

О

О

+(0x1) +(0x2)

X 2)

+(0 X 2) +1+(0 X 41

О 1

1 2 3 4

+ 1 2

четырех тактов 1

После четырех тактов4

Работа устройства для возведения в

четвертую степень непрерывных функхшй, представленных последовательностью импульсов, аналогична работе устройства описанного выше. При этом последовательность испульсов x(t)подается на вход 31, а на вход 32 поступает последовательность импульсов yCt) . Устройство осущесляет вычисление текущих значений фунлиии 2Ct)xltl - yitl 1 Такое устройство может бытъ использовано, например, в функциональном аналого-цифровом преобразователе cлeдJющeгo типа для возведения в четвертую степень непрерывных функций с получением результата в цифровой виде.

Предложенное устройство по сравнению с известными имеет меньший объем оборудования и большое быстродействие, так как в предложенном устройстве частота подачи входных импульсов определяется

в

Продолжение таблицы

+(1 X 1) +(1 X 2)

+(1x2)

X 2) +1+(3 X 4) 16

3

+(4 X 1) +(4 X 2)

256

42

16

о1 /

величиной у (где Т - время сложения сумматора) и не зависит от величины аргумента. Например, в прототипе на входную шину устройства нельзя подавать очередной импульс до тех пор, пока генератор импульсов не выдаст число импульсов, определяемое величиной X - - ) j , а частота подачи импульсов не превышает величины 1/2 , где -максимальное значение аргумента, выраженное числом импульсов, т. е. выигрыш по быстродействию равен гх / 5 ,

Формула изобретения

Устройство для возведения двоичного числа в четвертую степень, содержашее элементы задержки, двоичный счетчик, выходы которого через первую группу элементов И соединены со входами пеового через вторую сумматора, входы которого и третью группу элементов И подключены ко входам второго сумматора, выходы которого через четвертую группу элеме тов И соединены со входами третьего сумматора, отличающееся тем, что,с целью упрощения устройства и повышения быстродействия, в нем входная шина соединена с другими входами второй группы элементов И, а через первый элемент задержки, выход которого подклю чен ко входу второго элемента задержки, к другим входам третьей группы элементов выход второго элемента задержки подключен к другим входам первой группы элементов И и ко второму входу первого сумматора, а через третий элемен задержки - ко входу двоичного счетчика, к другим входам четвертой группы элементов И и ко второму входу третьего сумматора, а выходы первой группы элементов И соединены с третьими входами третьего сумматора. Источники информации, принятые во внимание при экспертизе: 1.Воронов А. А. и др. Цифровые анаглоги для систем автоматического управления, изд. АН СССР, М, 1960, стр.100 2. Автоматизация производства и промышленная электроника изд. Сов. энциклопедия, М, 1962, т, 1, стр. 476 3.Авторское свидетельство СССР № 290279, Q06 F 7/52, от 15.05. 69 г. 4.Авторское свидетельство СССР 151118, QO6 F 7/38.

i5

32

iS

26

л:

13

j/

Фиг.2

Авторы

Даты

1976-12-05—Публикация

1974-02-01—Подача