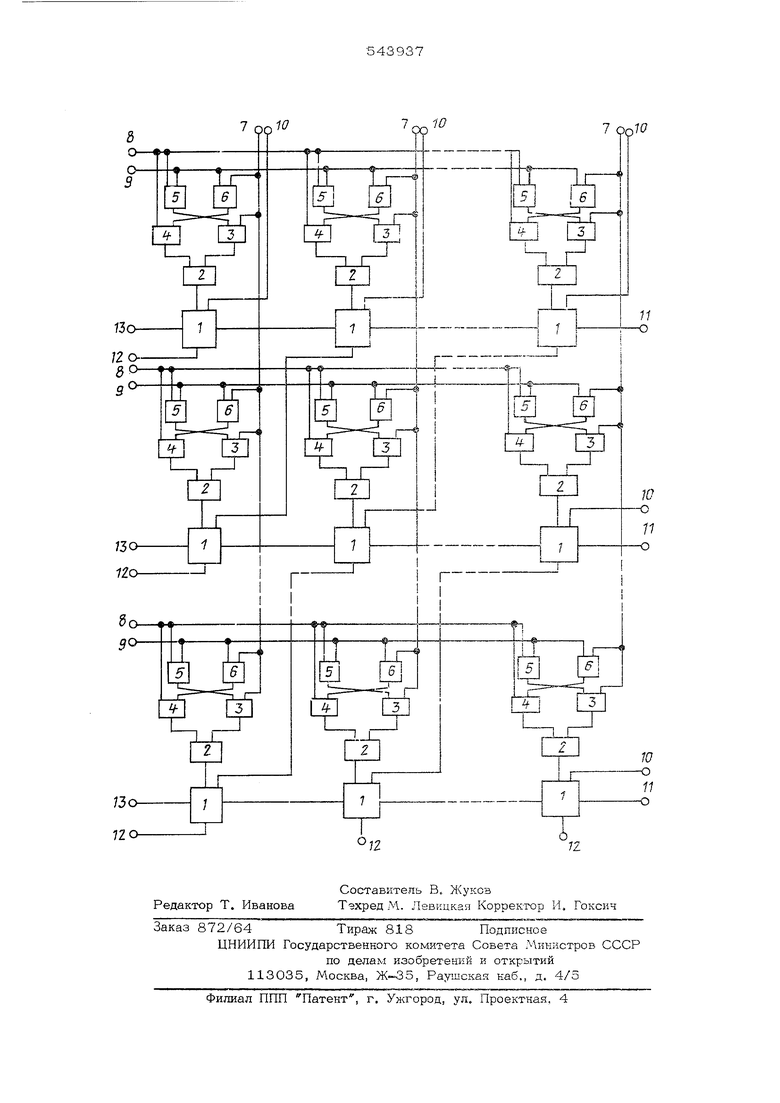

Изобретение относится к цифровой вычислительной технике и предназначено для использования в электронных вычислительны машинах и быстродействующих процессорах. Известно матричное устройство умножения, содержащее матрицу умножения, регистры множимого и множителя р. . Однак такие устройства обладают большой аппаратурной избыточностью и не могут выполнять другие арифметические операции. Наиболее близким по техническому решению к предложенному является устройство, содержащее в каждой ячейке одноразрядный сумматор, один вход которого подключен через элемент ИЛИ к выходам двух элементов И; выход одноразрядного суммато ра -i -чзтроки и j -столбца матриць подключен к одному из входов однора1зрядного сумматора ( + 1)-строки и (j l)- столбца матрицы, и шины уЬравлешод Г2. Однако такое устройство не может выполнять операции сложения и вычитания и имеет недостаточную модульность структуру по краям матрицы. Цель изобретения - расширение функциональных возможностей. Эта цель достигается тем, что устройство содержит в каждой ячейке по два сумматора по модулю два, первые входы которых в каждой строке матрицы подключены к первой шине управления, вторые входы первого сумматора по модулю два в каждой строке матрицы подключены ко второй шине управления и к одному из входов первого элемента И, вторые входы вторых сумматоров по модулю два в каждом столбце матрицы подключены к одному из входов второго элемента И и к входу устройства, выходы сумматоров по модулю два подключены к другим входам соответствующих элементов И. На чертеже показана схема устройства. Устройство содержит одноразрядные сук маторы 1, элементы ИЛИ 2, элементы И 3 и 4, сумматоры 5 и 6 по модулю два, шины управления 8 и 9, входные 7, 1О и 11 и выходные 12 и 13 шины. Работа устройства начинается с подачи на его входы кодов настройки и операнндов. выполнении операции деления сигнал с инверсного выхода 12 каждой предыдущей строки подается на входы 9 и 11 предыдущей строки. При выполнении умножения результаты с выходов 13 первых сумматоров каждой строки, кроме первого сумматора первой строки, подаются на входы 10 первой строки, т.е. результат с выхода 13 второй строки подается на вход 10 первого сумматора первой строки результат с выхода 13 третьей строки на вход 10 сумматора первой строки и т.д.

Операнды при сложении подаются на Входы 8 и 10, код настройки на входы 8 и 9. При этом в разряды матрицы, расположенные в первой строке, на входы 8 и 9 подаются коды 1 и О, соответственно, а на остальные входы 8 и 9 коды О. Таким образом, результат сложения образуется на выходах сумматоров первой строки. Сигнал переноса распространяется от младщего разряда к старшему. Так как на входы 8 и 9 подаются коды О, то результат без изменения передается на выходы 12 первого столбца матрицы. Операция вычитания выполняется подачей на входы 8 и 9 первой строки кодов 1 и 1, а на входы 8 и 9 следующих строк - кодов Q .Так как вход 9 в операциях сложения и вычитания не участвует в качестве информационного, для упрощения логической группы схем 2-6 этот вход используется в качестве дополнительного входа настройки для выполнения операций сложения и вычитания. Преложенное устройство обладает более широкими функциональными возможностями, что

достигнуто введением в него сумматоров по модулю два и новой организацией связей.

Формула изобретения

Матричное операционное устройство, содержащее в каждой ячейке одноразрядный сумматор, один вход которого подключен

через элемент ИЛИ к выходам двух элемен тов И, выход одноразрядного сумматора i-строки и 4 -столбца матрицы подключен к одному из входов одноразрядного сумматора ( 1 + 1)- :троки и ( --1).ч:тобЦа матринь шины управления, отличающееся тем, что, с целью расщирения функциональных возможностей, устройство содержит в каждой ячейке по два сумматора по модулю два, первые входы которых в каждой строке матрицы подключены к первой шине управления, вторые входы первого сумматора по модулю два в каждой строке матрицы подключены ко второй шине управления и к одному из входов пер-

вого элемента И, вторые входы вторых

сумматоров по модулю два в каждом столбце матрицы подключены к одному из входов второго элемента И и к входу устройства, выходы сумматоров по модулю два

подключены к другим входам соответствующих элементов И.

Источники информации, принятые во внимание при экспертизе:

1.Патент Франции К 2098559, кл. G06 Р 7/00, 1972.

2.Авторское свидетельство СССР № 360663, М.Кл. G 06 F 7/52, 1972 (прототип).

.10

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1978 |

|

SU750484A1 |

| Арифметическое устройство | 1976 |

|

SU650074A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750485A1 |

| Матричное вычислительное устройство | 1990 |

|

SU1833890A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Матричное вычислительное устройство | 1981 |

|

SU960803A1 |

Авторы

Даты

1977-01-25—Публикация

1975-01-03—Подача