кой единицы устройства, вход переноса п -го сумматора формирователя кода дополнения подключен к выходу переноса (h+1)-ro сумматора выход переноса первого сумматора формирователя кода дополнения подключен к первому входу элемента ШШ устройства,- выходы суммы сумматоров формирователя кода дополнения подключены соответственно к первьм входам коммутаторов первой группы, вторые входьГ которых подключены соответственно к первой группе младших разрядных входов устройства, управляющий вход режима р.аботы которого подключен к третьим входам коммутаторов первой группы, к первьм входам коммутаторов второй группы, к первым входам коммутаторов и.элементов И узла коррек ции, к первому входу элемента И устройства, второй вход которого подключен к старшему разрядному входу первых входов устройства и первому входу первого элемента ИСКЛЮЧАЮЩЕЕ №Ш первой группы, второй вход которого подключен к выходу первого элемента НЕ группы элементов НЕ, входы которых подключены соответственно к вторым разрядным входам устройства старший из второй группы разрядных входов которого подключен к второму вхо первого коммутатора второй группы коммутаторов, третий вход которого подключен к выходу первого элемента ИСКЛЮЧАКЛЩЕ ШШ первой группы, выход элемента И устройства подключен к первым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы кото рых подключены соответственно к входу (,3,...,N) вторых разрядных входов устройства, выход |( -го элемента ИСЮЮЧАЮЩЕЕ ИЛИ второй группы подключен к второму входу сумматора К-и вычислительной ячейки (,2,,..,N-1) первой строки матри|цы, выход К-го коммутатора (Х 1, 2,...,Н).первой группы подключен к второму входу, сумматора К -и вычис- . лительной (К-1,2,... ,Н) последнего столбца матрищ 1, выход К-го коммутатора второй группы подклк)чен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ШШ k-и вычислительной ячейки (,2,....,М) первого столбца матрицы, выход переноса сумматора К -и вычислительной ячейки (,2,...,N)

первого столбца матрицы подключен соответственно к первому входу ti-ro элемента (,3,.. , ,N + 1) ИСКПЮЧАЩЕЕ ИЛИ первой группы, второй вход .которого подключен соответственно к второму входу элемента ИСКЛЮЧАЮЩЕЕ ШШ П -и вычислительной ячейки первого столбца матрицы, выход -го элемента (,3,...,N) ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы подключен к третьему входу соответственно -го коммутатора (,3,.. .,N) второй группы и второму входу П-го коммутатора (,3,... ,N) узла коррекции, третьи входы коммутаторов которого подключены соответственно к выходам суммы сумматоров К -и вычислительной ячейки (,2,,,., N-1) первого столбца матрицы, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ М-йвычислительной ячейки первого столбца матрицы подключен к второму входу элемента ИЛИ, выход которого подключен к второму входу (N + O-ro коммутатора узла коррекции, третий вход которого подключен .к выходу (N+1)-ro элемента ИСКЛЮЧАЮЩЕЕ ШШ первой группы, выход первого.элемента ИСКЛЮЧАЩЕЕ ШШ которой подключен к второму входу первого ко.ммутатора узла коррекции и входу элемента НЕ, выход которого подключен к третьему входу первого коммутатора узла коррекции, выход (К+1)-го коммутатора которого подключен к входу переноса N -го одноразрядного сумматора узла -коррекции, второй вход К-го элемента И (,2,...,N) которого подключен соответственно к выходу переноса сумматора X -и вычислительной ячейки (К 1,2,...,1) первого столбца матрицы, выходы элементов И узла коррекции подключены соответственно к пераым входам сумматоров узла коррекции, -вторые входы которых подключены, соответственно к выходу К -го коммутатора (,2,...,М) узла коррекции, вход переноса К -го сумматора которого

(,2,.,.,Ц-1) подключен соответственно к выходу переноса И .-го сумматора (,3,...,M), выход k -го

сумматора (K 1,2,...,N) Узла коррекции подключен соответственно к

К-му выходу старших разрядных выходов устройства. Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах и ЭВМ для однотактного вып.олнения операции деления и умножения над целыми и дробг ными двоичными числами, представленных в дополнительных кодах, Известно вычислительное устройство для деления, содержащее матрицу вычислительных ячеек из М строк и N столбцов (где N - разрядность операндов) и реализующее алгоритмы деления по методу без восстановле- вид остатка, причем каждая ячейка . включает элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и одноразрядный сумматор l. Недостаток известного устройства заключается в отсутствии возможност вьтолнения операции умножения и ограниченности функциональных возможностей за счет выполнения делени лишь в прямых кодах. Целью изобретенияявляется расши рение функциональных возможностей . устройства за счет выполнения на нем операций деления и умножения в дополнительных кодах. Поставленная цель.достигается тем что в вычислительное устройство содержащее матрицу вычислительных ячеек размерности Н N , -где N - ра .рядность .операторов, причем каждая вычислительная ячейка матрицы содержит одноразрядный сумматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход кото рого подключен к первому входу одноразрядного сумматора, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ П -и вычислительной ячейки (,3, .. ., N) каждой строки матрицы подключен к первому входу элемента ИСЮЮЧАЮЩЕЕИЛИ (П-1) вычислительной ячейки этой же строки матрицы, второй вход элемента ИСКЛЮЧАМ)1ЕЕ ИЛИ П -и вычислительной ячейки (,3,...,N) каждого столбца матрицы подключен к второму выходу элемента ИСКЛЮЧАКЩЕЕ ИЛИ (h-1)-и ячейки этого же столбца матрицы, вход переноса сумматора К -и вычислительной .ячейки (,2,..., N-1) каждой строки матрицыподключён .к выходу переноса сумматора (К+1)-йвычислительной ячейки этой же строки матрицы, второй вход сумматора каждои вычислительной ячейки п й строки (,3,...,N) и К -го столбца матрицы (k 1,2,... ,N-1) подключен к 972 выходу суммы вычислительной ячейки сумматора соответственно предыдущей строки и последующего столбца матрицы, второй вход элемента ИСКЛЮЧАНЩЕЕ ИЛИ К -и вычислительной ячейки (,2,...,N) первой строки матрицы подключен соответственно к 1C -му входу первой группы старших разрядных входов устройства, выходы суммы сумматрров вычислительных ячеек последней строки матрицы подключены соответственно к младшим разрядным выходам устройства, дополнитель.но введены две группы из М коммутаторов каждая, первая группа из (N+1)го и вторая группа из (N-l)-ro элементов ИСКЛЮЧАЮЩЕЕ ШШ, группа из У элементов НЕ, элемент ИЛИ, элемент И, элемент НЕ, узел коррекции, состоящий из-N одноразрядных сумматоров, N элементов И и (N+1)-ro коммутатора, и формирователь кода дополнения, состоящий из N элементов НЕ и одноразрядных сумматоров, причем первые входы сумматоров формирователя кода дополнения подключены к шине логического .нуля устройства, а вторые входы сумматоров подключены соответственно к выходам элементов НЕ формирователя кода дополнения, входы которых подключены соотв1етственно к первой группе старших разрядных .входов устройства, вход переноса сумматора младщего разряда формирователя кода дополнения подключен к. шине логической единицы.устройства, вход переноса П -го сумматора формирователя кода дополнения подключен к выходу переноса (п+1)-го сумматора, выход переноса первого сумматора формирователя кода дополнения подключен к первому входу элемента ИЛИ устройства, выходы суммы сумматоров формирователя кода дополнения подключены соответственно к первьм входам коммутаторов первой группы, вторые входы которых подключены соответственно к пер- . вой группе младших разрядных входов устройства, управляющий вход режима работы которого подключен к третьим входам коммутаторов первой группы, к первьм входам коммутаторов второй группы, к первым входам коммутаторо.в и элементов И узла коррекции, к первому входу элемента И устройства, второй вход которого подключен к старшему разрядному входу первых входов устройства и первому входу

первого элемента ИСКЛЮ 1АЩЕЕ ШШ первой группы, второй вход которого подключен к выходу первого элемента НЕ группы элементов НЕ, входы которых подключены соответственно к вторым разрядным входам устройства, старший из второй группы разрядных входов которого подключен к второму входу первого коммутатора.второй группы коммутаторов, третий вxq которого-подключен к выходу.первого элемента ИСКЛЮЧАМЦЕЕ ШШ первой группы, выход элемента И устройства подключен к первьпм входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторы входы которых подключены соответственно к )1 -ку входу (,3,...., N) BTopbix разрядных входов устройства, выход k -го элемента .ИСКЛЮЧАЮЩЕЕ ИЛИ .второй группы подключен к второму входу сумматора К -ивычислительной ячейки (,2,...,М-1) первой строки матрицы,, выход К -го коммутатора (К-1,2,...,М) первой группы подключен к- второму вход5 сумматора вычислительной ячейки (К 1,2,... N) последнего столбца матрицы, выход X -го коммутатора второй группы подключен к первому входу -элемента ИСКЛЮЧАЮЩЕЕ ИЛИ К -и.вычислительной ячейки (,...,N) первого столбца матрицы, выход переноса сумм.атора 1с-и вычислительной ячейки (К 1,2,... N) первого столбца матрицы подключен соответственно к первому входу И -го элемента ( ,3,... ,Н -И) ИСЮЮЧАЮЩЕЕ ЩИ первой группы, второй вход ко- . .торого подключен соответственно к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ ц -и вычислительной ячейки первого столбца матрицы, выход П -го элемента ,3,...,N) ИСКЛЮЧАВДЕЕ ИЛИ первой группы подключен к третьему входу соответственно И -го коммутатора (,3,... ,N) второй группы и второму входу h-го коммутатора (,.,.,N) узла коррекции, третьи входы коммутаторов которого подключены соответственно к выходам суммы сумматоров К -и вычислительной .ячейки (,2,...,N-1) первого столбца матрицы, второй, вход элемента ИСКЛЮЧАЩЕЕ ИЛИ N -и вычислительной ячей ки первого столбца матрицы подключён к второму входу элемента ИЛИ, выход которого.подключен к второму входу )-го коммутатора узла коррекции, третий вход которого подключен к выходу (N+1)-ro элемента ИСКЛЮЧАНМЦЕЕ ИЛИ первой группы, выход первого . элемента ИСКЛЮЧАК)ЩЕЕ ИЛИ которой подключен к второму входу первого коммутатора узла коррекции и входу элемента НЕ, втькод которого подключен к третьему входу первого коммутатора узла коррекции, выход (N+1)-rp коммутатора которого подключен к входу переноса N -го одно,разрядного сумматора узла коррекции, .второй вхоК-го элемента И (,2,..,,N) которого подключен соответственно, к выходу переноса сумматора К- -и вычислительной ячейки (,2,... ,N) -первого столбца матриць.1, выходы элементов И

|узла коррекции подключены соответственно к первым входам сумматоров

.узлакоррекции, вторые входы которых подключены соответственно- к выходу К -гокоммутатора (К 1.,2,..., N) узла коррекции, вход переноса

.К-го сумматора которого (k 1,2,..., N-I) .подключен соответственно к выходу переноса п -го сумматора (,3... ,./V) ,вьгход |( -го сумматора (,2,...,N) узла коррекции подключен соответственно к К -му выходу старших разрядных выходов устройства:.

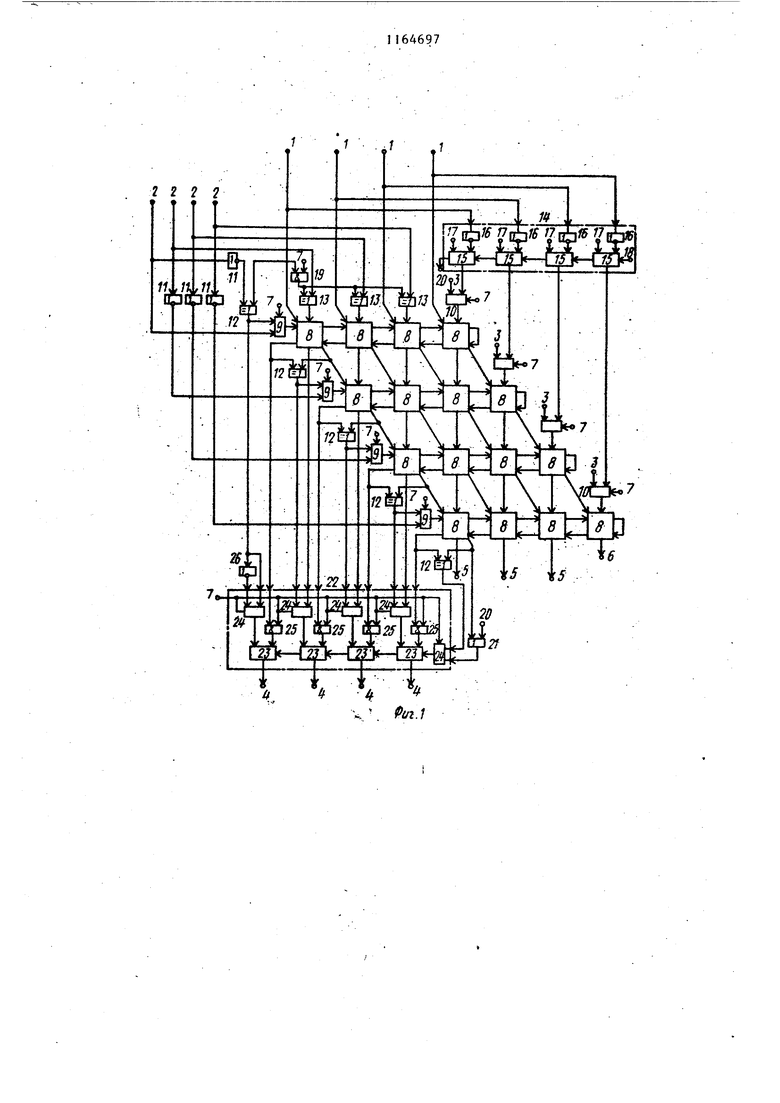

На фиг.1 приведена структурная схема пре длагаемого устройства, на фиг.2 - функциональная схема ячейки . .. .. ..

Устройство для.деления и умножения (фиг. 1) содержит первые входы t устройства, на которые подают код делителя или множимого., вторые входы 2 устройства, на которые-подают старшие разряды -кода делимого или код множителя, .третьи входы 3 устройства, на которые подаю.т младшие разряды кода делимого,. первью выходы 4 устройства, на которых формируются старшие разряды кода произведения или код частного, вторые выходы 5 -устройства,, на которых формируются младшие разряды кода произведения или код остатка, выход 6 младшего разряда остатка, входы 7 управления ус-тройства, ячейки 8, коммутаторы 9 и 10 соответственно первого и второго столбца коммутаторов, строку инверторов 11, столбец 12 и строку 13 элементов ИСКЛЮЧАЮЩЕЕ ШШ, формирователь 14 кода дополнения, который изменяет знак кода множимого на противоположный, одноразрядные сумматоры 15 формирователя, инверторы 16 формирователя, входы 17, на которые подают константные сигналы нулевого уровня, и вход 18, на которьй подают 5 сигнал единичного уровня, элемент И 19, выход 20 формирователя, который электрически связан с входом элемента Ш1Й 21, узел 22 коррекции, одноразрядньде сумматоры 23 узла, строка О коммутаторов 24 узла, cfрока элементов И 25 узла, инвертор 26,

Каждая ячейка 8 (фиг.2) содержит одноразрядньй сумматор 27, элемент ИСКЛЮЧАКЛЦЕЕ ИЛИ 28, первый вход 29, 15 нторой вход 30, вход 31 суммы, вход 32 переноса, первый выход 33, второй выход 34, выход 35 суммы, вькод 36 перенос.а. . .

.Номера строк матрицы возрастают 20 сверху вниз, а столбцов - слева направо, номера элементрв узла 22 коррекции и формирователя 14 возрастают слева направо .

Первые входы коммутаторов 9 подключены к выходам элементов 12 ИСКЛЮЧАЩЕЕ ШШ, .а вторые входы - к выходам инверторов 11. Первые входы коммутаторов 1.0 подключены к входам 3 устройства, а вторые - к соответ- 30 ствующим выходам формирователя 14. Первые входы коммутаторов 24, за исключением первого и (Н+ 1)0, подключены к выходам элементов 12 ИСКЛКЬ ЧАЮЩЕЕ ШШ, а вторые входы этих ком- 35 мутаторов - к выходам суммы ячеек 8 . первого столбца; первый вход (№+1)-:го коммутатора 24 подключен к выходу элемента .12 ИСКПЮЧАКЩЕЕ ИЛИ, а в.торой - к выходу элемента ИЛИ 21,. пер- 40 вый вход первого коммутатора 24 подключен к выходу, а второй к входу инвертора 26. Все коммутаторы работают так, что , если на входах управения 7 присутствует сигнал нулево- 45 го. уровня, то к выходам подключаютсяпервые входы, а если единичного.. уровня.- то вторые входы. .

Сигнал нулевого уровня на входе 7 . управления устройства настраивает на 50 вьшолнение операции деления, а сигнал единичного - на выполнение операции умножения.

Предлагаемре устройство работает следз щим .образом..55

Деление в устройстве выполняется по методу деления без восст.ановления остатка в дополнительных кодах.

Настройка на деление осуществляется подачей на вход управления 7 сигнала нулевого уровня; при этом (2Ы-1)-разрядное делимое через элементы ИСКЛЮЧАЮЩЕЕ 1ШИ 13, которые здесь выполняют функции логических повторителей , и через первые входы коммутаторов 10 поступают на входы ячеек 8 1-й строки N -го столбца. ,.

Де.лит.ель- в N .разрядов подают через входы 1 устройства на вторые входы ячеек. 8 1-й строки. Знаковые разряды кодов операндов расположеныперед старшими разрядами, мантисс кодов (на фиг. 1 знаковые р.азряды отделены от остальной части кода запятыми).Считается, что по абсолютной величине делитель больше . делимого. Исход.я из этого, делимое вступает в операцию по отношению . к делителю со сдвигом на разряд в сторону старших разрядов. Если знак очередного остатка (делимое считают нулевым остатком) совпадает со знаком делителя,, то из сдвинутого на разряд влево очередного остатка вычитается делитель, в противном случае делитель суммируется с ним. Вычитание осуществляется. изме.нениём знака у кода делителя на противоположный за счет имеющихся в ячейках 8 элементов ИСКЛЮЧАЮЩЕЕ .ШШ 28 и электрической связи выхода 33 с выходом 32 ячеек N -го столбца. Так элементы И 25 узла коррекции 22 закрыты сигналом нулевого.уровня то на сумматоры 23 поступают разряд знака частного, выработанного элементами 11, 12 и 25, и разряды мантиссы, формируемые соответствующими элементами ИСКгаОЧАЩЕЕ-ИЛИ 12. В силу того, что деление в дополнительных кодах требует коррекции результата., то, следуя одному из правил коррекции, -к вычисленному N разрядному коду подсуммируется (N+1)-я цифра частного, дополнительно сформированная; М -и строкой мат рицы ячеек.

Умножение в устройстве осуществляется старшими разрядами вперед со сдвигом частичных произведений вправо. С целью максимального использования элементов матрицы, уже реализующей операцию деления для выполнения операции умножения, формирование частичных произведений в устройстве осуществляется путем умножения кода множимого В на код множителя А, цифры которого представлены в той же двоичной системе, но с цифрами (-1, +1). Причем цифра -1 кодируется сигналом единичного уровня, а цифра +1 - сигналом нулевого уровня Каждое частичное произведение в этом случае или прямо равно множимому В, или ему же, но с противоположным знаком, т.е. (-В).Так как множимое В в устройстве выражается цифрами (0,1), то и произведение на выходах представлено в том же алфавите. Простота перевода в систему с цифрами (-1, 1) позволяет выполнить это преобразование в процессе вычисления произведения. Для представления множителя А в новом алфавите используется согласно известным способам представления двоичная система счисления с искусственным весовым членом. , / -2-i-2-« 4i.-tvtr где а, - цифра множителя, равная -1 или +i; разрядность кода А, предст ленного двоичной дробью} ()множитель А соответственно в системе с цифрами (0,1) и (-1, +1). Причем цифры множителя AJ.,J определяются через вспомогательный код (0.1 Г . r2V(Ao, +1), если А О (о,1)|2 (А(о,,-1), если AiO В коде ,J все логические нули заменяют на -1, а единицы оставляют н«и.зменними. Произведение в устройстве вычисл . ется по следующей Формуле: , N . С-(-В)2 +С Z:a;.B.2-VK , (2) -н . где (-В) 2 - дополнение от Б, т.е В с противоположным знаком, получаемое на 8. выходах формирователя 14 и суммируемое со сдвигом на N разрядов, вправо, 0 нулевая сумма, равная подразрядному дополнению цифр множителя А . до знакового разряда множимого В , знак С равен код С/, формируется с помощью элементов 13, инвертором 11 и 1-м элементом 12; а: В-2 частичное произведение множимого на множитель в системе ( -1, +1), сдвин утое на 1 разрядов вправо, формируемое в строках ячеек 8 по значению сигнала на выходе соответствующего инвертора 11 j корректирующий член, равный знайовому разряду множимого.В, объединенного в логичес; кое ИЛИ с переносом, : возникающим на выходе 20 формирователя 14. ормула (2) получена в результате жения В на множитель А/.л выраый формулой (1). ри умножении (на входе 7 сигнал ичного уровня) работают вторые ы коммутаторов 9, 10 и 24, оты все элементы И. В узле коррекосуществляется суммирование перев и информационных битов, формиихся на выходах переносов и сумм к 1-го, столбца. Результат произния в дополнительном коде снимас выходов 5 и 4 устройства, .аким образом, предлагаемое устт о позволяет выполнить в одном oйcтjвe умножение и деление в доительных кодах, что расширяет .функциональные возможности. J 2222 ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее матрицу вычислительных ячеек размерности N N , где N разрядность операторов, причем каждая вычислительная ячейка матрицы содержит одноразрядный сумматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому входу одноразрядного сумматора, первый вход элемента ИСЮШЧАЮЦЕЕ ИЛИ п -и вычислительной ячейки (,3,...,N) каждой строки матрицы подключен к : первому входу элемента ИСКЛЮЧАКЙЦЕЕ ИЛИ ()й вычислительной ячейки этой же строки матрицы, второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ П -и вычислительной ячейки (,3,...,W) кажг дого столбца матрицы подключен к второму выходу элемента ИСЮЛОЧАЮЩЕЕ ИЛИ (п-1)-й ячейки этого же столбца матрицы, вход переноса сумматора К-й вычислительной ячейки (,2,..., N-1) каждой строки матрицы подключен к выходу переноса сумматора (К+1)-й вычислительной ячейки этой же строки матрицы, второй вход сумматора каждой вычислительной ячейки h-й строки (,3,. .. ,N) .и (-го столбца матрицы (,,2, ... ,Н-1) подключен к выходу суммы вычислительной ячейки сумматора соответственно предь|дущей строки и последующего столбца матрицы, второй вход э,лемента ИСКЛЮЧАЮЩЕЕ ИЛИ .К-и вычислительной .ячейки (,2,...,N) первой строки матрицы подключен соответственно к К му входу первой группы старших разрядных входов устройства, выходы суммы сумматоров вычислительных ячеек последними строки матрицы подключены соответственно к младшим разрядным выходам устройства, отличающееся тем, -что, с целью расширения его функциональных возможностей за счет выполнения операций деСО ления и умножения в дополнительных кодах, в устройство введены две группы из N коммутаторов каждая, первая группа из (N+1)-го и вторая ,группа из (N-I)-TO элементов ИСКЛЮЧАМЦЕЕ ШШ, группа из N элементов НЕ, элемент ИЛИ, элемент И, .элемент НЕ, узел коррекции, состоящий из N Oi одноразрядных сумматоров, N элемен4ik тов И и (N+1)-ro коммутатора, и фора мирователь кода дополнения, состоя;о .щий из N элементов НЕ и одноразрядных сумматоров, причем первые входы i сумматоров формирователя кода дополнения подключены к шине логического нуля устройства, а вторые входы сумматоров подключены соответственно к выходам элементов НЕ формирователя кода дополнения, входы которых подключены соответственно к первой группе старших разрядных входов устройства, вход переноса сумматора младшего разряда формирователя кода дополнения подключен к шине логичес

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А., Брик В.А | |||

| Вычислительные системы и синхронг ная арифметика | |||

| М., Радио и связь,, 1981, с | |||

| Ручная тележка для грузов, превращаемая в сани | 1920 |

|

SU238A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-06-30—Публикация

1982-05-21—Подача