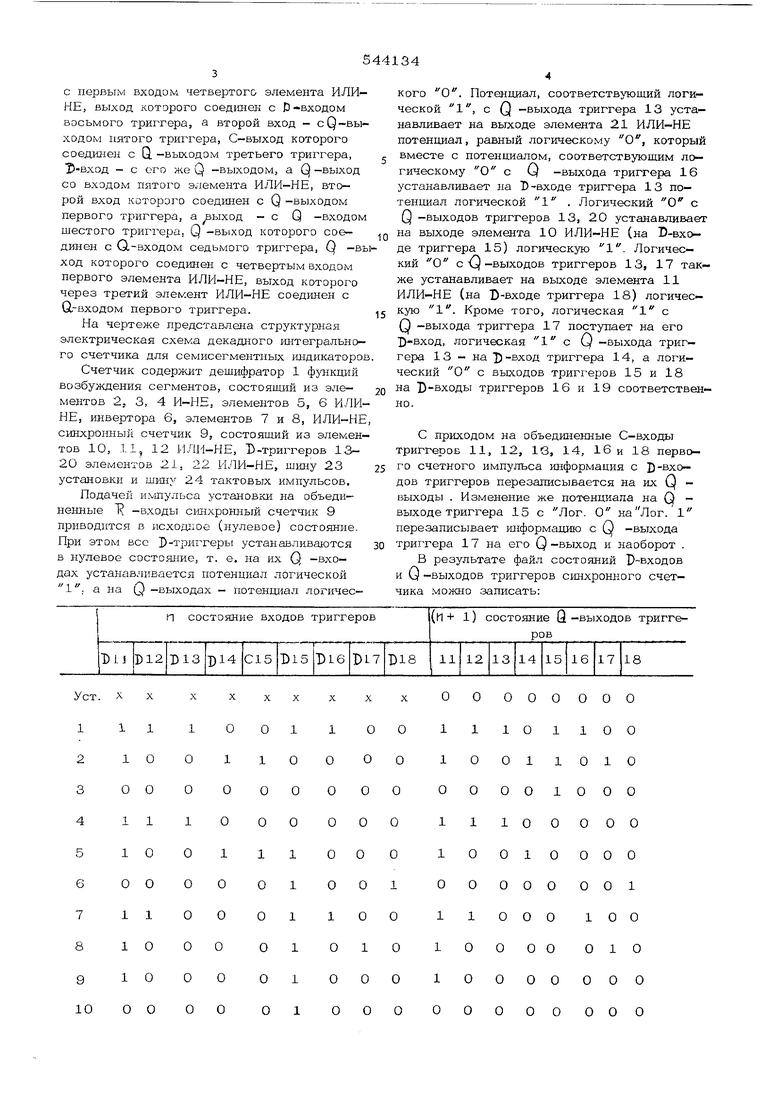

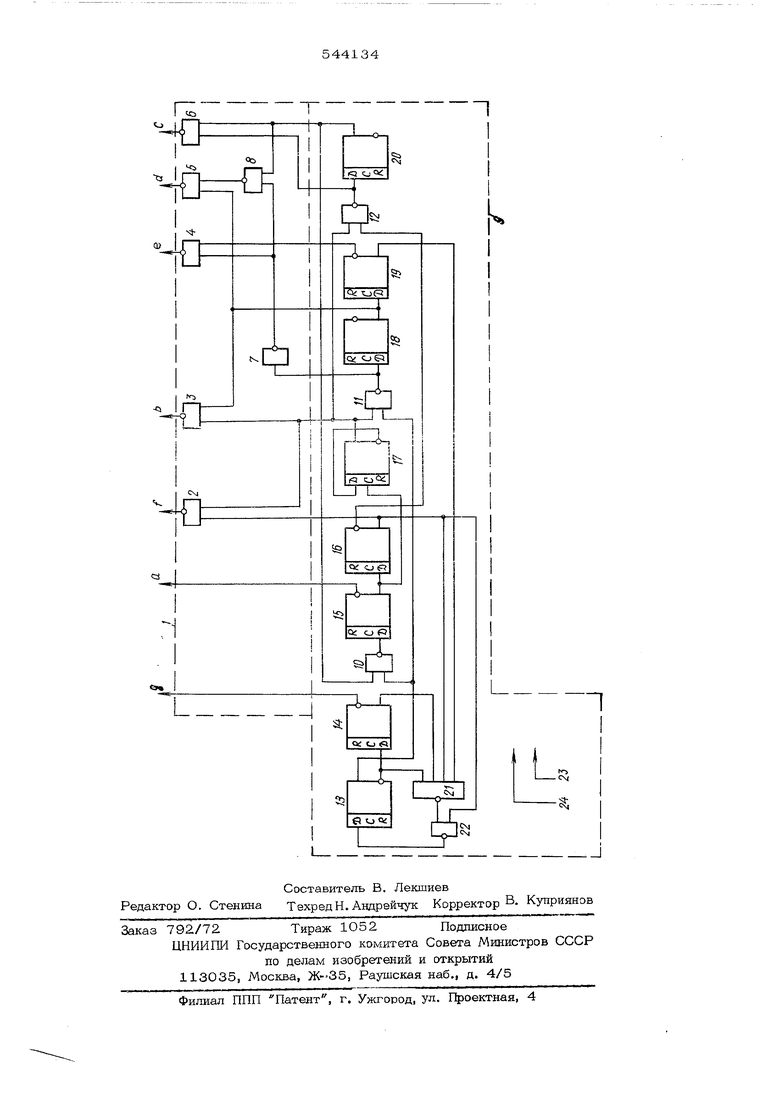

с первым входом четвертого элемента ИЛИ- НЕ, выход которого соед1шек с D-входом восьмого триггера, а второй вход - с Q-выходом пятого триггера, С-выход которого соединен с Q. -выходом третьего триггера, вход - с его же Q -выходом, а Q -выход со входом пятого элемента ИЛИ-НЕ, второй вход которого соединен с Q -выходом первого триггера, а выход - с Q -входом шестого триггера. Q -выход которого соединен с О,-входом седьмого триггера, Q -в ход которого соединен с четвертым входом первого элемента ИЛИ-НЕ, выход которого через третий элемент ИЛИ-НЕ соединен с Q-входом первого триггера. На чертеже представлена структурная электрическая схема декадного интегрального счетчика для семисегментных шдикаторо Счетчик содержит дешифратор 1 функций возбуждения сегментов, состоящий из элементов 2, 3, 4 И-НН, элементов 5, 6 ИЛИ НЕ, инвертора 6, элементов 7 и 8, ИЛИ-НЕ синхронный счетчик 9, состоящий из элемен тов 10, 11, 12 ИЛИ-НЕ, D-триггеров 1320 элементов 21, 22 ИЛИ-НЕ, щину 23 установки и шину 24 тактовых импульсов. Подачей импульса установки на объединенные 1 -входы синхронный счетчик 9 приводится в исходное (нулевое) состо5шие. При этом все D-триггеры устанавливаются в нулевое состояние, т. е. на их Q -входах устанавливается потенциал логической а на Q -выходах - потенциал логичес- кого О. Потенциал, соответствующий логической 1, с Q -выхода триггера 13 устанавливает на выходе элемента 21 ИЛИ-НЕ потенциал, равный логическому О, который вместе с потенциалом, соответствующим логическому О с Q -выхода триггера 16 устанавливает на D -входе триггера 13 потенциал логической 1 . Логический О с Q -выходов триггеров 13, 20 устанавливает на выходе элемента 10 ИЛИ-НЕ (на С-вхо- де триггера 15) логическую 1. Логический О с {)-выходов триггеров 13, 17 также устанавливает на выходе элемента 11 ИЛИ-НЕ (на В-входе триггера 18) логическую 1. Кроме того, логическая 1 с Q -выхода триггера 17 поступает на его 3)-вход, логическая 1 с Q -выхода триггера 13 - на 1)-вход триггера 14, а логический О с выходов триггеров 15 и 18 на D-входы триггеров 16 и 19 соответственно. С приходом на объедш енные С-входы триггеров 11, 12, 1G, 14, 16и 18 первого счетного импульса информация с D-входов триггеров перезаписывается на их Q выходы . Изменение же потенциапа на Q - выходе триггера 15 с Лог. О на Лог. 1 перезаписывает информацию с Q -выхода триггера 17 на его Q-выход и наоборот . В результате файл состояний D-входов и Q -выходов триггеров синхронного счетчика можно записать:

| название | год | авторы | номер документа |

|---|---|---|---|

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1330757A1 |

| Счетчик импульсов для семисегментных индикаторов | 1988 |

|

SU1580550A1 |

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383494A1 |

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| Декадный счетчик для семисегментных индикаторов | 1983 |

|

SU1172005A1 |

| Преобразователь числоимпульсного кода в код семисегментного индикатора | 1983 |

|

SU1105885A1 |

| Декадный счетчик в семисегментном коде | 1987 |

|

SU1432767A1 |

| Синхронный делитель на 12 | 1987 |

|

SU1517129A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1319276A1 |

| Сигнатурный анализатор с перестраиваемой структурой | 1983 |

|

SU1120334A1 |

О О 000000

10 1 1 О О

О 01 1010

О О ОО1000

10 О 000

о о 1 о 000

о о 000 001

о о о 100

10000 010

10000000 00000000

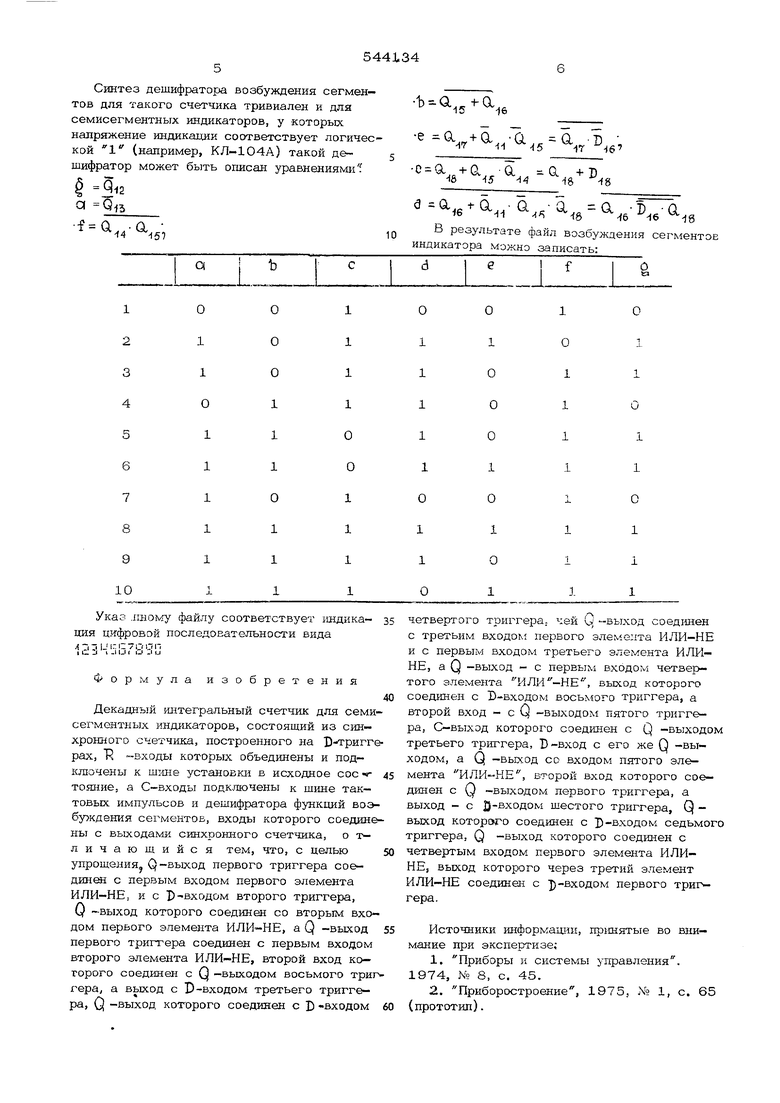

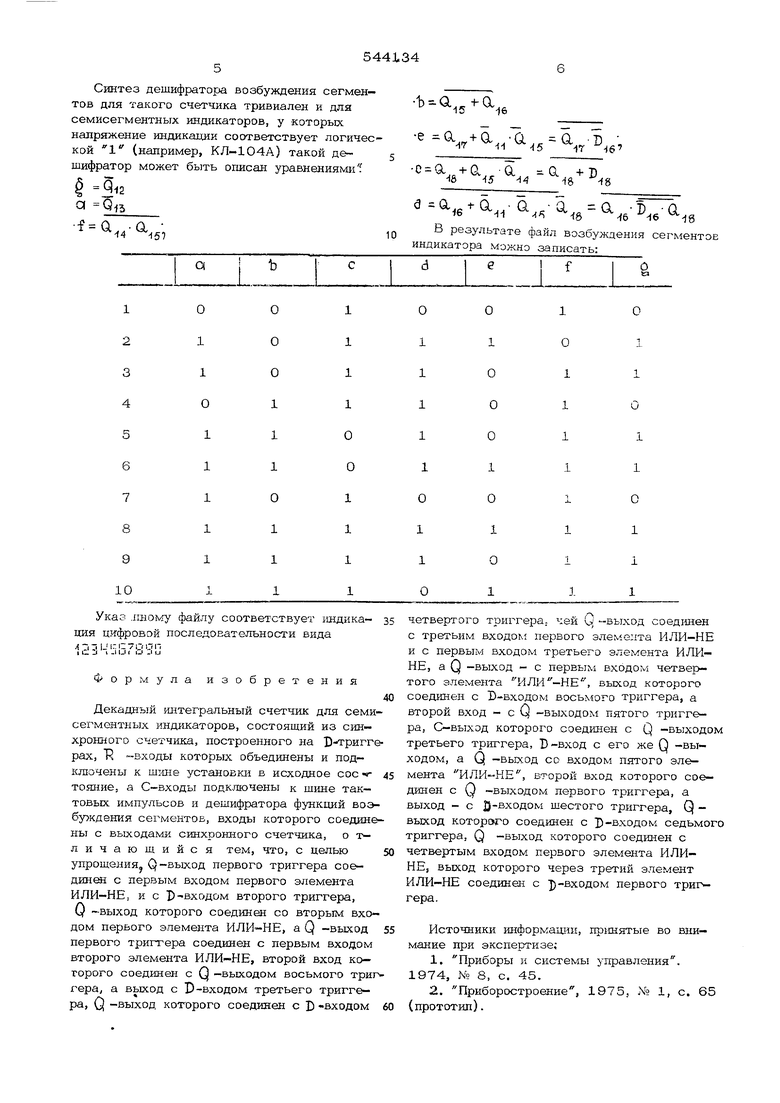

Синтез дешифратора возбуждения сегментов для такого счетчика тривиален и для семисегментных индикаторов, у которых напряжение индикадик соответствует логической 1 (например, КЛ-104А) такой дешифратор может быть описан уравнениямиf

ё

а 15

О

О

о о

1 1

О

1 1 1

1 1

О

10 Указ .иному файлу соответствует шдикация цифровой последовательности вида l и I с ООП 1 с i 1-11-1(1-1 .1 и Формула изобретения Декахщый интегральный счетчик для семи сегментных индикаторов, состоящий из синхронного счетчика, построенного на D-тригг pax. Т -входы которых объединены и под1Ш1очены к Ш1ше установки в исходное сое «то5шие, а С-входы подключены к шине тактовых импульсов и дешифратора функций воэ бркдения сегментов, входы которого соедин ны с выходами синхронного счетчика, о т- личающийся тем, что, с целью упрошения, Q-выход первого триггера соединен с первым входом первого элемента ИЛИ-НЕ, и с D-входом второго триггера, Q -выход которого соединен со вторьпу вхо дом первого элемента , а Q -выход первого триггера соединен с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с Q -выходом восьмого три гера, а вь1ход с D-входом третьего триггера, Q -выход которого соединен с D -входом

.

....,5 Sr-V

+а, -а, а +D

-16 5 Н4 8 -fg

...-.. о.-1..-а

о

о

о

о 1

1 1

1 1

о

1 1 1

о о 1

1 1

1 о о

и 1 1

о

о

о

о четвертого триггера; чей ( --выход соед1шен с третьим входом первого элемента ИЛИ-НЕ и с первым входом третьего элемента ИЛИНЕ, а Q -выход - с первым входом четвертого элемента ИЛИ -НЕ, выход которого соединен с Б-входом восьмого триггера, а второй вход - с Q -выходом пятого триггера, С-выход которого соединен с Q -выходом третьего триггера, Б-вход с его же Q -выходом, а Q -выход со входом пятого элемента ИЛИ-НЕ, второй вход которого соединен с Q -выходом первого триггера, а выход - с и-входом шестого триггера, Q выход которого соединен с D-входом седьмого триггера, Q -выход которого соединен с четвертым входом первого элемента ИЛИНЕ, выход которого через третий элемент ИЛИ-НЕ соединен с )-входом первого триггера. Источники информации, пргшятые во внимание при экспертизе; 1. Приборы и системы управления. 1974, № 8, с. 45. 2. Приборостроение, 1975, № 1, с. 65 (прототип).

I to

mf

HO

П

Авторы

Даты

1977-01-25—Публикация

1975-06-30—Подача