входом второго ком- коммутаторов всех узлов сдвига объинформационным

мутатора (п )-го узла сдвига г

JBTopbie информационные входы вторых

1120334

единень и являются входом синхронизации анализатора„

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1246098A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1180902A1 |

СИГНАТУРНЫЙ АНАЛИЗАТОР С ПЕРЕСТРАИВАЕМОЙ СТРУКТУРОЙ, содержащий сумматор по модулю два и четыре узла сдвига, каждый из которых содержит регистр сдвига, дешифратор и узел индикации, причем в каждом узле сдвига выходы регистра сдвига соединены с -входами дешифратора, выходы которого соединены с входами узла индикации, первьй вход сумматора по модулю два является информационным входом анализатора, прямой выход третьего разряда регистра сдвига второго узла, сдвига, прямые выходы первого и четвертого разрядов регистра сдйига третьего узла сдвига и прямой выход четвертого разряда регистра сдвига четвертого узла сдвига соединены соответственно с вторым, третьим, четвертым и пятым входами сумматора по модулю два, отличающийся тем, что, с целью расширения функциональных возможностей анализатора за счет обеспечения контроля блоков, не имеющих жесткой синхронизации, в каждый узел сдвига введены два коммутатора, четыре элемента И и элемент ИЛИ-НЕ, причем в каждом уэле сдвига входы первого элемента И соединены соответственно с инверсными выходами первого, второго и третьего разрядов и с прямым выходом.четвертого разряда регистра сдвига, входы второго элемента И соединены соответственно с прямым выходом, третьего и инверсным выходом четвертого разрядов регистра сдвига, входы третьего элемента И соединены соответственно с инверсным выходом первого и прямым выходом второго разрядов регистра сдвига, входы четвертого элемента И соединены соответственно с инверсным выходом третьего и прямым выходом четвер(Л того разрядов регистра сдвига, выходы второго, третьего и четвертого элементов И соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого соединен с первым информационным входом первого коммутатора, выходы первого и второго коммутаторов го соединены соответственно с информационным и сдвигающим входами регистра о сдвига, управляющие входы всех комму00 таторов всех узлов объединены и являоо J ются входом режима работы анализатора, выход сумматора по модулю два соединен с вторым информационным входом первого коммутатора первого узла сдвига, первый информационный вход второго коммутатора первого узла сдвига соединен с информационным входом анализатора, а прямой выход четвертого разряда регистра сдвига и выход первого элемента И каждого узла сдвига

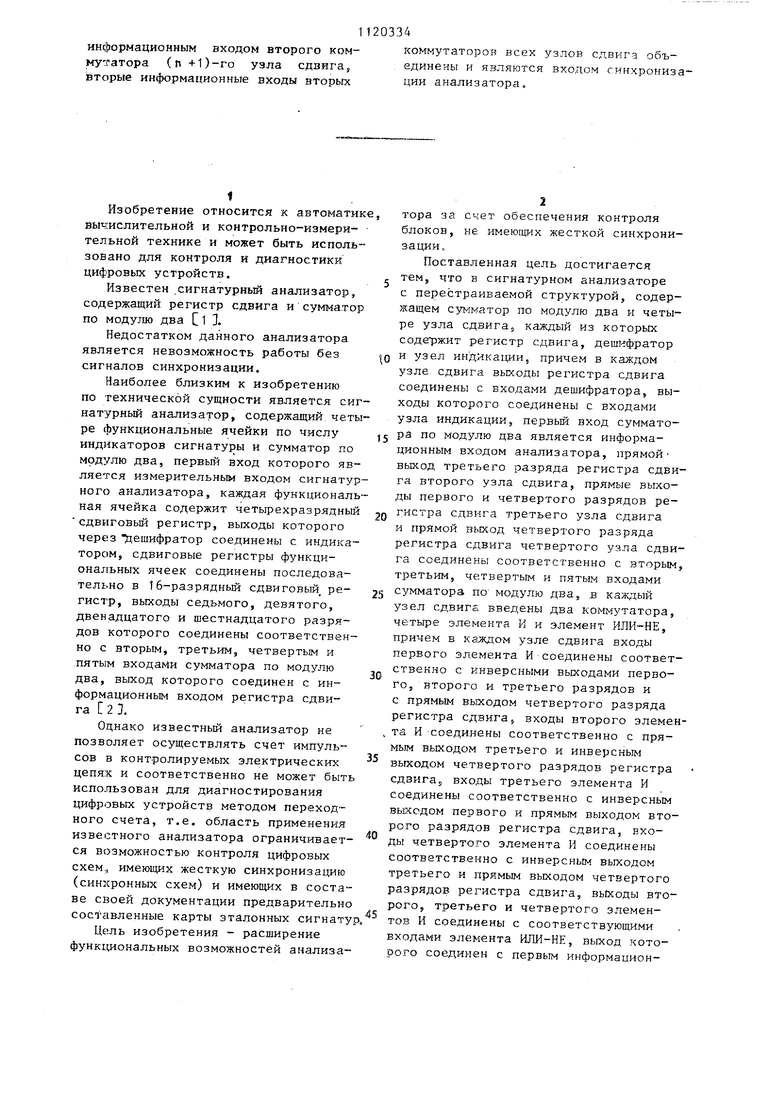

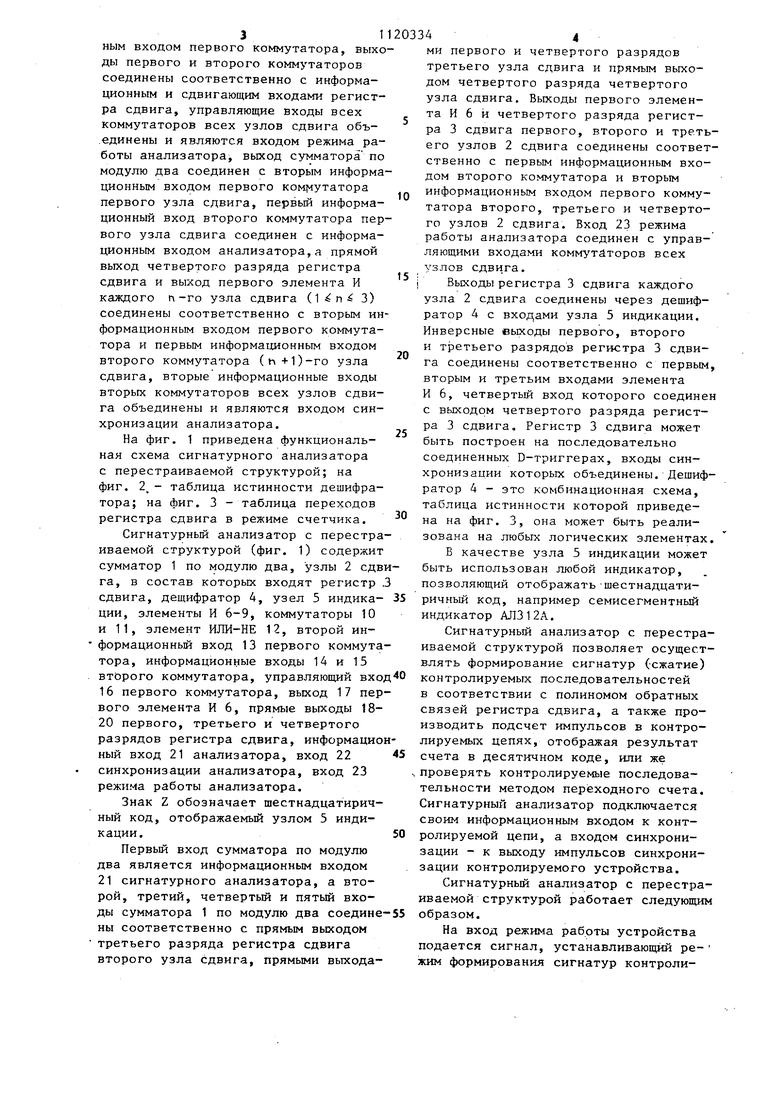

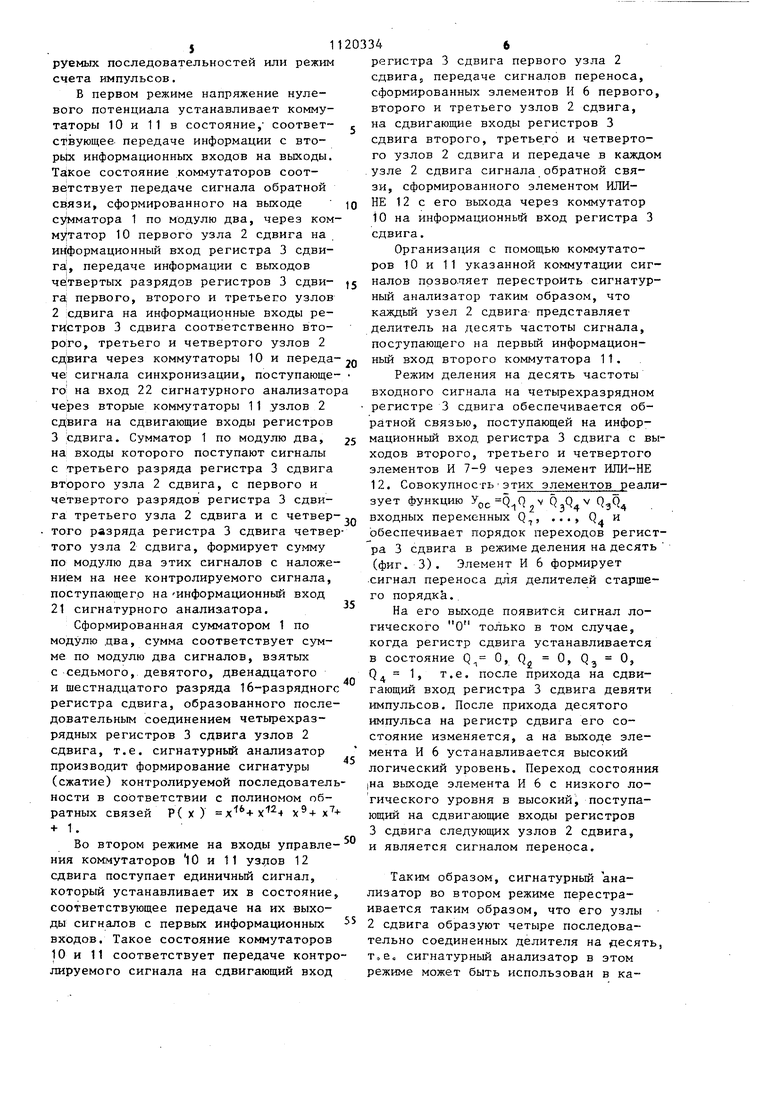

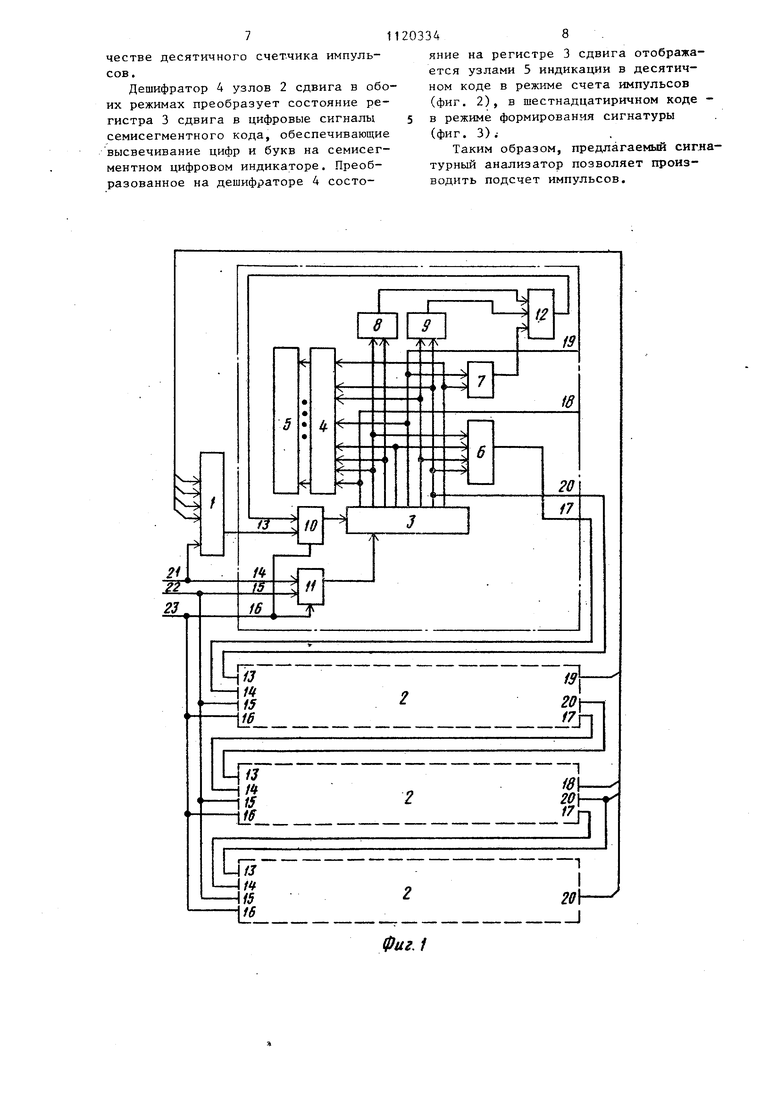

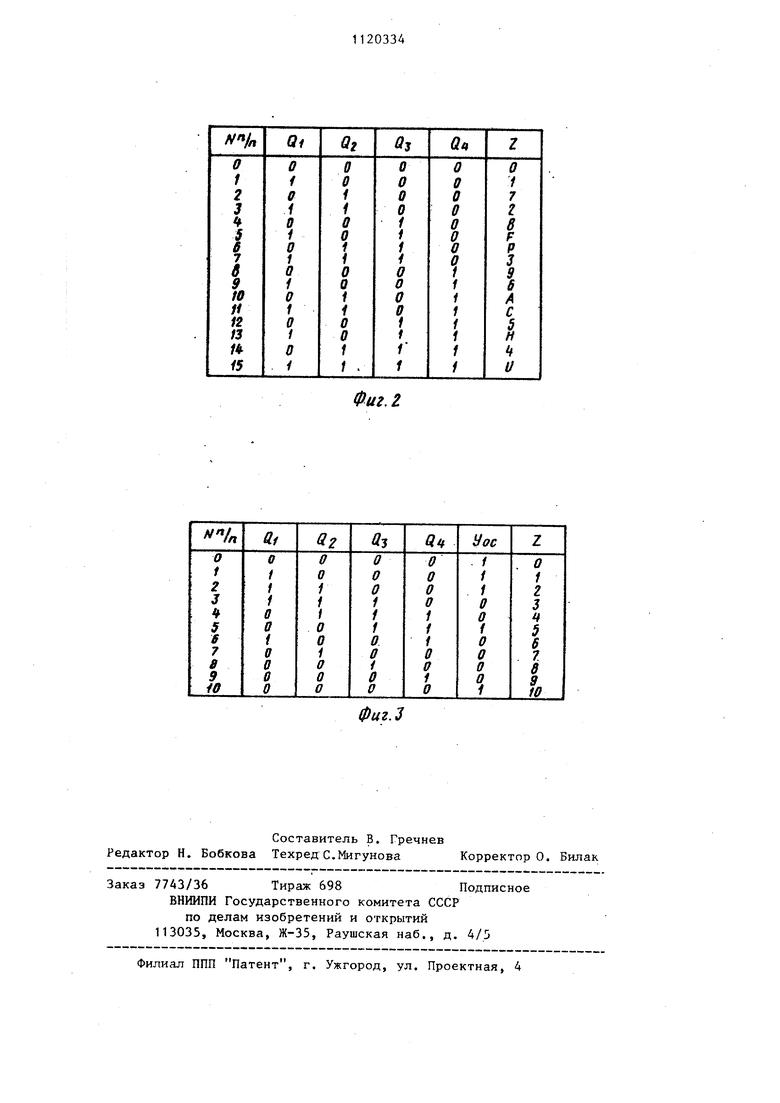

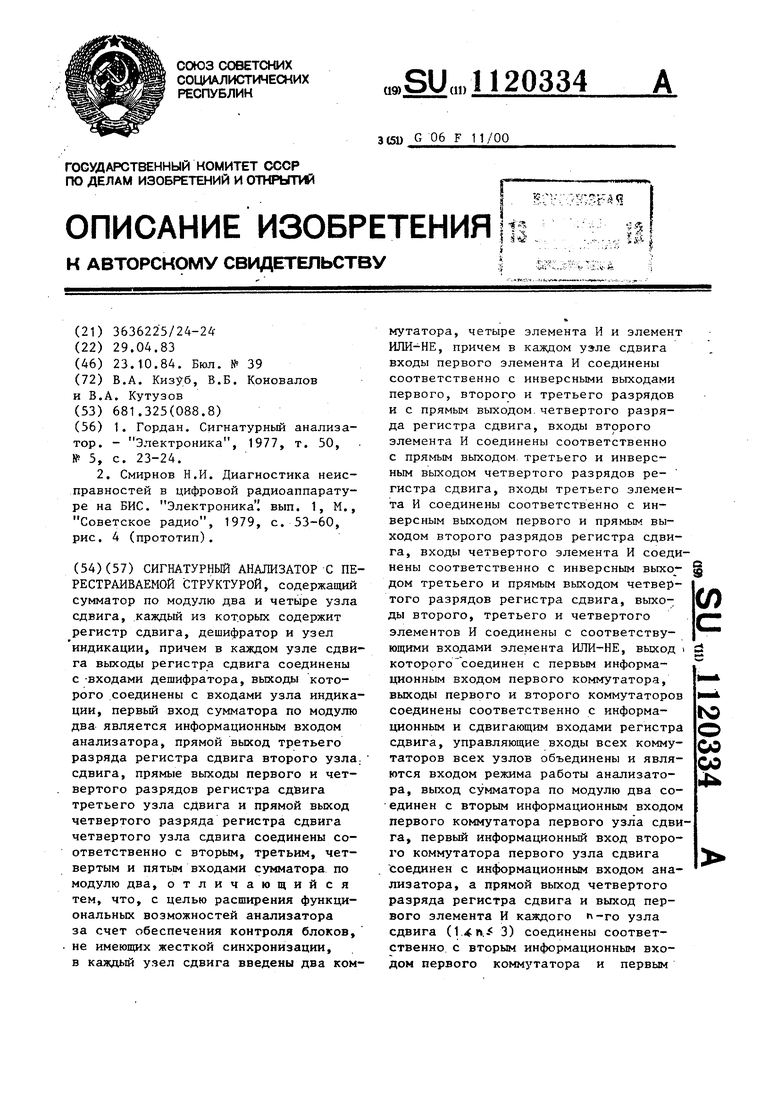

Изобретение относится к автоматик вычислительной и контрольно-измерительной технике и может быть использовано для контроля и диагностики цифровых устройств. Известен .сигнатурный анализатор, содержащий регистр сдвига исумматор по модулю два С1 1 Недостатком данного анализатора является невозможность работы без сигналов синхронизации. Наиболее близким к изобретению по технической сущности является сиг натурный анализатор, содержащий четы ре функциональные ячейки по числу индикаторов сигнатуры и сумматор по модулю два, первый вход которого является измерительным входом сигнатур ного анализатора, каждая функциональ ная ячейка содержит четырехразрядный сдвиговьш регистр, выходы которого через Дешифратор соединены с индикатором, сдвиговые регистры функциональных ячеек соединены последовательно в 16-разрядный сдвиговьй регистр, выходы седьмого, девятого, двенадцатого и шестнадцатого разрядов которого соединены соответственно с вторым, третьим, четвертым и пятым входами сумматора по модулю два, выход которого соединен с информационным входом регистра сдвига С 2 1 Однако известный анализатор не позволяет осуществлять счет импульсов в контролируемых электрических цепях и соответственно не может быть использован для диагностирования цифровых устройств методом переходного счета, т.е. область применения известного анализатора ограничивается возможностью контроля цифровых схем., имеющих жесткую синхронизацию (синхронных схем) и имеющих в составе сзюей документации предварительно составленные карты эталонных сигнату Цель изобретения - расширение функ1у1ональных возможностей анализатора за счет обеспечения контроля блоков, не имеющих жесткой синхронизации. Поставленная цель достигается тем, что в сигнатурном анализаторе с перестраиваемой структурой, содержащем сумматор по модулю два и четыре узла сдвигаS каждый из которых содержит регистр сдвига, дешифратор и узел индикации, причем в каждом узле сдвига выходы регистра сдвига соединены с входами дешифратора, выходы которого соединены с входами узла индикации, первый вход сумматора по модулю два является информационным входом анализатора, прямойвыход третьего разряда регистра сдвига второго узла сдвига, прямые выходы первого и четвертого разрядов регистра сдвига третьего узла сдвига и прямой вьЕкод четвертого разряда регистра сдвига четвертого узла сдвига соединены соответственно с вторым, третьим, четвертым и пятым входами сумматора по модулю два, в кахсдый узел сдвига введены два коммутатора, четыре элемента И и элемент ИЛИ-НЕ, причем в каждом узле сдвига входы первого элемента. И соединены соответственно с инверсными выходами первого, второго и третьего разрядов и с прямым выходом четвертого разряда регистра сдвига входы второго элемента И соединены соответственно с прямым выходом третьего и инверсным выходом четвертого разрядов регистра сдвига, входы третьего элемента И соединены соответственно с инверсным вьйсодом пер.вого и прямым выходом второго разрядов регистра сдвига, входы четвертого элемента Н соединены соответственно с инверсным выходом третьего и прямьм выходом четвертого разрядов регистра сдвига, вьйсоды второго, третьего и четвертого элементов И соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого соедии€ н с первым информаиионным входом первого коммутатора, выхо ды первого и второго коммутаторов соединены соответственно с информационным и сдвигающим входами регистра сдвига, управляющие входы всех коммутаторов всех узлов сдвига объ.единены и являются входом режима работы анализатора, выход сумматора по модулю два соединен с вторым информа ционным входом первого коммутатора первого узла сдвига, первый информационный вход второго коммутатора пер вого узла сдвига соединен с информационным входом анализатора,а прямой выход четвертого разряда регистра сдвига и выход первого элемента И каждого п-го узла сдвига ( 3) соединены соответственно с вторым ин формационным входом первого коммутатора и первым информационным входом второго коммутатора (п+1)-го узла сдвига, вторые информационные входы вторых коммутаторов всех узлов сдвига объединены и являются входом синхронизации анализатора. На фиг. 1 приведена функциональная схема сигнатурного анализатора с перестраиваемой структурой; на фиг. 2, - таблица истинности дешифратора; на фиг. 3 - таблица переходов регистра сдвига в режиме счетчика. Сигнатурный анализатор с перестра иваемой структурой (фиг. 1) содержит сумматор 1 по модулю два, узлы 2 сдв га, в состав которых входят регистр сдвига, дешифратор 4, узел 5 индикации, элементы И 6-9, коммутаторы 10 и 11, элемент ИЛИ-НЕ 12, второй информационньй вход 13 первого коммута тора, информационные входы 14 и 15 второго коммутатора, управляющий вхо 16 первого коммутатора, выход 17 пер вого элемента И 6, прямые выходы 1820первого, третьего и четвертого разрядов регистра сдвига, информацио ный вход 21 анализатора, вход 22 синхронизации анализатора, вход 23 режима работы анализатора. Знак Z обозначает шестнадцатиричный код, отображаемьм узлом 5 индикации. Первый вход сумматора по модулю два является информационным входом 21сигнатурного анализатора, а второй, третий, четвертый и пятый входы сумматора 1 по модулю два соедине ны соответственно с прямым выходом третьего разряда регистра сдвига второго узла сдвига, прямыми выходами первого и четвертого разрядов третьего узла сдвига и прямым выходом четвертого разряда четвертого узла сдвига. Выходы первого элемента И 6 и четвертого разряда регистра 3 сдвига первого, второго и третьего узлов 2 сдвига соединены соответственно с первым информационным входом второго коммутатора и вторым информационным входом первого коммутатора второго, третьего и четвертого узлов 2 сдвига. Вход 23 режима работы анализатора соединен с управляющими входами комм таторов всех узлов сдвига. Выходы регистра 3 сдвига каждого узла 2 сдвига соединены через дешифратор 4 с узла 5 индикации. Инверсные выходы первого, второго и третьего разрядов регистра 3 сдвига соединены соответственно с первым, вторым и третьим входами элемента И 6, четвертый вход которого соединен с выходом четвертого разряда регистра 3 сдвига. Регистр 3 сдвига может быть построен на последовательно соединенных D-триггерах, входы синхронизации которых объединены. Дешифратор 4 - это комбинационная схема, таблица истинности которой приведена на фиг. 3, она может быть реализована на любых логических элементах, В качестве узла 5 индикации может быть использован любой индикатор, позволяющий отображать -шестнадцатиричный код, например семисегментный индикатор AJI312A. Сигнатурный анализатор с перестраиваемой структурой позволяет осуществлять формирование сигнатур (-сжатие) контролируемых последовательностей в соответствии с полиномом обратных связей регистра сдвига, а также производить подсчет импульсов в контролируемых цепях, отображая результат счета в десятичном коде, или же проверять контролируемые последовательности методом переходного счета. Сигнатурный анализатор подключается своим информационным входом к контролируемой цепи, а входом синхронизации - к выходу иь1пульсов синхронизации контролируемого устройства. Сигнатурный анализатор с перестраиваемой структурой работает следующим образом. На вход режима работы устройства подается сигнал, устанавливающий режим формирования сигнатур контроли1руемых последовательностей или режим счета импульсов. В первом режиме напряжение нулевого потенциала устанавливает коммутаторы 10 и 11 в состояние, соответствующее передаче информации с вторых информационных входов на выходы. TatKoe состояние коммутаторов соответствует передаче сигнала обратной связи, сформированного на выходе сумматора 1 по модулю два, через ком мутатор 10 первого узла 2 сдвига на информационный вход регистра 3 сдвиги, передаче информации с выходов четвертых разрядов регистров 3 сдвига первого, второго и третьего узлов 2сдвига на информационные входы регистров 3 сдвига соответственно второго, третьего и четвертого узлов 2 сдвига через коммутаторы 10 и переда че сигнала синхронизации, поступающе го на вход 22 сигнатурного анализато через вторые коммутаторы 11 узлов 2 сдвига на сдвигающие входы регистров 3сдвига. Сумматор 1 по модулю два, на входы которого поступают сигналы с третьего разряда регистра 3 сдвига второго узла 2 сдвига, с первого и четвертого разрядов регистра 3 сдвига третьего узла 2 сдвига и с четвертого разряда регистра 3 сдвига четвер того узла 2 сдвига, формирует сумму по модулю два этих сигналов с наложением на нее контролируемого сигнала, поступающего на информационный вход 21 сигнатурного анализатора. Сформированная сумматором 1 по модулю два, сумма соответствует сумме по модулю два сигналов, взятых с седьмого, девятого, двенадцатого и шестнадцатого разряда 1б-разрядногс регистра сдвига, образованного последовательным соединением четьфехразрядных регистров 3 сдвига узлов 2 сдвига, т.е. сигнатурный анализатор производит формирование сигнатуры (сжатие) контролируемой последователь ности в соответствии с полиномом обР( X ) х ратных связей + 1. Во втором режиме на входы управления коммутаторов 10 и 11 ysjrioB 12 сдвига поступает единичный сигнал. который устанавливает их в состояние соответствующее передаче на их выходы сигналов с первых информационных входов. Такое состояние коммутаторов 10 и 11 соответствует передаче контро лируемого сигнала на сдвигающий вход 346 регистра 3 сдвига первого узла 2 сдвига, передаче сигналов переноса, сформированных элементов И 6 первого, второго и третьего узлов 2 сдвига, на сдвигающие входы регистров 3 сдвига второго, третьего и четвертого узлов 2 сдвига и передаче в каждом узле 2 сдвига сигнала обратной связи, сформированного элементом ИЛИНЕ 12 с его выхода через коммутатор 10 на информационный вход регистра 3 сдвига. Организация с помощью коммутаторов 10 и 11 указанной коммутации сигналов позволяет перестроить сигнатурный анализатор таким образом, что каждый узел 2 сдвига- представляет делитель на десять частоты сигнала, поступающего на первый информационный вход второго коммутатора 11. Режим деления на десять частоты входного сигнала на четырехразрядном регистре 3 сдвига обеспечивается обратной связью, поступающей на информационньй вход регистра 3 сдвига с выходов второго, третьего и четвертого элементов И 7-9 через элемент ИЛИ-НЕ 12. Совокупностьэтих элементов реализует функцию ВХОДНЫХ переменных Q, ..., Q, и обеспечивает порядок переходов регистра 3 сдвига в режиме деления на десять (фиг. 3). Элемент И 6 формирует сигнал переноса для делителей старщего порядка. На его выходе появится сигнал логического О только в том случае, когда регистр сдвига устанавливается в состояние Q О, Q О, Q О, Q 1, т.е. после прихода на сдвигающий вход регистра 3 сдвига девяти импульсов. После прихода десятого импульса на регистр сдвига его состояние изменяется, а на выходе элемента И 6 устанавливается высокий логический уровень. Переход состояния |на выходе элемента И 6 с низкого логического уровня в высокий, поступающий на сдвигающие входы регистров 3 сдвига следующих узлов 2 сдвига. и является сигналом переноса, Таким образом, сигнатурньй анализатор во втором режиме перестраивается таким образом, что его узлы 2 сдвига образуют четыре последовательно соединенных делителя на десять т,е. сигнатурный анализатор в этом режиме может быть использован в ка71

честве десятичного счетчика импульсов.

Дешифратор 4 узлов 2 сдвига в обоих режимах преобразует состояние регистра 3 сдвига в цифровые сигналы семисегментного кода, обеспечивающие высвечивание цифр и букв на семисегментном цифровом индикаторе. Преобразованное на дешифраторе 4 состо/J /« 15

203348

яние на регистре 3 сдвига отображается узлами 5 индикации в десятичном коде в режиме счета импульсов (фиг. 2), в шестнадцатиричном коде 5 в режиме формирования сигнатуры (фиг. 3) .Таким образом, предлагаемый сигнатурный анализатор позволяет производить подсчет импульсов.

19

1

2

20 Фиг.1

Фиг.г

фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гордан | |||

| Сигнатурный анализатор | |||

| - Электроника, 1977, т | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Смирнов Н.И | |||

| Диагностика неисправностей в цифровой радиоаппаратуре на БИС | |||

| Электроника вып | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-10-23—Публикация

1983-04-29—Подача