Изобретение относится к преобразовательной технике, а именно к тиристорным преобразователям с принудительной коммутацией, и может быть иснользовано в непосредственных преобразователях, в инверторах и выпрямителях.

Известно устройство управления тиристорными преобразователями 1, которое содержит формирователи сигналов управления принудительной коммутацией, связанные через суммирующие и дифференцирующие устройства с устройствами, формирующими сигналы управления тиристорными группами преобразователя, и выходными устройствами, формирующими сигналы управления коммутирующими и заряжающими тиристорами узла принудительной коммутации. Данное устройство является прототипом изобретения.

Недостатком известного устройства является его ненадежная работа при произвольных интервалах между импульсами двух последовательностей.

Цель изобретения - повыщение надежности и помехоустойчивости - достигается за счет введения в устройство управления логической схемы с таким алгоритмом работы, который исключает возможность срыва коммутации при любых возможных интервалах времени между сигналами управления

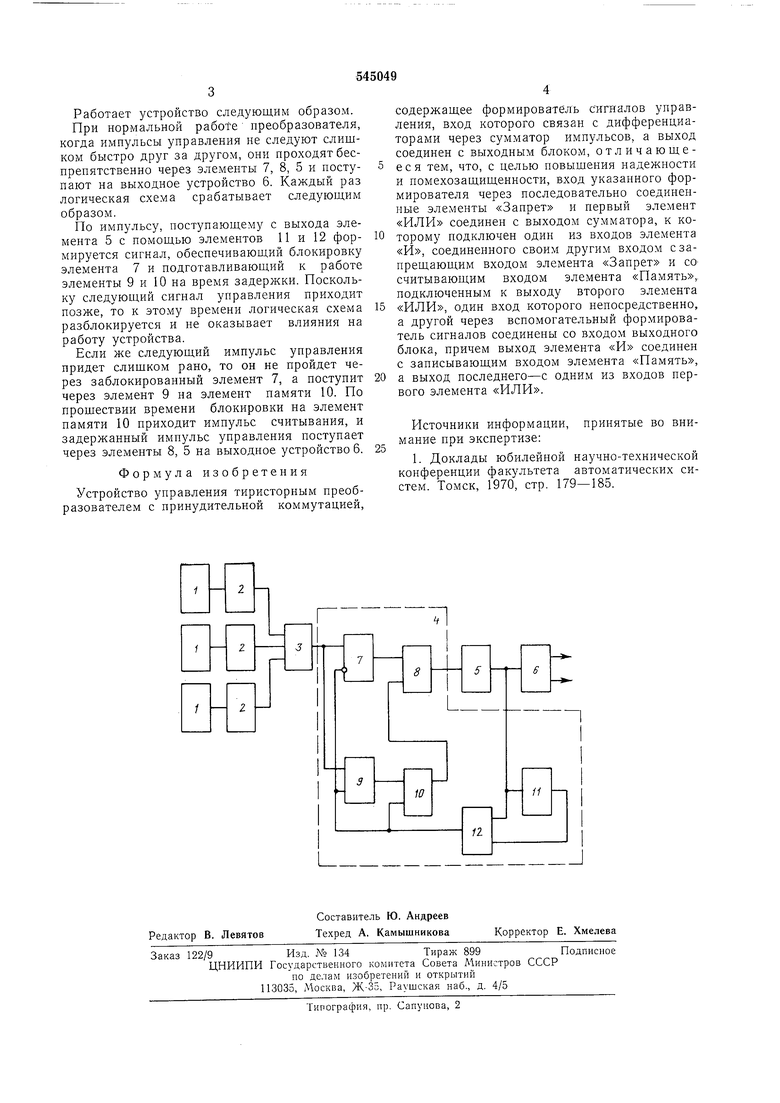

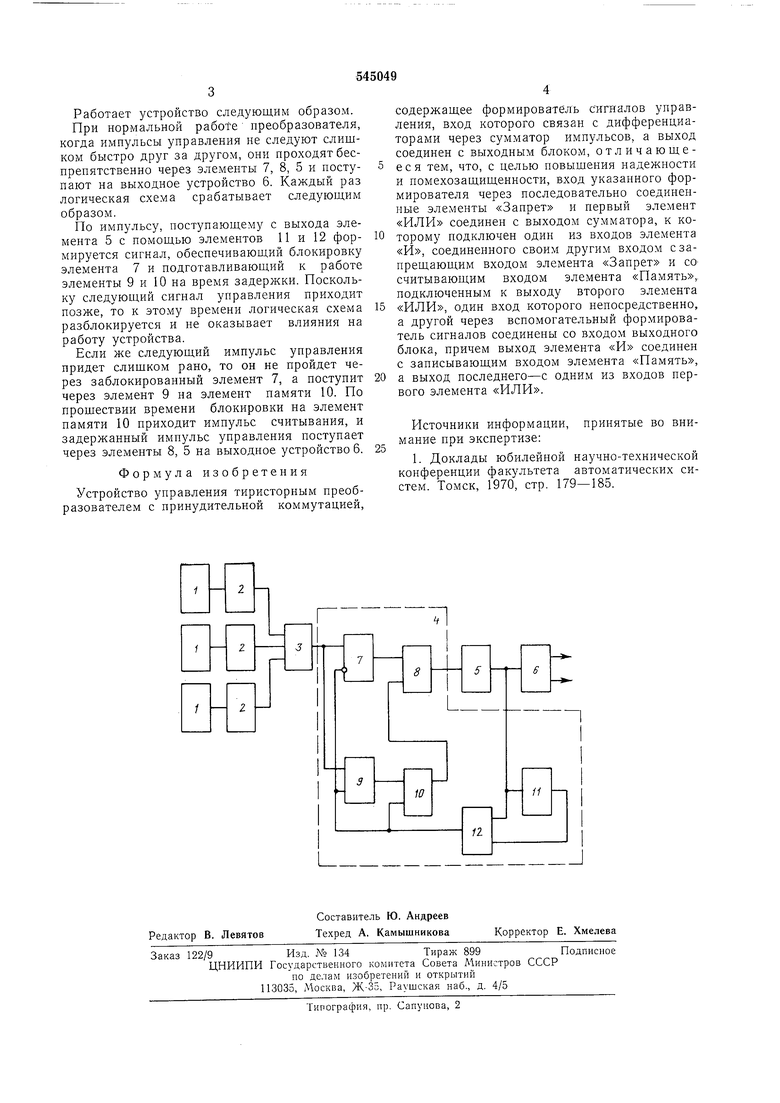

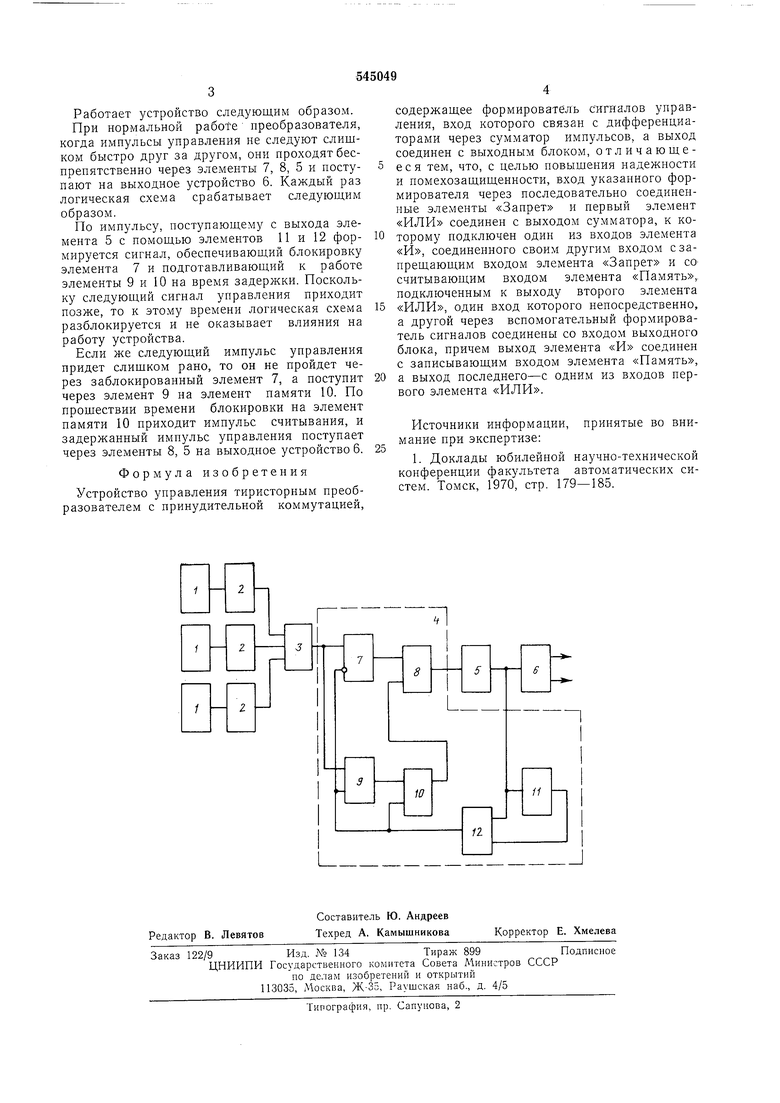

На чертеже приведена функциональная схема предлагаемого устройства. Устройство состоит из формирователей сигналов управления тиристорными группами преобразователя 1, дифференциаторов 2, подключенных к их выходам, и сумматора 3 сигналов дифференциаторов. Выход сумматора через логическое устройство 4 соединен с формирователем сигнала управления коммутацией 5, который, в свою очередь, соединен с выходным устройством 6.

Логическое устройство 4 состоит из элемента «Запрет 7, выход которого через элемент «ИЛИ 8 соединен со входом формирователя 5. Вход элемента «Запрет соединен с выходом сумматора 3, с которым соединен также и первый вход элемента «И 9. Выход элемента «И 9 соединен с записывающим входом элемента памяти 10.

Кроме того, в логическом устройстве имеется дополнительный формирователь 11, вход которого соединен с вы.ходом формирователя 5. Выходы формирователей 5 и 11 соединены с двумя входами второго элемента «ИЛИ 12, выход которого соединен со считывающим входом элемента «Память 10, вторым входом элемента «И 9 и с запрещающим входом элемента «Запрет. Выход элемента «Память 10 соединен со вторым входом первого элемента «ИЛИ 8.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления статическим тиристорным компенсатором | 1985 |

|

SU1309175A1 |

| Устройство управления тиристорным преобразователем с принудительной коммутацией | 1971 |

|

SU547009A1 |

| Устройство принудительной коммутации тиристоров | 1985 |

|

SU1275685A2 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Преобразователь трехфазного переменного напряжения в переменное для систем бесперебойного электропитания | 1987 |

|

SU1495907A1 |

| СИСТЕМА УПРАВЛЕНИЯ ГРУППОЙ АСИНХРОННЫХ ЭЛЕКТРОПРИВОДОВ ВОДЯНЫХ НАСОСОВ | 2003 |

|

RU2251206C2 |

| Тяговый преобразователь постоянного напряжения в трехфазное переменное | 1989 |

|

SU1690137A1 |

| Устройство принудительной коммутации тиристоров преобразователя | 1984 |

|

SU1267550A1 |

| Устройство принудительной коммутации тиристоров преобразователя | 1985 |

|

SU1302392A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

Авторы

Даты

1977-01-30—Публикация

1972-02-21—Подача