1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения систем высокой надежности.

Известно резервированное по мажоритарному принцииу устройство, которое содержит резервируемых каналов, причем не менее -f-1 каналов подключены к источнику питаиия непосредственно, а остальные - через блок выявления неидентичной работы любого из упомянутых каналов. Однако в этом известном устройстве при отказе одного из каналов к источнику питания подключаются все оставшиеся k каналы, т. е. возрастает потребление энергии от источника питания. Известно также устройство управлеиия резервированной системы, содержавшее счетчик, соединенный с дешифратором, выходы которого через элемеиты «ИЛИ подключены к переключателям питания резервируемых блоков, а выходы последних непосредственно и через элемент «ИЛИ подключены к входам элементов несовпадения, выходы которых соедииены со входами элементов «И, вторые входы которых подсоединены к шинам питания соответствуюш,их резервируемых блоков, а выходы через элемент «ИЛИ подсоединены к счетчику. Это известное устройство характеризуется возможностью блокировки переключения блоков при включении

пары неисправных блоков, имеюших одинаковые выходные сигналы; такой случай может иметь место в процессе попска пары исиравных блоков, в результате чего выходной снгнал системы определяется неисправными блоками, что приводит к отказу резервированной системы.

Цель изобретения - повышение надежности устройства, а также более полное использование резерва - обеспечение работоспособности резервированной системы при наличии в последней хотя бы двух исправных блоков. В описываемом устройстве это достигается тем, что в нем, кроме счетчика, соединенного

через дешифратор с переключателями питания п резервируемых блоков, выходы которых непосредственно и через первый элемент «ИЛИ подключены к входам элементов несовпадения, выходы которых соединены с

первыми входами первых двухвходовых элементов «И, вторые входы которЪ1х соединены с шинами питания соответствуюших резервируемых блоков, а выходы - с входами второго элемента «ИЛИ, дополнительно установлены генератор импульсов, элемент задержки, третий элемент «ИЛИ, два элемента «ИЛИ-НЕ 2« элементов памяти, элементов «НЕ, двухвходовых элементов «И, 2д-|-1 трехвходовых элементов «И,

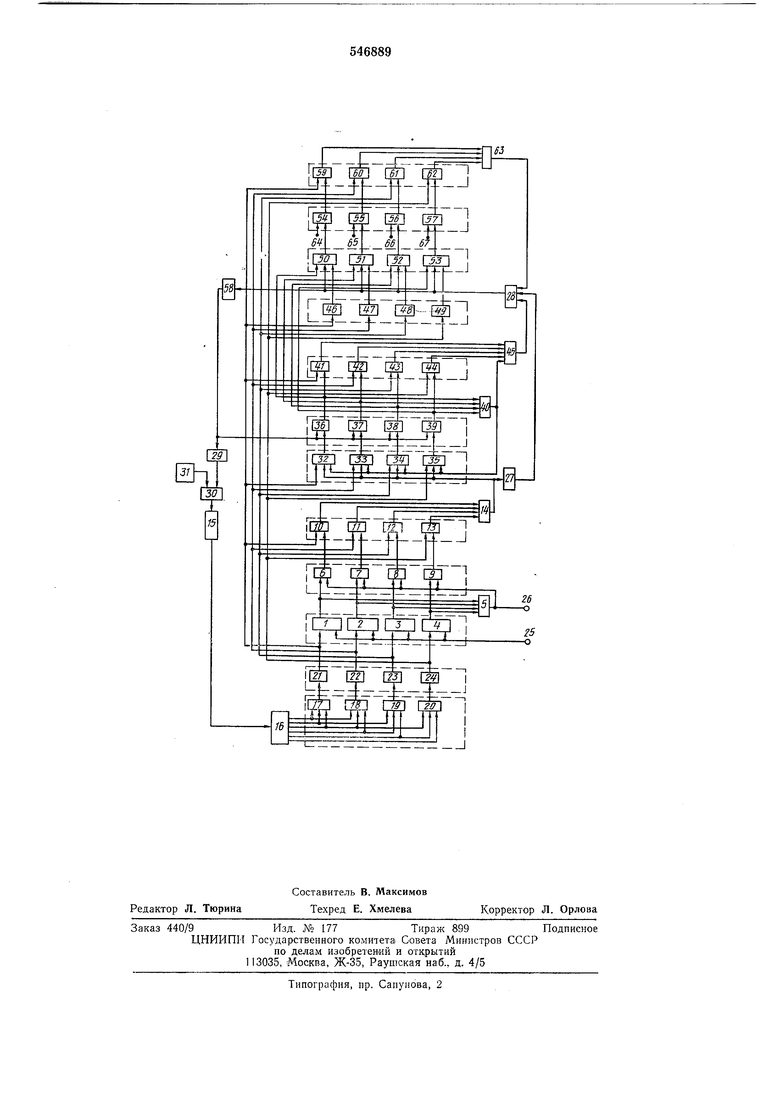

причем выход второго элемента «ИЛИ соедпнеи со входом элемента «НЕ и с первыми входами п трехвходовых элементов «И, вторые входы которых соединены с шинами иитания соответствующих резервируемых блоков, а третьи входы - с выходом иервого элемента «Р1ЛИ-НЕ и с одним из входов третьего элемента «ИЛИ, другие входы которого соединены с выходами вторых п двухвходовых элементов «И, выход элемента «НЕ соединен с иервым входом трехвходового элемента «И, второй вход которого соединен с выходом третьего элемента «ИЛИ, третш вход - с выходом второго элемента «ИЛИНЕ, а выход соединен со входом элемента задержки и с иервыми входами вторых п трехвходовых элементов «И, вторые входы которых соединены с выходами соответствуюпдих элементов «НЕ, входы которых соедниены с шинами иитання соответетвуюгцих резервируемых блоков, а третьи входы - с выходами соответствуюш их первых п элементов памяти и иервыми входами соответетвуюгцих вторых /X двухвходовых элементов «И, вторые входы которых соединены с шинами нитання соответствующих резервируемых блоков, а также с входами первого элемента «Р1ЛИ-НЕ, а выходы вторых п трехвходовых элементов «PI соединены с информационными входами соответствующих вторых п элементов памяти, выходы которых соединены с первыми входами соответствующих третьих п двухвходовых элементов «И, вторые входы которых соединены с шинами нитания соответствующих резервируемых блоков, а выходы- с входами второго элемента «ИЛИИЕ, выход элемента задержки соединен с входами установки исходного состояния соответствующих первых я элементов памяти, информационные входы которых соединены е выходами соответствующих вторых п трехвходовых элементов «И, и с входом элемента «НЕ, выход которого соединен с первым входом двухвходового элемента «И, второй вход которого соединен е выходом генератора импульсов, а выход - е входом счетчика. На чертеже приведена блок-схема описываемого устройства для резервированной системы, состоящей нз двух рабочих и двух резервных блоков. Блоки 1, 2, 3 и 4 резервируемой системы соединены с устройством для управления переключением резерва, которое содержит элемент «ИЛИ 5, элементы 6, 7, 8 и 9 несовпадения, элементы «И 10, 11, 12 и 13, элементы «ИЛИ 14, счетчик 15, дешифратор 16, элементы «ИЛИ 17, 18, 19 и 20, переключатели питания 21, 22, 23 и 24, вход 25, резервированной системый, выход 26 резервированной системы, элемент «НЕ 27, элемент «И 28, элемент «НЕ 29, элемент «И 30, генератор импульсов 31, элементы «И 32, 33, 34 и 35, элементы памяти 36, 37, 38 и 39, элемент «ИЛИ-НЕ 40, элементы «И 41, 42, 43 и 44, элемент «ИЛИ 45, элементы «НЕ 46, 47, 48 и 49, элементы «И 50, 51, 52 и 53, элементы иамяти 54, 55, 56 и 57, элемеит задержки 58, элементы «И 59, 60, 61 и 62, элемеит «ИЛМНЕ (33, входы 64, 65, 66. п 67 сброса элементов памяти 54, 55, 56 и 57. Сигналы с блоков 1, 2, 3 и 4 резервированной системы поступают на элемент «ИЛИ 5 и на первые входы элементов несовнадения 6, 7, 8 и 9, вторые входы которых соединены с выходом 26 системы. Сигналы несовпадения с выходов элементов 6, 7, 8 и 9 поступают на первые входы элементов «И 10, 11, 12 и 13, вторые входы которых соединены с шинами питания соответствующих блоков 1-4. Сигпалы песовиадения с выходов элементов «И 10-13 поступают на элемент «ИЛИ 14, с выхода которого, во-первых, на вход элемента «НЕ 27, во-вторых, на входы элементов «И 32, 33, 34 и 35, вторые входы которых соединены с шипами питания соответствующих резервируемых блоков, а третьи входы - с выходом элеме 1та «ИЛИ-НЕ 40. С выхода элемента «НЕ 27 сигнал поступает па вход элемента «И 28, на второй вход которого поступает сигнал е выхода элемента «ИЛИ 45, а на третий вход - с выхода элемента «ИЛИ-НЕ 63. С выхода элемента «И 28 сигнал поступает, во-первых, па вход элемента задержки 58, вовторых, на входы элементов «И 50, 51, 52 и 53, па вторые входы которых поступают сигналы с выходов элементов «НЕ, входы которых соедииепы с шинами питания соответствующих резервируемых блоков, а на третьи входы - с выходов элементов иамяти 36, 37, 38 и 39, которые, кро.ме того, поступают на входы элемента «ИЛИ-НЕ 40 и на входы элементов «И 41, 42, 43 и 44, вторые входы которых соединены с шинами питания соответствующих резервируемых блоков. На входы элемента «Р1ЛИ 45 поступают сигналы с выхода элемента «ИЛИ-НЕ 40 и элементов «И 41,42,43 и 44. С выходов элементов «И 50, 51, 52 и 53 сигналы поступают на информационные входы элементов памяти 54, 55, 56 и 57, фиксирующих неисправный блок, с выходов которых сигналы поступают на входы элементов «И 59, 60, 61 и 62, вторые входы которых соединены с шинами питания соответствующпх резервируемых блоков, а выходы - с в.ходами эле.мента «ИЛИ-НЕ 63. С выхода элемента задержки 58 сигнал поступает, во-первых, на входы установки исходного состояния элементов памяти 36, 37, 38 и 39, на информационные входы которых поступают сигналы с выходов элементов «И 32, 33, 34 и 35, во-вторых, на вход элемента «НЕ 29. С выхода элемента «НЕ 29 сигнал поступает на вход элемента «И 30, на второй вход которого поступают импульсы с выхода генератора импульсов 31. С выхода элемента «И 30 сигнал поступает на вход счетчика 15. Счетчик 15 соединен с ешифратором 16, который выдает сигналы б отказах резервируемых блоков на шины, правляющие через элементы «ИЛИ 17, 18, 19 и 20 иерек.иочателями питания, которые в ависи.мост от состояния счетчика 15 подают

питание на те или иные попарные комбинации блоков 1, 2, 3 и 4, например 1 и 2, 1 и 3, 1 н 4,

2и 3, 2 и 4, 3 и 4.

В начальный момент элементы иамятн 36- 39 и 54-57 приведены в исходное состояние и выдают на выходах нули, вследствие чего выходные сигналы элементов «И 41-44, 50- 53 и 59-62 равнынулю, а выходные сигналы элементов «ИЛИ-НЕ 40 н 63, а также элемента «ИЛИ 45 равны единице. Пусть в начальный момент счетчик 15 находится в состоянии, при котором дешифратор 16 выдает сигнал по шине, соединенной с элементами «ИЛИ 17 и 18. Так как на остальных шинах депшфратора 16 сигналы отсутствуют, то выходные сигналы имеются только на входах элементов «ИЛИ 17 и 18, и переключатели питания 21 и 22 подают напряжение питания на резервируемые блоки 1 и 2; при этом выдается разрешение прохождения сигнала несовпадения (единицы) через элементы «И 10 и 11, а элементы 12 и 13 обесточенных блоков

3и 4 выдают на выходе сигналы, равные пулю. Блоки и 2 в соответствии с входным сигналом и логикой своей работы выдают выходные ст гналы, равные нулю или единице; при исправиом элементе «ИЛИ 5 сигналы на входах элементов 6 и 7 совпадают, выходные сигналы элементов «И 10 и 11 и «ИЛИ 14 также равны нулю, вследствие чего равны нулю выходные снгналы элементов «И 32, 33, 34 и 35, а выходной сигнал элемента «НЕ 27, а также элемента «И 28 и элемента задержки 58 равен единице. Выходной сигнал элементов «НЕ 29 и «И 30 равен нулю, и счетчик 15 сохраняет свое состояние; в итоге остаются включенными блоки 1 и 2.

Пусть вследствие неисиравности, например, блока 2, последний выдает «ложную единицу, а блок 1 - нуль. В этом случае сигнал на выходе элемента «НЛИ 5 равен единице, сигнал на выходе элемента несовпадения 6 равен единице, а на элементе 7 - нулю, что приводит к появлению единицы на выходе элементов «И 10 и «ИЛИ 14, а также элементов «И 32 и 33. На выходе элелгента «НЕ 27 появляется нуль, что приводит к появлению нулевого сигнала на выходе элемента «И 28 и элемента задержки 58.

Таким образом, с входов установки исходного состояния элементов памяти 36-39 снимаются единичные сигналы гашения, в результате чего срабатывают элементы памяти 36 и 37, на информационные входы которых поступают единицы с выходов элементов «И 32 и 33, и выдают Hl своих выходах единицы, что приводит к появлению нулевого сигнала на выходе элемента «ИЛИ-НЕ 40. На выходе элемента «НЕ 29 появляется единичный сигнал, который открывает элемент «И 30 для прохождения на счетчик 15 импульса с выхода генератора импульсов 31. Счетчик 15 переходит в следуюш,ее состояние, при котором напряжение питания поступает на другие комбинации блоков (в рассматриваемом случае-

на блоки I и 3). Так как блоки 1 и 3 исправны, то сигналы на выходах элементов несовпадения 6 и 8, а также элементов «И 10 и 12 или «11Л1Ъ 14 равиьт нулю. Сигнал на выходе эле 1епта «НЕ 27 становится равен единице. Сигнал на выходе элеме гга «ИЛИ 45 при нулевом сшиале на выходе элемента «ИЛИНЕ 40 определяется выходными сигналами элементов «И 41-44 и рапен единице, когда

появляется единичный сигнал на выходе одного из них, что имеет место тогда и только тогда, когда в новую комбинацию включенных блоков входит один из блоков той комбинации, с которой началось переключение, В рассматриваемом случае в новую комбинацию включеииых блоков 1 и 3 входит блок 1, относяи,ийся к ьюмбшации 1 и 2, зафиксированной элементами памяти 36 и 37, с которой началось переключение, что регистрируется элементом «И 41, на оди1 вход которого поступает единила с выхода элемента памяти 36, а на втором вход - по шине питания включенного блока 1, в результате на выходе элементов «И 41, «ИЛИ 45 и «И 28 иоявляется

единииа, при этом появляется единица н на выходе элемента «И 51, так как на один из его входов поступает единица с выхода элемента «И 28, на второй вход - единица с выхода элемента памяти 37, а на третий

ВХ0.1 - единица с выхода элемента «НЕ 47, на вход которого поступает нулевой сигнал по шине питания отключеиого блока 2. В результате срабатывает элемент памяти 55, фиксирующий неиснравный блок 2. На выходе элемента задержки 58 через время, необходимое для срабатывания элемента памяти, тоже появляется единичный сигнал, который, во-первых, осуществляет сброс элементов памяти 36 и 37, что приводит к иоярлению единицы на выходе элемента «ИЛИ-НЕ 40, во-вторых, вызывает появление на выходе элемента «НЕ 29 нулевого сигнала, который запрещает прохождение через элемент «И 30 и пyльcoв с генератора

импульсов 31 па счетчик 15, и последний сохраняет состояние; в итоге остаются включеиН1ТМИ блоки 1 и 3.

Пусть через некоторое время вследствие неисправности, например, блока 3, последний

выдает «ложный ну,ть, а блок 1 - единицу, В этом сллчае сигнал на выходе элемента «ИЛИ 5 равен единице, сигнал на выходе элемента несовпадения 6 равен нулю, а на элементе 8 - единице, что приводит к появлению единниы ип выходе элементов «И 12 и «ИЛИ 14. а также элементов «И 32 н 33. На выходе элe eнтoг. «НЕ 27 и «И 28, а также элемента залсржктт 58 появляется пуль, срабатыпают эле генты памяти 36 н 38, на инфорациоииыс входы которых поступают едииицы выходов элементов «И 32 и 33, и выдают на поих выходах единицы, что приводит к появ.-тгю нулевого сигнала на выходе элемента-1-1ЛИ-НЕ 40. На выходе элемента «НЕ 29

появляется единица, которая открывает элемент «И 30 для прохождения на счетчик 15 импульса с выхода генератора импульсов 31. Счетчик 15 переходит в следующее состояние, при котором напряжение питания поступает на другие комбинации блоков (в рассматриваемом случае - на блоки 1 и 4). Так как блоки 1 и 4 исправны, то сигналы на выходах элементов несовпадения 6 и 9, а также элементов «И 10 и 13 и «ИЛИ 14 равны нулю. Сигнал на выходе элемента «НЕ 27 становится равен единице. На выходе элемента «ИЛИ 45 тоже сохраняется единица, так как равен единице сигнал на выходе элемента «И 41, на один вход которого поступает единица с выхода элемента памяти 36, а на второй вход - единица по гнине питания блока 1. В результате появляется единица на выходе элемента «И 28, а также элемента «И 52, на второй вход которого поступает единица с выхода элемента памяти 38, а на третий вход-единица с выхода элемента «НЕ 48, на вход которого поступает нулевой сигнал по шине питания отключенного блока 3. В результате срабатывает элемент памяти 56, фиксирующий неисправный блок 3. На выходе элемента задержки 58 появляется единичный сигнал, который, во-первых, осуществляет гашение элементов памяти 36 и 38, что приводит к появлению единицы на выходе элемента «ИЛИ-НЕ 40, во-вторых, вызывает появление на выходе элемента «НЕ 29 нулевого сигнала, запрещающего прохождение через элемент «И 30 импульсов с генератора импульсов 31 на счетчик 15, и последний сохраняет свое состояние; в итоге остаются включенными блоки 1 и 4. Пусть удалось восстановить неисправный блок 2, тогда необходимо осуществить сброс элемента памяти 55 по входу 65. Если во время ремонта отказавшего блока 3, отказывает рабочий блок 4, и на его выходе появляется нзлевой сигнал, а на выходе второго рабочего блока 1 - единичный сигнал, то на выходе элемента «ИЛИ 5, сигнал оказывается равен единице, на выходе элемента несовпадения 6 - нулю, а на элемент 9 - единице, что приводит к появлению единицы на выходе элементов «И 13 и «ИЛИ 14, а также элементов «И 32 и 35. На выходе элемента «НЕ 27 появляется нуль, что приводит к появлению нулевого сигнала на выходе элемента «И 28 и элемента задержки 58. Срабатывают элементы памяти 36 и 39, на информационные входы которых пост)шают единицы с выходов элементов «И 32 и 35 и выдают на своих выходах единицы, что приводит к появлению нулевого сигнала на выходе элемента «ИЛИ-НЕ 40. На выходе элемента «НЕ 29 появляется единица, которая открывает элемент «И 30 для прохождения на счетчик 15 импульса с выхода генератора имщ льсов 31. Счетчик 15 переходит в следующее состояние, при котором напряжение питания поступает на другие комбинации блоков, (в рассматриваемом случае - на блоки 2 и 3). Так как блок 3 - неисправен, и на его выходе сохраняется улевой сигнал, в то время как исправный лок 2 выдает единичный сигнал, то на выхое элемента «ИЛИ 5, а также элемента неовпадения 8 и элемента «И 12 появляется единица, и на выходе элемента «ИЛИ 14 сораняется единичный сигнал, а на выходах лементов «НЕ 27, «И 28 и элемента заержки 58 - нулевой сигнал. В результате на выходе элемента «НЕ 29 сохраняется единица, и на счетчик 15 с выхода генератора импульсов 31 через элемент «И 30 проходит следующий импзльс, от которого счетчик 15 переходит в следующее состояние, при котором напрял ;ение питания поступает на другие комбинации блоков (в рассматриваемом случае- на блоки 2 и 4). Так как блок 4 - неисиравеи и на его выходе сохраняется нулевой сигнал, в то время как исправный блок 2 выдает единичный сигнал, то на выходе элемента «ИЛИ 5, а также элемента несовпадения 9 и элемента «И 13 появляется единица, и на выходе элемента «ИЛИ 14 сохраняется единичный сигнал, а на выходах элементов «НЕ 27, «И 28 и элемента задержки 58 - нулевой сигнал. В результате на выходе элемента «НЕ 29 сохраняется единица, и с выхода генератора импульсов 31 через элемент «И 30 проходит следующий импульс на вход счетчика 15, после чего последний переходит в очередное состояние, нри котором напряжение питания поступает на другие комбинации блоков (в рассматривае1мом случае - на блоки 3 и 4). Так как оба блока 3 и 4 неисправны и выдают на своих выходах нулевые сигналы, то сигналы на выходах элементов несовпадения 8 и 9, а также элементов «И 12 и 13 и «ИЛИ 14 равны . Хотя сигнал на выходе «ИЛИ 14 равен нулю, переключение блоков не прекращается. Действительно, так как на выходе элемента памяти 56, фиксирующего неисправный блок 3, - единица, то элемент «И 61 выдает на своем выходе единицу, поскольку на его второй вход поступает единица по шине питания включенного блока 3, вследствие чего на выходе элемента «ИЛИ-НЕ 63 - нулевой сигнал, и хотя на выходе элемента «НЕ 27, а также элемента «ИЛИ 45 - единицы, на выходе элемента «И 28, а также элемента задержки 58 сохраняется нуль. В результате на выходе элемента «НЕ 29 сохраняется единица, разрешающая прохождение с выхода генератора импульсов 31 через элемент «И 30 следующего импзльса на счетчик 15, и последний переходит в очередное состояние, при котором напряжение питания поступает на другие комбинации блоков (в рассматриваемом случае на блоки 1 и 2). Так как оба блока 1 и 2 - исправны, то сигналы на выходах элементов несовпадения 6 и 7, а также элементов «И 10 и II и «ИЛИ 14 равны нулю. Сигнал на выходе элемента «НЕ 27 становится равен единице. На выходе элемента «ИЛИ 45 - тоже единица, так как элемент «И 41 выдает единицу, поскольку на один вход его поступает единица с выхода элемента памяти 36, а нз Другой вход - единица по шине питания включенного блока 1. На выходе элемента «ИЛИНЕ 63 теперь появляется единица, так как на выходе всех элементов «И 59-62 - нули. В результате появляется единица на выходе элемента «И 28, а также - элемента «И 53, поскольку на его второй вход поступает единица с выхода элемента памяти 39, а на третий вход - единица с выхода элемента «НЕ 49, так как на вход последнего поступает нулевой сигнал по шине питания отключенного блока 4, и срабатывает элемент памяти 57, фиксирующий неисправный блок 4. На выходе элемента задержки 58 тоже появляется единица, которая, во-первых, осуществляет сброс элементов памяти 36 и 39 во-вторых, вызывает появление на выходе элемента «НЕ 29 нулевого сигнала, блокирующего прохождение через элемент «И 30 импульсов с выхода генератора импульсов 31 на счетчик 15, который, таким образом, сохранит свое состояние; в итоге остаются включенными блоки 1 и 2. Описываемое устройство может быть использовано для управления переключения как цифровых, так и аналоговых резервируемых блоков и позволяет экономить расход электроэнергии на питание резервированной системы, так как работоспособность системы обеспечивается при питании только двух блоков, независимо от общего числа блоков резервированной системы. При одном и том же общем числе блоков резервированной системы оно обеспечивает значительно более высокую надежность всей системы в целом, т. е. для обеспечения заданной надежности резервированной системы может содержать значительно меньшее число блоков при иснользовании известных устройств для переключения резерва, что существенно удешевляет систему. Формула изобретения Vcтpoйcтвo для управления переключением резерва, содержащее счетчик, соединенный через дешифратор с переключателями питания п резервируемых блоков, выходы которых непосредственно и через первый элемент «ИЛИ подключены к входам элементов несовпадения, выходы которых соединены с первыми входами первых двухвходовых элементов «И, вторые входы которых соединены с шинами питания соответствующих резервируемых блоков, а выходы - с входами второго элемента «ИЛИ, отличающееся

V

546889

10 тем, что, с целью повыщення надел-;ности устройства, оно содержит генератор импульсов, элемент задержки, третий элемент «ИЛИ два элемента «ИЛИ-НЕ 2л элементов памяти, элементов «НЕ, двухвходовых элементов «И, 2«+1 трехвходовых элементов «И, причем выход второго элемента «ИЛИ соединен со входом элемента «НЕ и с первыми входами первых п трехвходовых элементов «И, вторые входы которых соединены с шинами питания соответствующих резервируемых блоков, а третьи входы - с выходом первого элемента «ИЛИ-НЕ и с одним из входов третьего элемента «ИЛИ, другие входы которого соединены с выходами вторых п двухвходовых элементов «И, выход элемента «НЕ соединен с первым входом трехвходового элемента «И, второй вход которого соединен с выходом третьего элемента «ИЛИ, третий вход - с выходом второго элемента «ИЛИ-НЕ, а выход соединен со входом элемента задержки и с первыми входами вторых я трехвходовых элементов «И, вторые входы которых соединены с выходами соответствующих элементов «НЕ, входы которых соединены с щннами питания соответствующих резервируемых блоков, а третьи входы - с выходами соответствующих первых п элементов памяти и первыми входами соответствующих вторых п двухвходовых элементов «И, вторые входы которых соединены с тинами питания соответствующи резервируемых блоков, а также с входами первого элемента «ИЛИ-НЕ, а выходы вторых п трехвходовых элементов «И соединены с информационными входами соответствующих вторых п элементов памяти, входы которых соединены с первыми входами соответствующих третьих п двухвходовых элементов «И, вторые входы которых соединены с щинами питания соответствующих резервируемых блоков, а выходы - с входами второго элемента «ИЛИ-НЕ, выход элемента задержки соединен с входами установки исходного состояния соответствующих первых п элементов памяти, информационные входы которых соединены с выходами соответствующих вторых п трехвходовых элементов «И, и с входом элемента «НЕ, выход которого соединен с первым входом двухвходового элемента «И, второй вход которого соединен с выходом генератора импульсов, а выход - со входом счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройства для управления переключениемРЕзЕРВА | 1979 |

|

SU822391A1 |

| Устройство для управления переключением резерва | 1974 |

|

SU549809A1 |

| АДАПТИВНОЕ РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО | 2000 |

|

RU2210806C2 |

| Мажоритарное устройство | 1981 |

|

SU1096767A1 |

| Трехканальное мажоритарно-резервированное устройство | 1990 |

|

SU1764202A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Резервированная система | 1982 |

|

SU1089771A1 |

| Многоканальное устройство управления резервированной системой | 1979 |

|

SU866558A2 |

| Резервированное многокаскадное устройство | 1981 |

|

SU1069203A1 |

| Устройство для управления переключением резерва | 1975 |

|

SU552737A1 |

Авторы

Даты

1977-02-15—Публикация

1974-07-30—Подача