Изрбретение относится к автоматике и вычислительной технике/ а именно к многоканальным устройствам управления резервированной системой. По основному авт. св. 526893 из вестно многоканальное устройство управления резервированной системой, с держащее коммутаторы, управляювдае по дачей питания и входами резервных блоков, каналы управления, входы которых соединены с соответствующими выходами блоков устройства, а выходы фор1«ируют канальные 1выходы устройства и управляют коммутаторс1ми, в состав казвдого канала при этом входят первьЮ элемент ИЛИ, формирующий эы ход кансша, группа элементов И-НЕ, группа элементов И и второй элемент ИЛИ, составля а ие схему определения НеисправностиV первый и второй счетчики с дешифраторами, первый и второй элементы И, третий и четвертый элементы ИЛИ, первый и второй RS-три геры и первый и второй мультиилексоры, обеспечивающие работу устройст ва по принципу скользящего резерва ЧИ. Недостатками известного устройства являются недостаточная надежность и быстродействие. Целью изобретения является повышение надежности и увеличение быстро- действия. Поставленная цель достигается тем, что устройство содержит блок памяти, : первая группа входов которого соеди-f нена с запусканвдими выходами когдалутаторов,группа запускагацих выходов - с вторыми группами входов каналов вто- рая группа входов - с выходами эле- . . ментов И групп элементов И схем определения . неисправности каждого канала, третья группа входов - с выходами последних разрядов первых счётчиков каждого Канала, а установочный вход с шиной установки исходного состояния блока памяти. Блок памяти содер- жит группу элементов И7Т1, первую и вторую группы RS-триггеров, первую и вторую группы элементов И, группу элементов задержки, группу элементов индикации .и элемент ИЛИ, при этом входы каждого из элементов групшж элементов ИЛИ Соединены-с соответствуюп иш входами второй группы входов блока, а выход каждого элемента ИЛИ подключен к S-входу соответствующего триггера первой группы RSтрйггеров и входу роответствующего элемента группы элементов задержки,

выход которого соединен с первым входом соответствуняцего элемента первой группы элементов И, второй вход последнего подключен к прямому выходу соответствующего триггера первой группы RS-триггеров, а выход подключен к S-входу соответствующего триггера второй группы RS-триггеров, прямой выход которого соелине:н с входом соответствующего элемента группы элементов индикации, а инверсный выход - с первым входом элемента второй группы элементов И, второй вход которого подключен к соответствующему входу первой группы входов блока, а выход - к соответствующему выходу группы эапускающих выходов блока, первые R-входы всех триггеров соединены с установочным входом блока памяти, а вторые R-входы триггеров первой группы RS-триггеров чере элемент ИЛИ подключены к третьей группе входов блока.

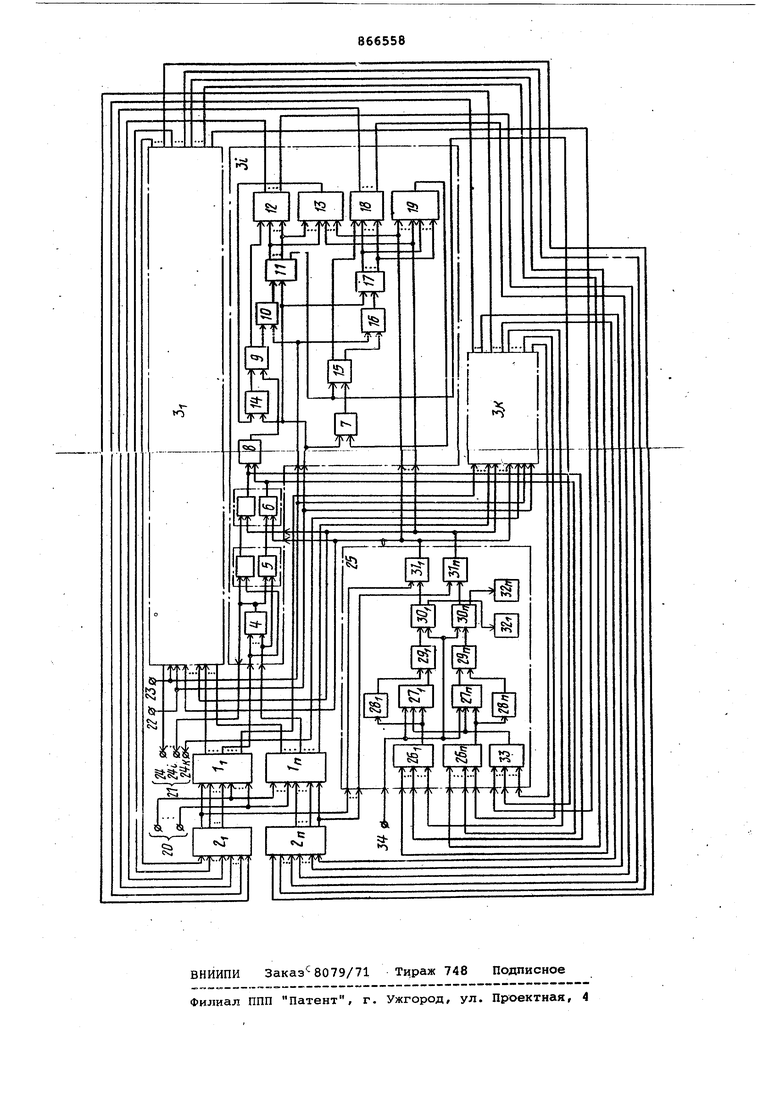

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит резервные блоки 1у-1, коммутаторы 2.-2, каналы ,, а каждый канал содержит элемент 4 ИЛИ, группу 5 элементов И-НЕ, группу б элементов И, элементы 7 и 8 ИЛИ, RS-триггер 9, элемент 10 И, счетчик 11,. дешифратор 12, мультиплесор 13, элемент 14 ИЛИ, RS-триггер 15, элемент 16 И, счетчик 17, дешифратор 18, мультиплексор 19, группы 20 и 21 соответственно, входов и выходов устройства, установочный 22 и тактовый 23 входы устройства и выходы каналов.

Кроме того, устройство содержит блок 25 памяти, состоящий из группы элементов 26 -26иИЛИ, первой группы RS-триггеров , группы элементов задержки, первой группы элементов 29 29 И, второй группы Rg-триггеров 30(-30и, второй группы элементов 31 -31,И, группы элементов индикации, элемента 33 ИЛИ и установочный вход 34 блока памяти.

Устройство работает следующим образом.

Выходные канальные сигналы с блоков 1.-1„ резервируемой системы поступают на соответствующие первые групы входов каналов - на элементы 4 ИЛИ - для канала и на первые вход элементов группы 5 элементов И-НЕ, вторые входы которых соединены с выходом элемента 4 ИЛИ и выходом 24 данного канала. Сигналы несовпадения с выходов элементов группы 5 элементов И-НЕ поступают на первые входы элементов группы 6 элементов И, вторые входы которых соединены с второй группой входов соответствующего канала, соединенной с запускающи:ли выходами блока 25 памяти, первая группа входов которого подключена к запускакицим выходам коммутаторов 2 -2, соединенным с запускаемыми входами резервируемых блоков 1. -L.

С выходов элементов группы 6 -элементов И сигналы несовпадения постуJ пают на входы элементов 8 ИЛИ и на вторую группу входов блока 25 и на входы элементов группы 26. -26, элементов ИЛИ. Причем сигналы несовпадения с вйходов j-ых элементов И групQ пы 6 каждого канала поступают на входы j-oro элемента ИЛИ группы 2 , выход которого управляет S-входом j-oro триггера группы 2, -27j, RS-триггеров и входом j-oro элемента группы 28 -2В элементов задержки. Прямой

5 выход j-oro триггера группы 27j -27,, разрешает прохождение сигнала с выхода j-oro элемента задержки группы ) на Б-вход j-oro триггера группы RS-триггеров, прямой выход которого управляет j-ым элементом группы 32 -32VI элементов индикации, а инверсный выход разрешает прохождение сигнала с j-oro входа первой группы входов блока 25, подключенного к выходу j-oro коммутатора из группы , через j-ый элемент группы 31j-31 элементов И на соответствующий запускающий выход блока 25.

Q Су(®«арный сигнал несовпадения с выхода элемента 8 ИЛИ канала 3j поступает на S-вход триггера 9,прямой выход которого разрешает прохождение через элемент 10 И на счетный вход

5 первого счетчика 11 пачки тактовой частоты данного канала с тактового входа 23 устройства. С выходов каждого разряда счетчика 11 сигналы поступают- на первый дешифратор 12, управляющий вход которого соединен

с инверсным выходом триггера 9. Кроме того, выходы счетчика 11 соединены с первой группой входов первого мультиплексора 13, вторая группа входов которого подключена к запускаю5 Щим выходам блока 25 памяти, а выход через элемент 14 ИЛИ управляет R-входом триггера 9.

Импульсы переносов с последних разрядов канальных счетчиков 11 поступают на 8-входы канальных триггеров 15 на третью группу входов блока 25 и далее через элемент 33 ИЛИ на вторые .Н-входы триггеров группы , RS-триггеров. Прямой выход

г триггера 15 разрешает прохождение через элемент 16 И на счетный вход второго счетчика 17 пачки тактовой частоты данного канала с тактового входа 23 устройства.

С выходов каждого разряда счетчика 17 сигналы поступают на второй дешифратор 18, управляющий вход которого соединен с инверсным выходом триггера 15. Кроме того, выходы |счетчика 17 соединены с первой групг

5 той входов второго мультиплексора 9, вторая группа входов которого подключена к запускающим выходам блока 25 памяти, а выход через элемент 7 ИЛИ управляет R-входом триггера 15. Выходы дешифраторов 12 и 18 в зависимости от состояния счетчиков 11 и 17 управляют подачей общего и канального питания с коммутаторов .на блоки включая их и подключая к соответствующим каналам, а также управляя соответствую щими канальными входами группы входов 20 устройства. Установка исходного ссмзтояния уст ройства осуществляется подачей соответствующего сигнала с установочного входа 22 устройства на R-входы тригг ров 9 и 15 через элементы ИЛИ 14 и 7 соответственно, а также на входы установки исходного состояния счетчико 11 и 17. Установка исходного состояния триггеров 2 7у, и 3Q, -30 25 памяти осуществляется подачей соответствующего сигнала на их первые R-входы с установочного входа 34, Тактовый вход 23 устройства выдает пачки канальных тактовых частот разделенных по времени. Пусть в начальный момент времени, после прохождения сигнала установки с установочных входов 22 и 34 триггеры 9, 15, 27 27 и 30 -30j,ycTaновлены в нулевые состояния, а счетчики 11 и 17 находятся в таких состояниях, при которых дешифраторы 12 и 18, выходы которых открыты инверсными выходс1ми триггеров 9 и 15, соответственно, выдают на коммутаторы 2 -2 у, сигналы. ir подключающие к канаустройства и разрешающие прохождение на их вход входного сигнала по входу канала 3; из группы 20 входов устройства. Элементы И 31 -31J, при эток также открыты инверсными выходами триггеров , для прохождения сигналов с коммутаторов 2 -2j, на входы соответствующих элементов груп пы 6 элементов И и на вторые группы мультиплексоров 13 и 19. При исправном состоянии рабочих блоков канала 3; узел определения неисправностей, состоящий из группы 5 элементов И-НЕ группы 6 элементов И- и элемента 8 ИЛ не выдает сигнала на S-вход триггера 9, а следовательно, на счетные входы счетчиков 11 и 17 не поступают на им пульсы из пачки тактовой частоты данного канала и они, так же как и все триггеры устройства, сохраняют свои исходные состоя)1ия. В итоге блоки из 1 -ly. для канала 3 остаются включенными. Аналогично исходное состояние сохраняется и для остгшьных (k - 1) кансшов системы. Пусть вследствие неисгфавности од ного из блоков I:,-IH например работаюцего на канал 3, узел определения ненсправностей канала Щ выдает сигнал, например по цепи j-ый элемент И-НЕ группы 5 - j-ый элемент И группы 6 - элемент 8 ИЛИ на S-вход .триггера 9, а также с выхода элемента. И группы 6 через j-ый элемент ИЛИ группы ,, на S-вход j-6ro триггера группы и вход j-oro элемента задержки группы 28. -28), . Прямой выход триггера 9 открывает при этом элемент-10 И для прохождения импульсов из пачки тактовой частоты данного канала на счетный вход счетчика 11, а инверсный выход триггера 9 выдает сигнал на дешифратор 12, запрещающий прохождение с его выходов команд на коммутаторы ра время -поиска невключенного блока J13 резерва системы, отключая при этом первый из двух блоков, работающих на канал 3j устройства С каждым тактом та товой частоты счетчик 11 меняет свое состояние и осуществляет через первую группу входов мультиплексора 13 последовательный опрос последнегос целью выборки невключенного блока из (п - k) резервных. Когда состояние счетчика соответствует коду невключенного блока, мультиплексор выдает сигнал через элемент 14 ИЛИ Нс4 R-вход триггера 9, перебрасывая его в инверсное состояние и запрещая тем caiviHM прохождение через элемент 10 И тактовой частоты на счетный вход счетчика 11, фиксируя этим данное состояние последнего, соответствующее коду найденного невключенного блока резерва. С инверсного выхода триггера 9 при этом на вход дешифратора 12 поступает сигнал, разрешающий прохождение с его выхода команды на коммутаторы 2..-2,, подключая тем сам1да найденный блок к данному кансшу. Если в.канале сбой происходит изза неисправности второго блока, в этом случае происходит переполнение счетчика 11 и на S-вход триггера 15 проходит импульс переноса с выхода последнего разряда счетчика 11, перебрасывая его в прямое со тояние. Этот же импульс поступает через элемент 33 ИЛИ на R-вход j-oro триггера группы , перебрасывая триггер в инверсное состояние. Прямое состояние триггера 15 открывает элемент 16 И для прохождения импульсов из пачки тактовой частоты данного канала на счетный вход счетчика 17, а также выдавая сигнал на дешифратор 18, запрещаквдий прохождение с его выходов на коммутаторы 2 - 2 на Бремя поиска невключенного блока из резерва системы, и выключая при этом второй из блоков, работающих на канал 3i. С каждым та.:том тактовой частоты счетчик 17 мрняет свое состояние и осущестляет через первую группу входов мультиплексора 19 по-

следовательную выборку невключениого блока из резерва системы.

Когда состояние счетчика соответствует коду невключенного блока, муль типлексор 19 вьвдает сигнал-через элемент 7 ИЛИ на R-вход триггера 15, перебрасывая его в состояние О, закрывая тем самым элемент 16 И для прохождения трактовой частоты на счетный вход счетчика 17 и фиксируя,тем самым, данное состояние последнего, соответствующее коду найденного невключённого блока резерва. С инверсного выхода триггера этом на вход дешифратора iS поступает сигнал, разрешающий прохождение с его выхода команды на коммутаторы 2 -2у,, подключая тем самым найденный блок из резер ва на место второго неисп завного блока данного канала устройства.

Блок памятиРаботает при эхом следунидим образом.

.Сигнал неисправности, поступивший на S-вход j-oro триггера группы 27,-27у, , перебрасывает его в прямое состояние, разрешакяцее прохождение задержанного на время -г сигнала неисправности с выхода j-oro элемента группы 28, -2ЗУ, элемен ов задержки через элемент И группы 29 29, на S-вход j-oro триггера группы , перебрасывая последний в прямое состояние. Данное .состояние триггера группы 30.-30 обеспечивает подачу сигнала на сЬответствукяциЙ элемент группы 32.-32 элементов индикации, включение которого показывает номер неисправного блока, подлежащего восстановлению. Кроме того, данное состояние триггера группы 30,-30, запрещает прохождение сигналов с j-юго коммутатора 2,-2}, на j-ые входы второй группы входов всех канальных мультиплексоров 13 и 19 и на вторые входы j-ых элементов группы 6 элементов И,что обеспечивает noci тЬянное отключение j-oro неисправного блока из системы блоков ,.

Время задержки х элементов 28 28, выбирается с учетом перекрытия максимального по времени одного цикла перебора блоков резерва и замещения неисправного блока в канале (V)i,on) T.e.lTj: Тщлу, Если сбой в канале произошел из-за неисправности второго блока из работающих в данном канале требуется второй цикл работы канаа управления, импульс переноса со . счетчика 11, поступая на R-вход триг- гера группы: 27,-27, вновь возвращат его в исходное инверсное состоя ie и сигнал неисправности не прохоит на S-вход j-oro триггера группы . В этом случае на втору руппу входов блока 25 поступает игнал неисправности с некоторого -ого элемента группы 6 элеместов И хемы определения неисправности -oro канала и далее через .-ый

элемент группы ,, элементов ИЛИна S-вход Е-ого триггера группы 2 27ц и вход элемента задержки группы ,1. С выхода элемента задержки данный сигнал поступает через 1-ый элемент И группы ма В-вход t-oro триггера группы , и перебрасывает последний в прямое состояние, которое обеспечивает подачу сигнала на соответствующий индикатор из группы 32,-32. Прямое

состояние триггера группы 30 30,. запрещает также прохождение сигнгша с Е-ого коммутатора группы 2.-2, на -ые входы второй группы входов всех канальных мультиплексоров 13 и 19 и на вторые входы Х-ых .злементов группы 6 элементов И, что обеспе- чивает постоянное отключение f-oro: неисправного блока из системы блоков . В результате неисправный блок выявлен, а его дальнейшее использование исключено до подачи сигнала установки исходного состояния блока 25 по шине 33. Если система работает циклично с отключением питания, для постоянного запоминания отказавшего блока вместо элементов Пс1мяти второй группы RS-триггеров 30. -30„ можно использовать элементы, состояния которых не зависят от питгиощего напряжения, например поляризованные реле. Остальные каналы системы работают аналогично рассмотренному случаю работы канала 3J.

Введение указенн{лх блоков и связей в устройство позволяет обеспечить индикацию неисправных блоков системы с целью их последукндего

:оперативного восстановления, а также исключает возможность их повторного использования.

Следовательно, изобретение обеспечийает повышение надежности системы в целом и увеличение быстродейстВИЯ устройства переключения резерва.

Формула изобретения

1. Многоканальное устройство управления резервированной системой по авт. св. О 526893, о т л и ч а Ю щ е е с я тем, что, с целью повышения надежности и увеличения быстродействия, оно содержит блок памяти, первая группа входов которого соединена с запускакхцими выходами комму таторов, группа запускающих входов с вторыми rpynncUioi входов каналов, вторая группа входов - с выходами элементов И групп элементов И схем определения неисправности кгикдого канала, третья группа входов - с выходс1ми последних разрядов первых счетчиков каждого кангша, а установочный вход - с шиной установки исходного состояния блока памяти.

2. Устройство по п. 1, отличающееся тем, что блок памяти содержит группу элементов ИЛИ, первую и вторую группы RS-триггеров, и вторую группы элементов И, группу элементов задержки, группу элементов индикации и элемент или, при этом входы каждого из элементов группы элементов ИЛИ слединены с соответствующими входами второй группы входов блока, а выход каждого элемента ИЛИ подключен к S-входу соответствующего триггера первой группы RS-триггеров и входу соответствующег элемента группы элементов задержки, выход которого соединен с первым входом соответствующего элемента первой группы элементов И, второй вход последнего подключён к прямому выходу соответствующего триггера первой группы RS-триггеров, а выход подключен к S-входу соответствующего тригrepai второй группы RS-триггеров, прямой выход которого соединен с входом соответствующего элемента группы элементов индикации, а инверсный выход - с первым яходом элемента второй группы элементов И, -второй вход которого подклк чен к соответствующему входу первой группы входов блока, а выхо - к соответствующему выходу группы запускающих выходов блока, первые R-входы всех триггеров соеди0нены с установочным входом блока памяти, а вторые R-входы триггеров первой группы RS-триггеров через элемент ИЛИ подключены к третьей группе входов блока.

5

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 526893, кл: G 06 F 9/00, 1975

0 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство управления резервированной системой | 1975 |

|

SU526893A1 |

| Многоканальное устройство управления резервированной системой | 1978 |

|

SU744571A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Устройство для контроля электронных устройств | 1984 |

|

SU1231505A1 |

| Система передачи и приема информации рекуррентными последовательностями | 1985 |

|

SU1338101A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СООБЩЕНИЙ | 1991 |

|

RU2013867C1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Устройство для контроля счетчика | 1982 |

|

SU1048579A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

Авторы

Даты

1981-09-23—Публикация

1979-11-21—Подача