выход которого подключен к другим узлам определения величины проекций сигнала.

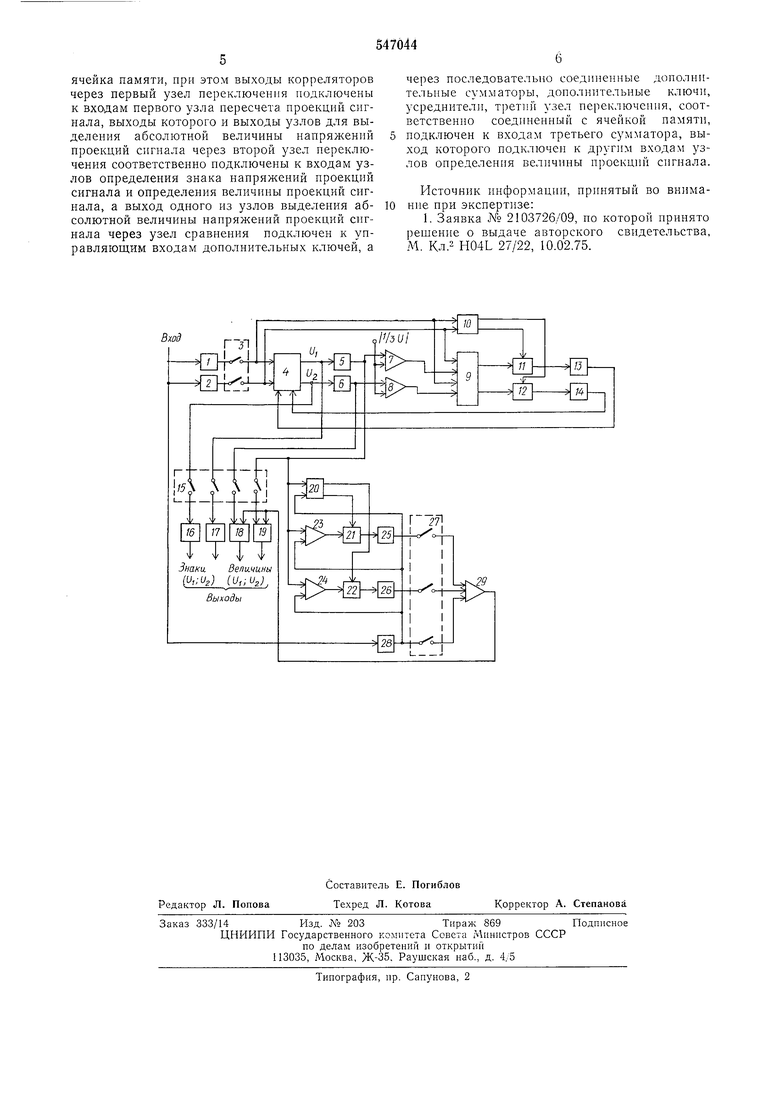

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство содержит объединенные ио входу корреляторы 1 и 2, нри этом выходы корреляторов 1 и 2 через первый узел 3 переключения подключены к входам узла 4 пересчета проекций сигнала, выходы которого соединены с входами узлов 5 и 6 для выделения абсолютной величины напряжений проекций сигнала. Выходы узлов 5 и 6 соединены с входами сумматоров 7 и 8, на вторые входы последних подано постоянное напряжение, и их выходы соединены с входами второго узла 9 пересчета нроекций сигнала, его другие входы подключены к входам узла 10 оиределения наименьшей величины сигнала, входы которого также соединены с входами первого узла 4 пересчета проекцийсигнала. Выходы узла 10 оиределения подключены к управляющим входам ключей И и 12, включенных между выходами второго узла 9 иересчета ироекций сигнала и входами интеграторов 13 н 14, выходы которых подключены к другим входам первого узла 4 пересчета. Выходы последнего и выходы узлов 5 и 6 для выделения абсолютной величины напряжений проекций сигнала через второй узел 15 переключення соответственно подключены к входам узлов 16, 17 и 18, 19 определения знака напряжений ироекций сигнала н определения величины проекций сигнала соответственно, а выход узла 5 выделения абсолютной величины наиряжений проекций сигнала через узел 20 сравнения нодключен к уиравляющим входам дополнительных ключей 21 и 22, а через последовательно соединенные дополнительные сумматоры 23 и 24, дополнительные ключи 21 и 22, усредннтелн 25 и 26, третий узел 27 переключення соответственно, соеднненный с ячейкой памяти 28, подключен к входам третьего сумматора 29, выход которого подключен к другим входам узлов 18 и 19 определения величины нроекций сигнала. Устройство работает следующим образом. Узлы 3 и 15 переключения разбивают процесс детектировання на два цикла.

В течение иервого цнкла онределяется величина напряжения порога сравнения для узлов ГВ и 19 определения величин проекций сигнала, для чего выход узла 5 выделения абсолютной величины проекций сигнала подключается к объединенным входам дополнительных сумматоров 23 и 24, на вторые входы которых подается напряжение, снимаемое с выхода ячейки памяти 28. На этих входах сумматоров 23 и 24 формируются соответственно напряжения 1/3 Un и Ua, необходимые для сравнения в сумматорах с абсолютной величиной нроекций сигналов.

Результирующие напряжения с выходов сумматоров 23 и 24 через дополнительные ключи 21 и 22 подаются на входы усреднителей 25 и 26. Ключи 21 и 22 управляются узлом 20 сравнения, который сравнивает напряжения

абсолютных величин проекций, поступающих на объединенные входы сумматоров 23 и 24, с

оиорным напряжением, равным - и сфорО

5 мированиым из наиряжения, поступающего с выхода ячейки памяти 28. По результату сравиеиия онределяется выход какого из сумматоров 23 и 24 иодключить к усреднителю.

Выходы усреднителей 25 и 26 и выход ячейки памяти 28 в конце первого цикла узлом переключения 27 подключаются к входам третьего дополнительного сумматора 29, заверщающего онределение нанряжения порога сравнения для узлов 18 и 19 определения величины

15 нроекций сигнала.

Значение напряжения порога запоминается в ячейке памяти сумматора 29, после чего производится сброс в интеграторах усреднителей 25 и 26, т. е. подготавливаются усреднители к

20 новому циклу.

На втором цикле детектирования узла 15 переключения подключает узлы 16 и 17 определения знака нанряжения нроекций сигнала к выходам первого узла 4 иересчета нроекций, а

5 узлы 18 и 19 определения величины проекций сигнала, на которые подается с ячейки памяти сумматора 29 напряжение порога сравнения, - к выходам узлов 5 и 6 выделения абсолютной величины проекций сигнала.

0 В течение этого цикла узлы 16 и 17 определяют знаки проекций сигнала на оси приемника, а узлы 18 и 19 - величины этих нроекций. Таким образом, уменьшается вероятность ошибки детектирования при кратковременных

5 изменениях уровня сигнала в канале связи, что повышает точность детектирования.

Формула изобретения

0 Устройство для детектирования сигналов, содержащее объединенные но входу корреляторы, а также иоследовательно соединенные узел иересчета проекций сигнала, к входам которого подключены входы узла определения наименьшей величины сигнала, узлы для выделения абсолютной величины напряжений проекций сигнала, сумматоры, второй узел пересчета проекций сигнала, другие входы которого подключены ко входам узла определения наименьшей величины сигнала, ключи, к унравляющим входам которых подключены выходы узла определения наименьшей величины сигнала, и интеграторы, выходы которых подключены к другим входам первого узла пересчета

5 проекций сигнала, и узел определения величин проекций сигнала и узел определения знака напряжений проекций сигнала, отличающееся тем, что, с целью повышения точности детектирования за счет уменьшения вероятности

ошибки детектирования сигналов с четырехкратной амплитудно-фазовой манипуляцией при воздействии кратковременных изменений уровня в канале связи, введены узлы переключения, узел сравнения, донолнительные ключи,

усреднители, дополиительные сумматоры и

ячейка памяти, при этом выходы корреляторов через первый узел переключения подключены к входам первого узла пересчета проекций сигнала, выходы которого и выходы узлов для выделения абсолютной величины напряжений проекций сигнала через второй узел переключения соответственно подключены к входам узлов определения знака напряжений проекций сигнала и определения величины проекций сигнала, а выход одного из узлов выделения абсолютной величины напряжений проекций сигнала через узел сравнения подкотючен к управляющим входам дополнительных ключей, а

через последовательно соединенные дополнительные сумматоры, донолнительные ключи, усреднители, третий узел переключения, соответственно соединенный с ячейкой памяти, подключен к входам третьего сумматора, выход которого подключен к другим входам узлов определеппя величины проекций спгнала.

Источник информации, принятый во вн 1манне при экспертизе:

1. Заявка № 2103726/09, по которой припято регнеппе о выдаче авторского свпдетельства, М. Кл.2 H04L 27/22, 10.02.75.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для детекрирования сигналов | 1975 |

|

SU543195A1 |

| Частотный дискриминатор | 1977 |

|

SU708503A2 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1051737A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1977 |

|

SU733117A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1042203A1 |

| Устройство для детектирования фазоманипулированных сигналов двукратной относительной фазовой манипуляции | 1973 |

|

SU491187A1 |

| Устройство для детектирования амплитудно-фазомодулированных сигналов | 1984 |

|

SU1292202A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1978 |

|

SU786047A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1984 |

|

SU1216834A1 |

Вход

Авторы

Даты

1977-02-15—Публикация

1975-04-07—Подача