(54) ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое делительное устройство | 1980 |

|

SU957224A1 |

| Множительное устройство | 1975 |

|

SU547782A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Множительно-делительное устройство широтно-модулированных сигналов | 1983 |

|

SU1095196A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| Релейный усилитель | 1977 |

|

SU660062A1 |

| Множительно-делительное устройство | 1981 |

|

SU995098A1 |

| Широтно-импульсный операционный усилитель | 1975 |

|

SU547778A1 |

| Множительное устройство | 1979 |

|

SU822204A1 |

| Множительно-делительное устройство | 1976 |

|

SU752364A1 |

1

Изобретение относится к время-импульсным вычислительным устройствам и может быть использовано в вычислительных машинах, в устройствах промышленной автоматики

Одно из известных делительных устройств время-импульсного типа содержит последовательно соединенные интегратор, элемент сравнения, усилительный элемент, широтноимлульсный модулятор l .

Это устройство имеет сравнительно ниэкую точность работы.

Из известных устройств аналогичного назначения наиболее близким к предложенному является делительное устройство, содержаш:ее соединенные последовательно интегратор, ре- лейный элемент и первый множительный блок выход которого через операторный резистор обратной связи подключен ко входу интегратора, выход релейного элемента соединен со входом второго множительного блока, вход интегратора через масштабирующий резистор подключен к выводу источника сигнала-делимого, второй вход первого множительного блока присоединен к выводу источника сигнала-делителя 2 .

Однако и это устройство имеет невысокую точность вьтолнения вычислительной операции вследствие изменения частоты следования выходных импульсов.

Целью изобретения является повышение точности работы устройства.

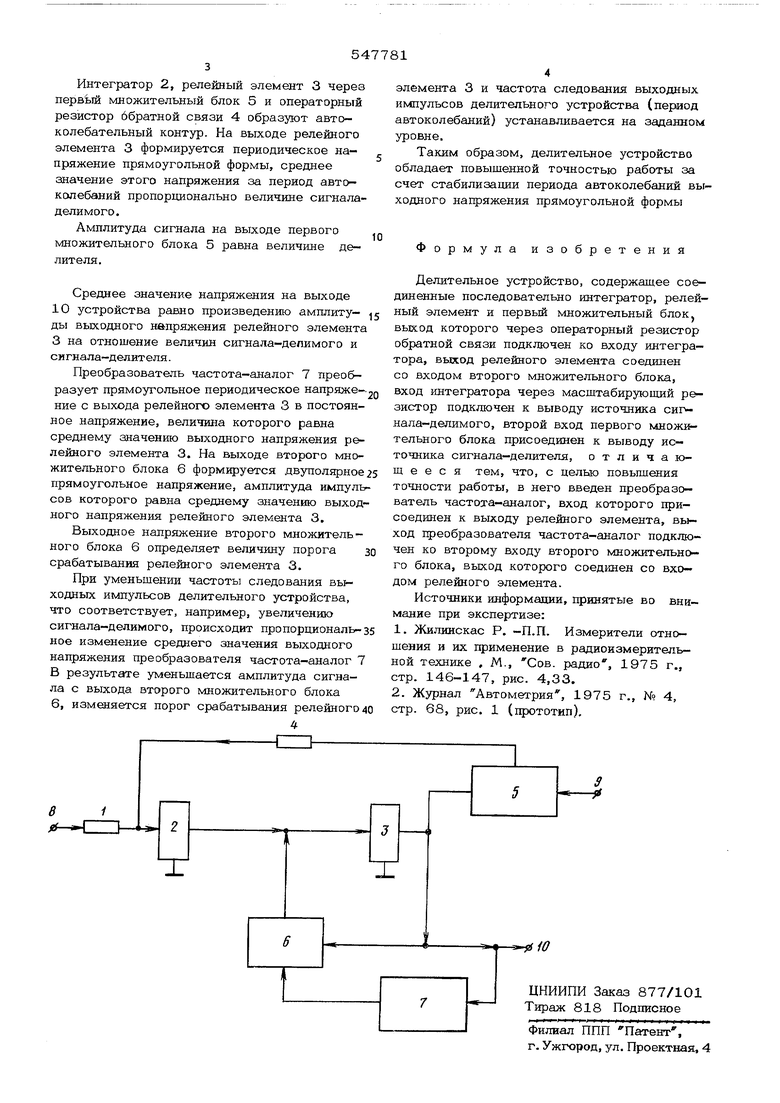

Это достигается тем, что в предлагаемое устройство введен преобразователь частота-аналог, вход которого присоединен к выходу релейного элемента, выход преобразователя частота-аналог подключен ко второму входу второго множительного блока, выход которого соединен со входом релейного элемента.

На чертеже изображена блок-схема делительного устройства.

Оно содержит масштабирующий резистор 1, интегратор 2, релейный элемент 3, операторный резистор обратной связи 4, первый множительный блок 5, второй множительный блок 6, тфеобразователь частота-аналог 7 вывод источника сигнала-делимого 8, вывод источника сигнала-делителя 9, выход 10 устройства.

Устройство работает следующим образом.

Авторы

Даты

1977-02-25—Публикация

1975-12-18—Подача