1

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных и управляющих комплексах в качестве вычислительного устройства, совер- 5 шающего математические операции над сигналами, представленными в частотно-импульсной форме.

Известно множитёльно-делительное устройство 1, содержащее первый 10 и второй элементы И и два триггера, составляющие логическое триггерное кольцо, выход которого соединен с выходом третьего элемента И.

Недостатком такого устройства |5 является наличие пульсации в выходном сигнале.

Наиболее близким по технической сущности к изобретению является частотно-импульсное множительно-дели- 20 тельное устройство 2 , содержащее первый.и второй множительно-делительные узлы, реверсивный счетчик, суммирующий счетчик, блок умножения, причем выходы первого и второго мно- 25 жительно-делительных узлов соединены соответственно со входами сложения и вычитания реверсивного счетчика, выходы которого соединены с первой группой входов блока умножения, вто- ЗО

рая группа входов блока умножения соединена с выходами суммирующего счетчика, счетный вход которого соединен с выходной шиной опорной частоты устройства, входы первого и второго сомножителей первого множительно-делительного узла соединены соответственно с входной шиной первого сомножителя устройства и шиной первого масштабирующего сигнала устройства, вход делителя второго иножительно-делительного узла соединен с шиной второго сомножителя устройства, выход блока умножения соединен с выходной шиной устройства и входом первого сомножителя второго множитёльно-делительного узла, вход делителя первого множительно-делительного узла соединен с шиной делителя устройства, вход второго сомножителя второго множительно-делительного узла соединен с шиной второго масштабирующего сигнала.

В данном устройстве, обладающем моделирующей зависимостью

РЛ

(1)

V

ч оа

частоты импульсных последовательностей FO, и FO являются постоянными

неравными величинами,либо их отношение соответствует масштабному коэффициенту, а F , FQ и Fj моделируют математические величины.

При использовании известного устройства в режиме деления моделирую щая зависимость (1) может быть записана в виде

p.b,Pi..f,

(2J ог г ч

Частоты импульсных последовательностей Г и Fj моделируют делимое и делитель.

Проведенные исследования частотно-импульсного разомкнутого множительно-делительного узла (РМДУ) в направлении определения влияния пульсаций во входных сигналах F,, F и Fg/ на его точностные характеристики показали, что по входам F, и РИДУ не критично к воздействиям пульсаций. Вместе с тем наличие неравномерности в импульсной последовательности F приводит к существенным погрешностям в f РМДУ.

При величине относительной пульсации в сигнале F равной

F,-0,25; (3)

в выходном сигнале имеет место погрешность

. . (Ч)

Так как в известном устройстве 1 РМДУ включены в с и /Ь цепи, то наличие пульсаций в сигналах f и F.приведет к появлению погрешности в

FZ .

Следовательно, модель 2 может

быть использована в режиме деления только при представлении математических величин равномерными импульсными последовательностями F, и F ,

На практике приходится иметь дело с сигналами, обладающими существенной пульсацией. Величина среднеквадратического отклонения 1-южет в пределе достигать значения основного сигнала. Следовательно, в результирующей импульсной последовательности устройства согласно соотношениям (3) и С) будет иметь место погрешность, величина которой будет достигать десятков процента, что указывает на непригодность использования модели в качестве математического инструмента.

Вторым недостатком известного делительного устройства является необходимость выполнения условия

,, (1 что Накладывает ограничения на диапазоны измвенения делимого и делителя .

Целью изобретения является улюньшение величины погрешности при наличии пульсации в сигнале делителя

обеспечение независимости изменения диапазонов сигналов делителя и делимого.

Поставленная цель достигается тем, что в частотно-импульсное множительг но-делительное устройство, содержащее первый и второй множительно-делительные узлы, делитель частоты, реверсивный счетчик, блок умножения, причем выходы первого и второго множительно-делительных узлов соединены соответственно со входами сложения и вычитания реверсивного счетчика, выходы которого соединены с первой группой входов блока умножения, вторая группа входов блока умножения соединена с выходами делителя частоты, счетный вход которого соединен с входной шиной опорной частоты устройства, входы первого и второго сомножителей первого множительно0 делительного узла соединены соответственно с входной шиной делимого уст ррйства и шиной первого масштабирующего сигнала устройства, вход делителя второго множительно-делительно5 узла соединен с шиной второго масштабирующего сигнала устройства, вход блока умножения соединен с .входной шиной устройства, введены дополнительные соединения - вход

Q делителя первого множительно-делительного узла- соединен с шиной третьего масштабирующего сигнала устройства, а входы первого и второго сомножителей второго множие тельно-делительного узла соединены соответственно с шиной делителя устройства и выходом блока умножения. Это позволяет в качестве делителя использовать импульсную последовательность Г , поступающую на низкочастотный вход РМДУ цепи обратной передачи. Устройство будет функционировать нормально при наличии пульсаций в импульсных потоках F и F4, если их величины не будут превышать

5 значений частот f и F . При этом величина пульсации в {результирующем сигнале F может быть сведена до сколь угодно малой величины.

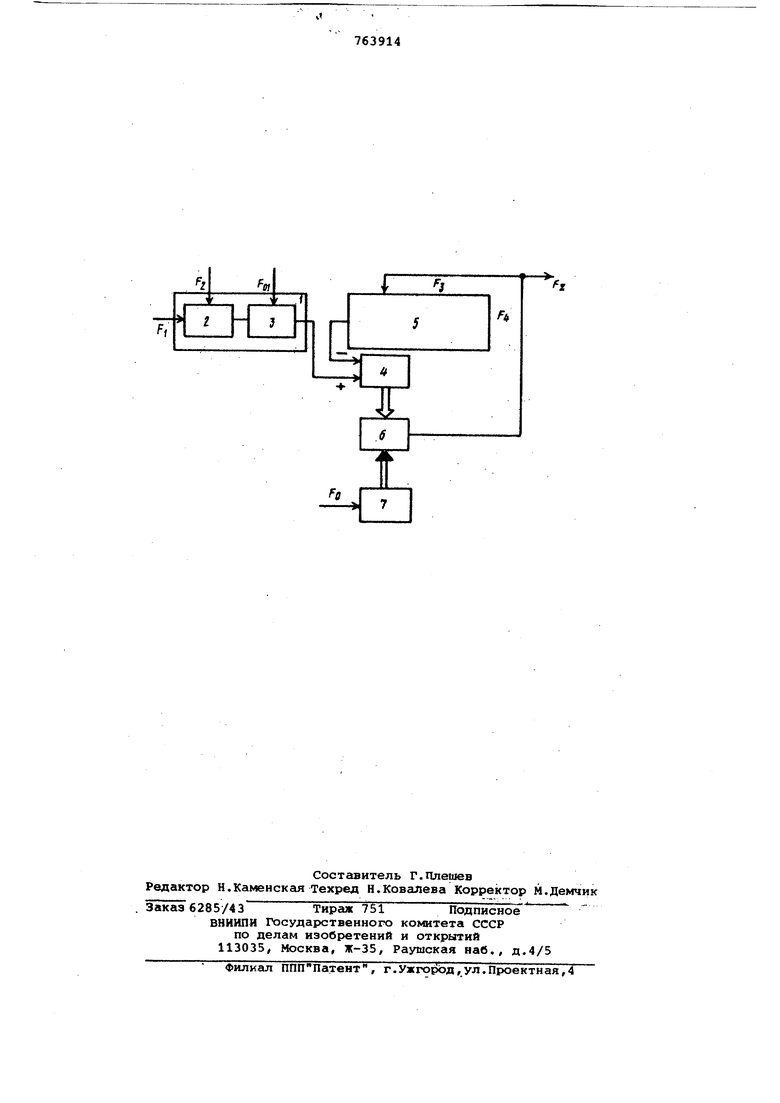

0 На чертеже представлена схема предлагаемого частотно-импульсного делительного устройства.

Устройство состоит из первого множительно-делительного узла 1,

5 включакадего логическое триггерное кольцо 2 и элемент И 3, реверсивного счетчика 4, второго множительно-делительного узла 5, блока умнодения 6, делителя частоты 7.

Устройство работает следующим образом.

С каждалм импульсом частоты F на выходе множительно-делительного узла 1, состоящего из логического

триггерного кольца 2 и элемента

И 3, формируется п импульсов, где

POIlf

%Г- - (

Следовательно, в единицу времени на суммирующую шину реверсивного счетчика 4 будет поступать п импульсов, где

и - с О1

г- тгАналогично, с каждым импульсом частоты F на выходе множительно.делительного узла 5 формируется п импульсов, где %г-- ;Следовательно, в единицу времени на вычитающую шину реверсивного сч чика 4 будет поступать п, импульсо где В режиме динамического равновесия n,:n МЛИ -- Откуда 1 Ч предлагаемое устройство работает в режиме деления, то выражение (11) примет вид Сопоставляя выражения (12) и (2), находим, что в предлагаемом устройстве входные сигналы F и F поступают на выходы триггеров логи ческих триггерных-колец 2. выше бы ло показано, что по указанным входам множительно-делительные узлы 1,5, используемые в предлагаемом устройстве соответственно в о и /Ь цепях, являются некритичными к нал чию пульсаций в сигналах. Следовательно, в предлагаемом устройстве частоты импульсных последовательностей, поступающих на суммирующую и вычитанвдую шины реве сивного счетчика 4 будут соответст вовать соотношениям (7) и (9) даже при наличии пульсаций в сигналах F, и F . Значит, и результирующая частота F. не будет подвержена влиянию пульсаций, имеющих ме то в импульсных последовательностя FI и F4 , т.е. величина погрешности Cf F, ОТ указанных фиксаторов будет стремиться к нулю. Согласно физике работы логического триггерного кольца диапазоны

изменения частот импульсных последовательностей F, и F в предлагаемом устройстве являются независимыми.

При использовании данногчэ устройства в вычислительной машине отпадает необходимость в постановке фильтра в цепь делителя при наличии пульсации в его сигнале.

Данное устройство обеспечивает независимость диапазонов изменения сигналов делителя и делимого.Следовательно, отпадает необходимость в наличии согласурхдего звена. Формула изобретения Частотно-импульсное делительное устройство, содержащее первый и .второй множительно-делительные узлы, делитель частоты, реверсивный счетчик, блок умножения, причем выходы первого и второго множительно-делительных узлов соединены соответственно со входами сложения и вычитания реверсивного счетчика, выходы которого соединены с первой группой входов блока умножения, вторая группа входов блока умножения соединена с выходами д лителя частоты, счетный вхЪд которого соединен с входной шиной опорной частоты устройства, входы первого и второго сомножителей первого множительно-делительного узла соединены соответственно с входной шиной делимого устройства и шиной первого масштабирующего сигнала устройства, вход делителя второго множительно-делительного узла соединён с шиной второго масштабирующего сигнала устройства, выход блока умноженин соединен с выходной шиной устройства, отличающееся тем, что, с целью уменьшения погрешностей при наличии пульсации в сигнале делителя и обеспечения независимости изменения диапазонов сигналов делителя и делимого, вход делителя первого множительно-делительного узла соединен с шиной третьего масштабирующего сигнала устройства, а входы первого и второго сомножителей второго множительно-делительного узла соединены соответственно с шиной делителя устройства и выходом блока умножения. Источники информации, принятые во внимание при зкспертизе 1.Авторское свидетельство СССР № 602945, кл. G 06 F 7/52, 1975. 2.Авторское свидетельство СССР 217070, кл. G Об G 7/16, 1967 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-импульсное множительно-дЕлиТЕльНОЕ уСТРОйСТВО | 1979 |

|

SU813426A1 |

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

| Устройство для перемножения двух частотно-импульсных сигналов | 1979 |

|

SU920723A1 |

| Множительно-делительное устройство | 1981 |

|

SU982002A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| Множительно-делительное устройство | 1978 |

|

SU813419A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Частотно-импульсное множительно-делительное устройство | 1975 |

|

SU556437A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

Авторы

Даты

1980-09-15—Публикация

1978-08-25—Подача