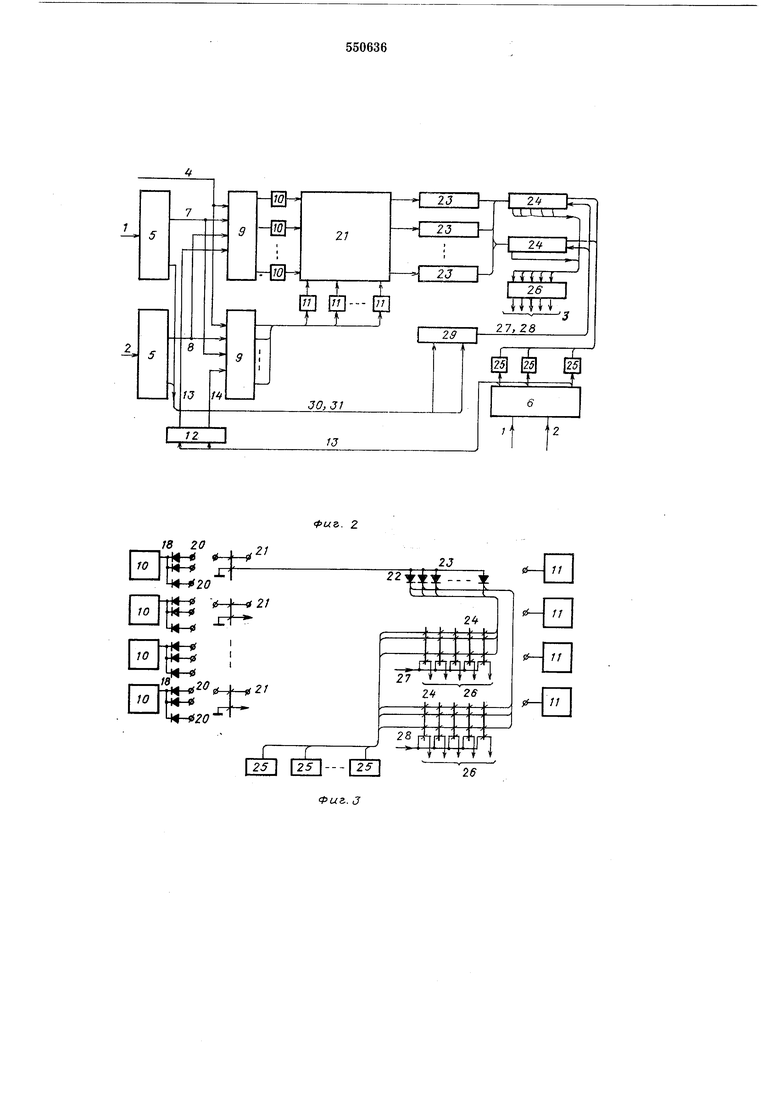

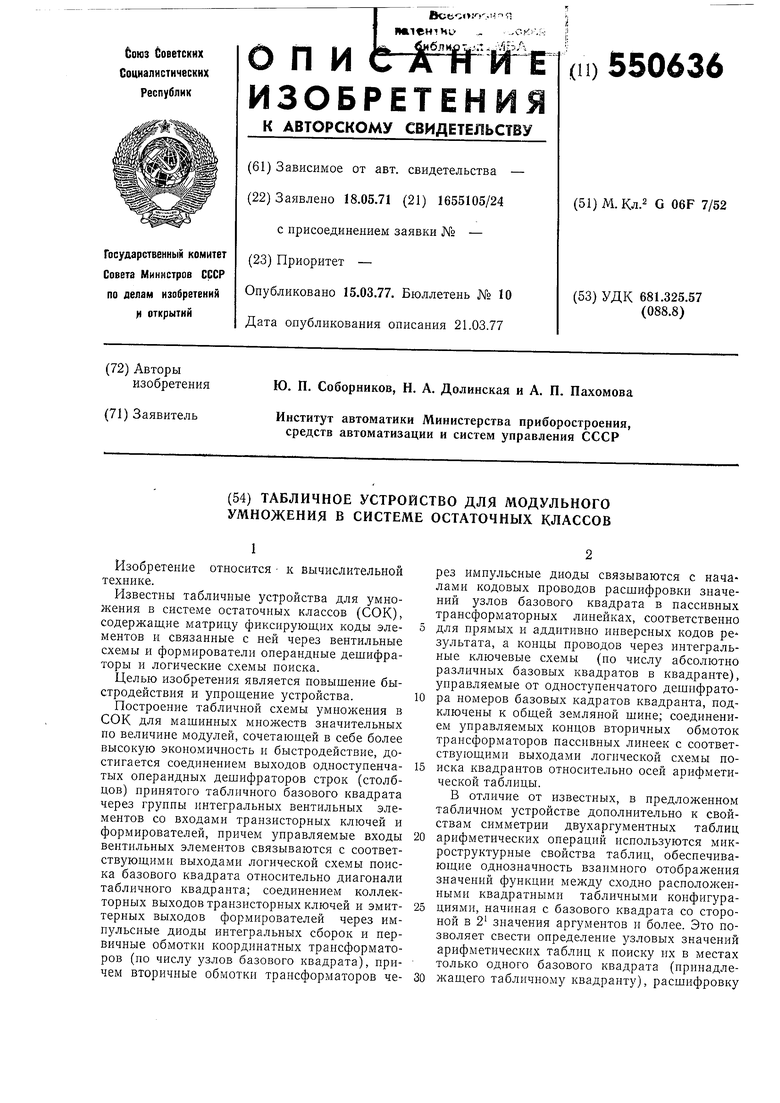

значении которых в завнснмости от номеров квадратов и квадрантов, составляющнх таблицу, с целью двукратного ускорения общего быстродействия табличной схемы производить нараллельно с поиском. Для предложенного табличного устройства для умножения используется радиотехнический принцип построения с учетом реальных задержек элементов без внутренней логической тактировки. В схеме применены квадрантно «свернутые нассивные кодовые линейки на радиочастотных ферритах (более быстродействующие, чем оперативные запоминающие ячейки на ферритах с прямоугольной нетлей гистерезиса) с экономичной занисью кодов проводниками прошивки. Практическая реализация изобретения иллюстрируется на машинном множестве взаимно простых модулей целочисленной нензбыточной СОК: 32, 31, 29, 27, 25, обеспечивающем машинный диапазон М 19418400. На фиг. 1 показана таблица умножения по модулю 29 (с акцентированием квадрантов и базовых квадратов); на фиг. 2 - функциональная схема модульного умнол :ения; на фиг. 3 - принципиальная схема поиска базовых квадратов квадрантов с последующей их расщифровкой; на фиг. 4 - принципиальная схема узла ключ - формирователь; на фиг. 5 - таблица соединений выходов ключей и формирователей (через нервичные обмотки координатно-узловых трансформаторов); на фиг. 6 - таблица неисходных грунп номеров базовых квадратов квадранта (выбираемых соответствующими ключевыми интегральными схемами). Как н обычно, в предложенной схеме модульного умножения нспользуются свойства симметрии арифметической таблицы относительно осей, проходящнх между узловыми знаmt-l m-. + l чениями для -и -; для модуля mj 29 (см. фиг. 1) оси проходят между онерандными значениями 14 и 15, образуя четыре табличных квадранта. Условно сложенная относительно горизонтальной и вертикальной осей симметрии арифметическая таблица (квадрант для операндных значений О-14 оставлен неподвижным) приобретает свойства взаимной аддитивной дополнительности значений совмещенных узлов до величины модуля, причем главная диагональ неподвижного квадранта и побочные диагонали налагаемых квадрантов, определяющие квадрантную диагональную симметрию узловых значений, совпадают. Оставшийся квадрант (для онерандных значений 15-28), симметричный относительно собственной главной днагонали, может быть сложен с неподвижным квадрантом относительно побочной диагонали таблицы (проходящей через пересечение осей симметрии) и проявляет при этом абсолютную тождественность значений совмещаемых узлов. Сказанное оиределяет возможность реализации в схеме модульного умножения только части одного квадранта (например, для онерандных значений О-14), ограниченной двумя его сторонами и главной диагональю (т. е. 120, а не 841 узловых значений). Однако в предложенной схеме умножения, за счет не использовавщихся ранее микроструктурных табличных свойств, физически реализуется только один базовый квадрат квадранта (со стороной, не менее 2 значений операнда). По соображениям минимизации общих аннаратурных затрат н наилучщего разбиения между дещифраторами и другими узлами табличной схемы донустимого временного запаздывания оптимальным базовым квадратом для машинного множества двоично-кодированных модулей {32, 31, 29, 27, 25} оказывается квадрат со стороной , « 2 (см. фиг. 1). Всем узлам нринятого базового квадрата присваиваются соответствующие порядковые номера состояний (от 1 до 16). Иснользуемые свойства табличной микроструктуры проявляются при этом в однозначности взаимных отобрал :ений соответствующих узловых значений сходно расноложенных базовых квадратных конфигураций, составляющих конкретный квадрант (так, 0-е значение узла базового квадрата 00-00, как показано на фиг. 1, взаимнооднозначно соответствует значениям 16 и 6 узлов квадратов 01-01 и 10-10, соответственно, и все три названные значения определены одним и тем же состоянием с номером 1 н т. д.). Базовые квадраты, расположенные симметрично относительно главной диагонали квадранта, характеризует абсолютная тождественность не только зеркально симметричных номеров состояний, но н собственно значений соответствующих узлов (поэтому все квадраты квадранта, включая и неполные, можно разбить только на 10, а не на 16 несходных грунн, как показано на фиг. 6). При схемной реализации единственного базового квадрата определение любого узлового значения таблицы модульного умножения сводится к поиску этого значения среди узловых мест (состояний) базового квадрата и к параллельной во времени расшифровке значения состояния (прямого либо аддитивно инверсного) в зависимости от места базового квадрата в том или ином квадранте таблицы. Отметим, что параллельный во времени поиск места базового квадрата в таблице может производиться при этом без использования операции кодового сравнения, ухудшающего временные характернстики схемы. Входы табличной схемы модульного умножения (см. фиг. 2) по кодовым цепям 1 и 2 для операндов X и Y связываются в цифровой вычислительной машине (ЦВМ) с выходами соответствующих нараллельных операндных регистров (на фиг. 2 не показаны), кодовые цепи 3 для Z - с параллельным операндным регистром, в который засылается результат модульной арифметической операции. При условии нахождения кодов операндов X и У в своих регистрах и готовности регистра

для Z к приему результата табличная схема по BHeiiineAiy сигналу управления с шины 4 срабатывает за время единичного машинного такта. Входные одноступенчатые пространственные дешифраторы 5 (ДШ1,2 - X, У) собраны на импульсных диодах интегральных сборок и служат для преобразования («сверткн) операндных аргументных кодов в десятичные коды номеров столбцов (строк) базового квадрата 00-00. Входной одноступенчатый дешифратор 6 (ДШз - X-Y служит для перобразования оиерандных кодов в номера базовых квадратов неподвижного квадранта таблицы, число которг;;х (и количество выходных цепей) в силу зеркальной симметрии узловых значений квадранта относительно собствеиной главной диагонали сокрашается с 22 до 2 -Ч2Ч-), т. е. с 16 до 10 (см. фиг. 6). Выходы (цепи) 7 и 8 дешифраторов 5 через группы интегральных вентильных элементов (ГИВЭ) 9 связаны соответственно со входами токовых транзисторных ключей 10 н формирователей J1 или, наоборот, в зависимости от расположения базового квадрата относительно диагонали квадпаита. Логическая схема (ЛСПК) 12, осун1ествля1ои1ая этот поиск, по цепям 13 соединена своими входами с соответствующими выходами дешифратора 6 номеров базовых квадратов квадранта; цепи 13 и 14 ЛСПК связаны с соответствующими управляемыми входами групп ГИВЭ 9. Ключевые транзисторы 15 и транзисторы 16 формирователей (см. фиг. 4) нормально закрыты за счет заземления базовых входов 17 через вентильные элементы ГИВЭ 9 и шнну 4 (см. фиг. 2). Транзисторы 15 и 16 в ключах 10 включены по схеме с общим эмпттером, а в формирователях 11 - с обшим коллектором. Коллекторные выходы 18 транзисторов ключей II эмнттерные выходы 19 транзисторов формирователей соединены вместе через импульсные диоды 20 интегральных сборок н первичные обмотки координатно-узловых трансфорлатопов 21 в соответствии с таблицей (см. фиг. 5). Вентильные импульсные дноды 20 первичных обмоток включены в направлении, совпадающем с проводимостью открытых ключевых транзисторов 15. В качестве вентильных диодов используются импульсные диоды интегральных сборок типа Щ-04; коордппатиые трансформаторы собраны на тороидальных сердечниках, сЬеррит марки Ml000 НМ; транзистопы ключей и формирователей - типа КТ 315А. рабочий импульсный ток - 10 мА; ДШь ДШ,, ДШз собраны на диодах интегральных сборок с учетом необходимого быстродействия, они люгут быть собраны и на стандартных интегральных схемах.

Вторичные обмотки коордннатно-узловых трансформаторов 21 через вентильные импульсные диоды 22 (по числу несходных групп базовых квадратов квадранта, равному 10 на обмотку) сборок (ДС) 23 (см. фиг. 2) соединены соответстветига с началами кодовых проводников нрошивок иассивных ферритовых линеек (ПКЛ) 24 (см. фиг. 3). Для уменьшения времени расшифровки иснользуются две пассивиые линейки (ПКЛ) 24: одна-длянрямых, другая - для аддитивно ннверсных кодов результата, в соответствии со свойствами квадрантов, симметричиых относительно осей таблицы. Общее число (36) имиульсных вентильных диодов 36 равно пронзведению числа координатно-узловых трансформаторов (УТР) груипы 21, показанной на фиг. 2 (состояний базового квадрата), на чнсло несходных групп базовых квадратов квадранта в таблице модульного умножения. Для схемной реализации

любой модульной таблицы множества (32, 31, 29, 27, 25} необходимо только 10X16 160 кодовых диодов, причем за счет временного параллелизма в поиске узлового места базового квадрата квадранта и расшифровке его значения примерно вдвое сокращается и время выборки величины произвольного табличного узла.

Вентильные диоды 22 интегральных сборок 23 (типа Щ-04) включены в направлении (см.

фиг. 2 и 3), проводящем для ключевых интегральных схем (КИ) 25 (тина 1ЛБ336 сер. 133, И 63.088.023 ТУ), с соответствуюшими коллекторными цепями которых соединены концы кодовых проводов (первичные обмоткн трансформаторов) обеих пасснвных лииеек (ПКЛ)

24.Чнсло ключевых интегральных схем (КИ)

25,входы которых связаны с управляющими выходами ДШз 6, для множества модулей (32, 31, 29, 27, 25) равно 10, а их принадлежность к расшифровке конкретной грунпы базовых квадратов квадранта отражена в таблице, прнведеиной на фиг. 6.

В проводящем состоянии КИ 25 подключают концы кодовых проводов ПКЛ 24 к общей

земляной шине. Начала вторичных обмоток трансформаторов обеих ПКЛ (см. фиг. 3, 2) соединены со входными цепями соответствующих разрядных интегральных усилителей считывания результирующих кодов (У. Сч.) 26.

Кодовые трансформаторы ПКЛ выполнены на феррнтах марки М1000 ПМ; в качестве усилителей параллельиого считывания 5-разрядиых кодовых сигналов нспользуются интегральные уснлители типа 1УБ221АК. Концы вторичных обмоток трансформаторов линеек соединяются с обшей земляной шииой соответственно через цепи 27 и 28 и логическую схему поиска квадрантов относительно осей арифметической таблицы ЛСПО 29. уиравляемые входы которой по цепям 30 и 31 связаны с выходами операндных дешифраторов ДШ1 и ДШ2. Так обеспечивается передача сигналов прямых либо аддитивно инверсных кодов результата Z на усилители У. Сч. 26 в зависимости от выбора конкретной ПКЛ 24 (квадранта таблицы). Логические схемы иоиска ЛСПК 12 и ЛСПО 29 представляют собой схемы совпадения, собранные из интегральных элементов типа «Логика-2, сер. 133,

И 63.088.023 ТУ. Выходы У. Сч. 26 связываются со входными цепями регистра для результата Z.

Предварительное занесение в оиерандные регистры кодов X и У но ценям 1 и 2 приводит в соответствующее активное состояние дешифраторы ДШь ДШ2 и ДШз 5 и 6 (см. фиг. 2), и на единственном выходе каждого из них появляется нотенниал. Потенциал с выхода ДШз б открывает одну из интегральных ключевых схем КИ 25, соединяя концы кодовых проводов обеих ПКЛ 26 для соответствующего базового квадрата (см. фиг. 6) с общей земляной шиной. Однако в приведенной в активное состояние от ДШ| и ДШз (по цепям 30 и 31) логической схеме поиска ЛСПО 29 связывается с земляной шиной только цепь 27 или 28 в зависимости от выбранного опепандными кодами табличного квадпанта. Тем самым к выдаче кодовых сигналов результата Z на усилители У. Сч. 26 подготавливается гпуппа вторичных обмоток только одной ПКЛ 24 (заземлением концов). Приведенная в активное состояние от ДШз 6 по цепям 13 схема поиска ЛСПК 12 подготавливает (по цепи 13 или 14) к включению соответствующие вентильные элементы 32 (см. фиг. 4), на входы которых по цепям 7 н 8 подаются таклсе выходные потенпналы операндных дешифраторов ДШ| и ДШг. Благодаря дополнительному воздействию потенциала с определенного выхода ЛСПК 12 в зависимости от расположения выбранного базового квадрата относительно главной диагонали квадранта, выходной сигнал трехвходовых вентильных элементов, соответствуюший потенциалу опеоандного дешифратора ДШ (ДШо), подается через разделительный элемент 33 на вход формирователей 11 или ключей 10.

При подаче импульсного управляюигего сигнала УС по цепи 4 (см. фиг. 21 транзисторы единственного ключа 10 и единственного формирователя II схемы, нредвапительно вьтбпянные с помощью ДШ,., 5 ЛСПК 12 и ГИВЭ 29, отпираются, и в первичной обмотке координатно-узлового трансформатора, обшей для ключа 10 и формирователя 11, возникает токовый импульс. Так как при этом выбирается конкретный координатный трансФопматоп из всей групц, трансформаторов (У. Тп.) 21. а единственной интегральной ключевой схемой КИ 25 предварительно включен только один из диодов 22 (см. фиг. 3 и 4), связанный со вторичной обмоткой выбранного трансформатора 21, то только по одному из кодовых проводов каждой линейки ПКЛ 24 проходит импульсный ток. При этом кодовые сигналы искомого результата онепаиии иоявляются на активных выходных обмотках только одной ПКЛ 24, коды прошивки которой соответствуют предварительно выбранному с иомошью схемы поиска ЛСПО 29 квадранту таблиттьт.

Таким образом, с активных выходов ПКЛ 24 на входы У. Сч. 26 параллельно подается группа сигналов, соответствующая единственному коду результата.

В экспериментальной схеме остаточного двоично-кодированного модульного умножения время запаздывания относительно момента подачи управляющего сигнала УС не иревышает 0,3 МКС.

Итак, отличительными признаками изобретения являются оригинальные решения (на основе дополнительного использования микрострзктурных свойств таблиц) схемы поиска

узловых значений в малом базовом квадрате и табличном квадранте, исключающие ненроизводительиое кодовое сравнение и нозволяющие ограничиться физическим фиксированием только количества кодов, равного удвоенному произведению числа состояний иринятого базового квадрата на число несходных групп базовых квадратов табличного квадранта, а не квадрату модуля СОК. Благодаря возможному параллелизму в подготовке выдачи результата оиерации и поиске узлового места базового квадрата быстродействие табличной схемы при использовании одноступенчатых онераидных дещифраторов практически повышается вдвое. Перестройка модульной таблич иой схемы с целью ее использования для всего мащинного множества лтодулей (32, 31, 29, 27, 25} затрагивает в основном перепайку выходов ДШ|.2, з начала и концов кодовых цроводов ПКЛ.

Принципы построения описанной табличной схемы применимы и для реализации экономичных больщих интегральных схем (на пороговых элементах и магнитных пленках) для

модульного остаточного умножения. 5

Формула изобретения

Табличное устройство для модульного умножения в системе остаточных классов, содержащее матрицу фиксирз ющих коды элементов, например координатных трансформаторов, и связанные с ней через вентильиые, ключевые элементы и формирователи онерандные дешифраторы и логические схемы поиска, и логические элементы, отличаюшееся тем,

5 что, с целью упрощения и повышения быстродействия, в нем выходы операндных дешифраторов строк (столбцов) базового квадрата матрицы через соответствующие группы интегральных вентильных элементов связаны со

0 входами транзисторных ключей и формирователей, а унравляемые входы вентильных элементов соединены с соответствующими выходамн логической схемы поиска базового квадрата относительно диагонали квадранта; коллекторные выходы транзисторных ключей и эмиттерные выходы формирователей соединены друг с другом через интегральные сборки и первичные обмотки координатных трансформаторов, а вторичные обмотки трансформаторов связаны с началами кодовых шин расшифровки значений узлов фазовых квадратов в дополнительно введенных иассивных трансформаторных линейках, соответственно для прямых и аддитивно ииверсных кодов резуль5 тата, концы кодовых щин через интегральные

ключевые схемы, связанные с дешифратором номеров базовых квадратов квадранта, подключены к шине нулевого потенциала, причем входы управления вторичных обмоток

трансформаторов линеек соединены с соответствующими выходами логической схемы поиска квадрантов относительно осей арифметической таблицы.

/5 20

гМ-« .cfA-lfZO

- ) Х+

2J

22Y.V.-i. --- Г.

2427

2 26

25j--- 25

Фиг. J

28

26

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство в системе остаточных классов | 1973 |

|

SU549805A1 |

| Табличный сумматор-вычислитель в системе остаточных классов | 1971 |

|

SU446056A1 |

| Побайтный преобразователь из двоичного в двоично-кодированное остаточное представление | 1972 |

|

SU437067A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ ИЗ ОСТАТОЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ПОЛИАДИЧЕСКУЮ | 1973 |

|

SU407301A1 |

| Арифметическое устройство в системе остаточных классов | 1981 |

|

SU999050A1 |

| Устройство для умножения в системе остаточных классов | 1978 |

|

SU922731A1 |

| Устройство для вычитания по модулю | 1980 |

|

SU959067A1 |

| Устройство для умножения по модулю | 1980 |

|

SU951296A1 |

| Устройство для умножения по модулю | 1980 |

|

SU959068A1 |

| Устройство для умножения чисел по модулю @ | 1983 |

|

SU1095178A1 |

Авторы

Даты

1977-03-15—Публикация

1971-05-18—Подача