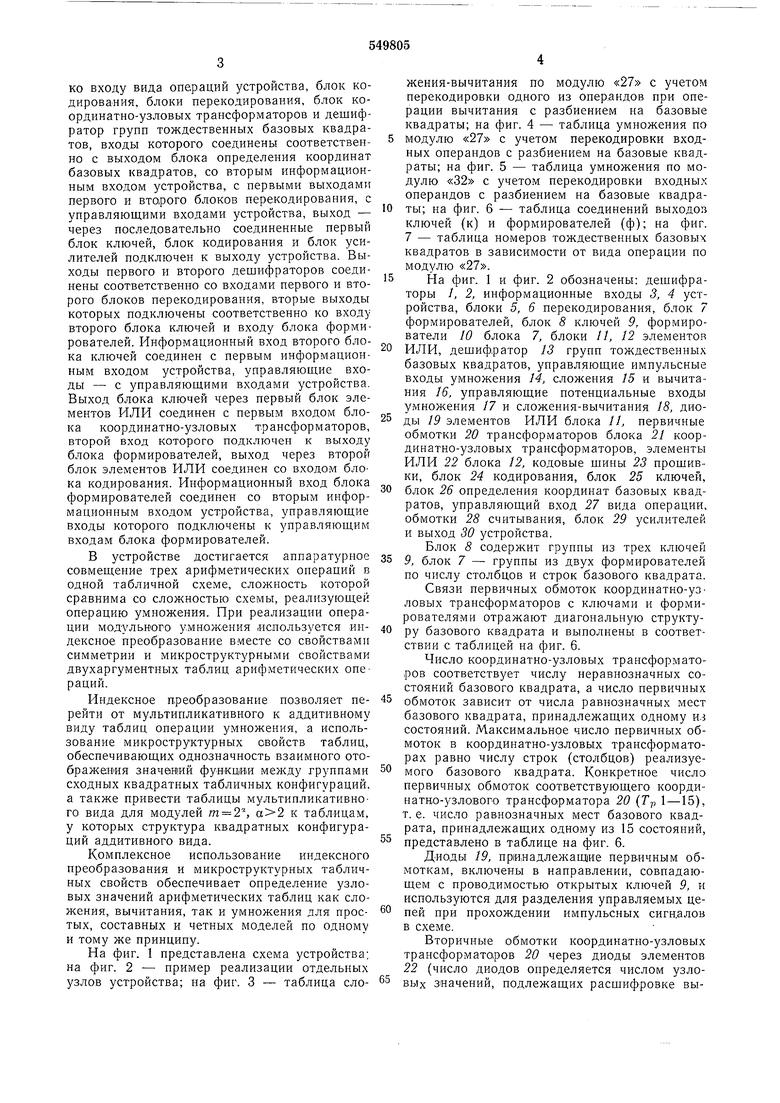

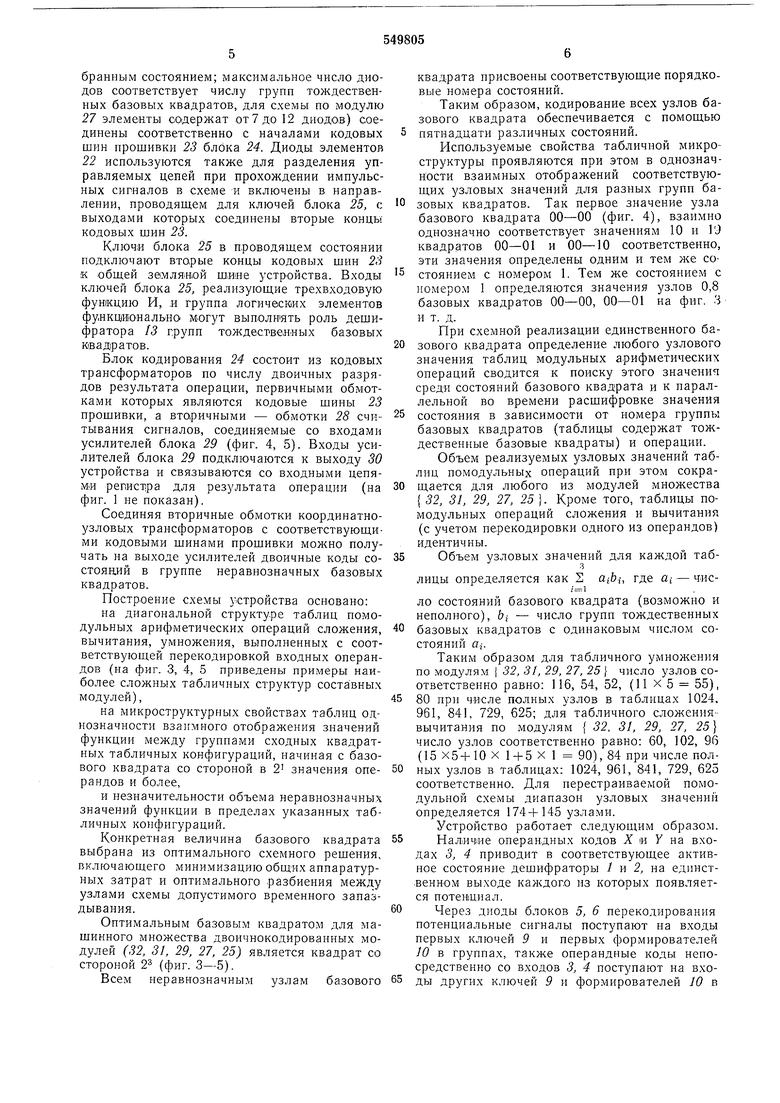

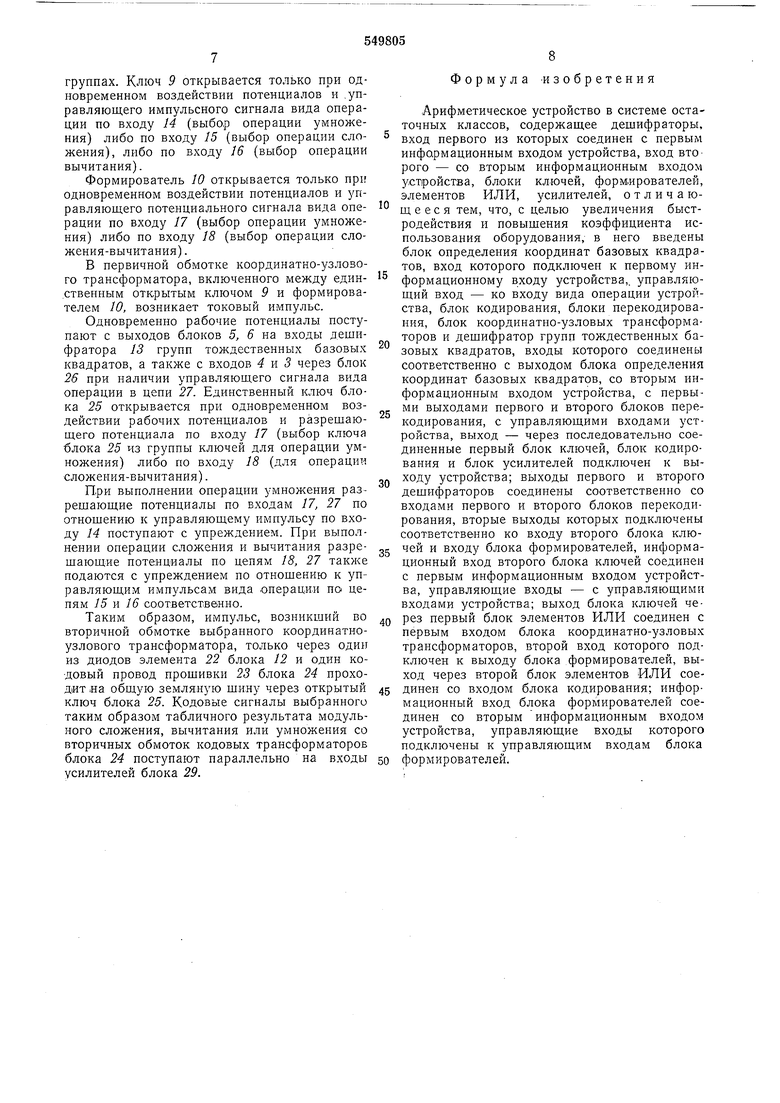

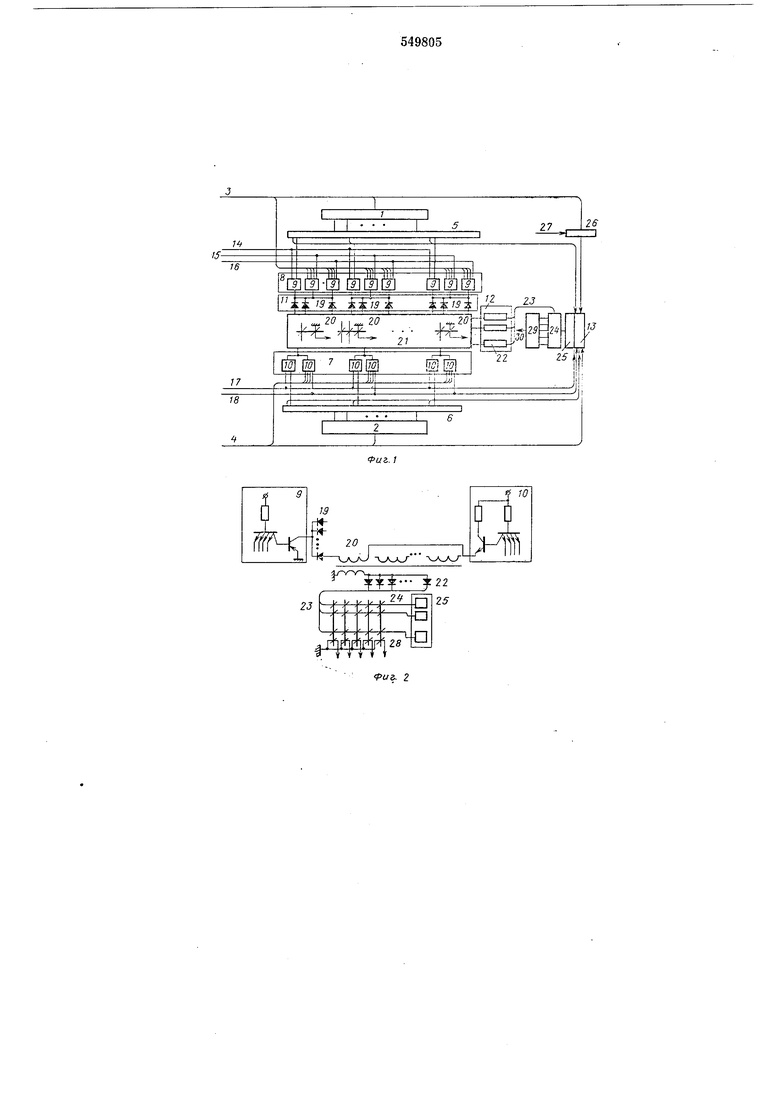

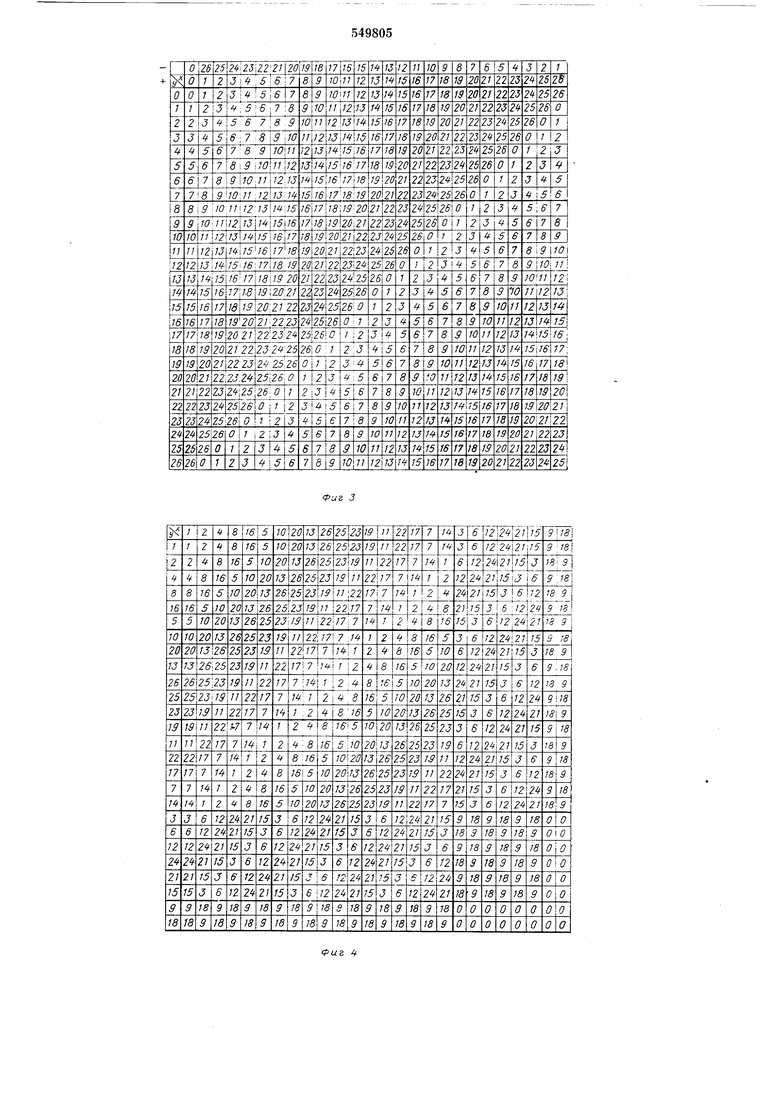

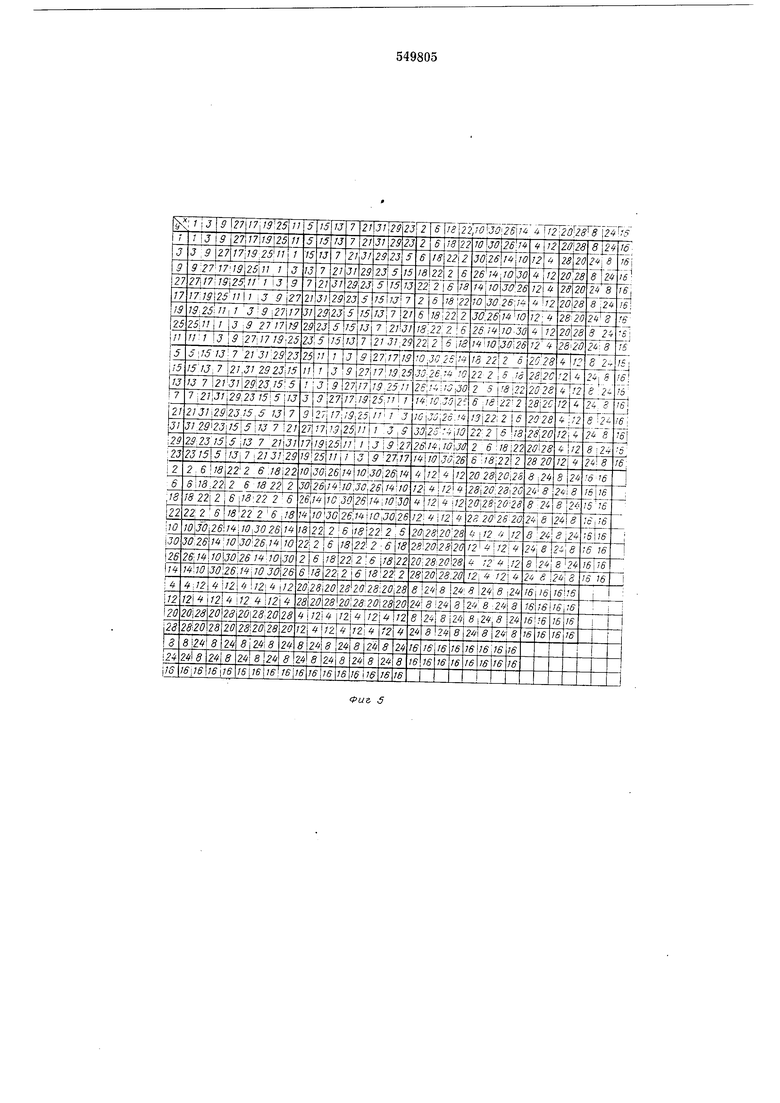

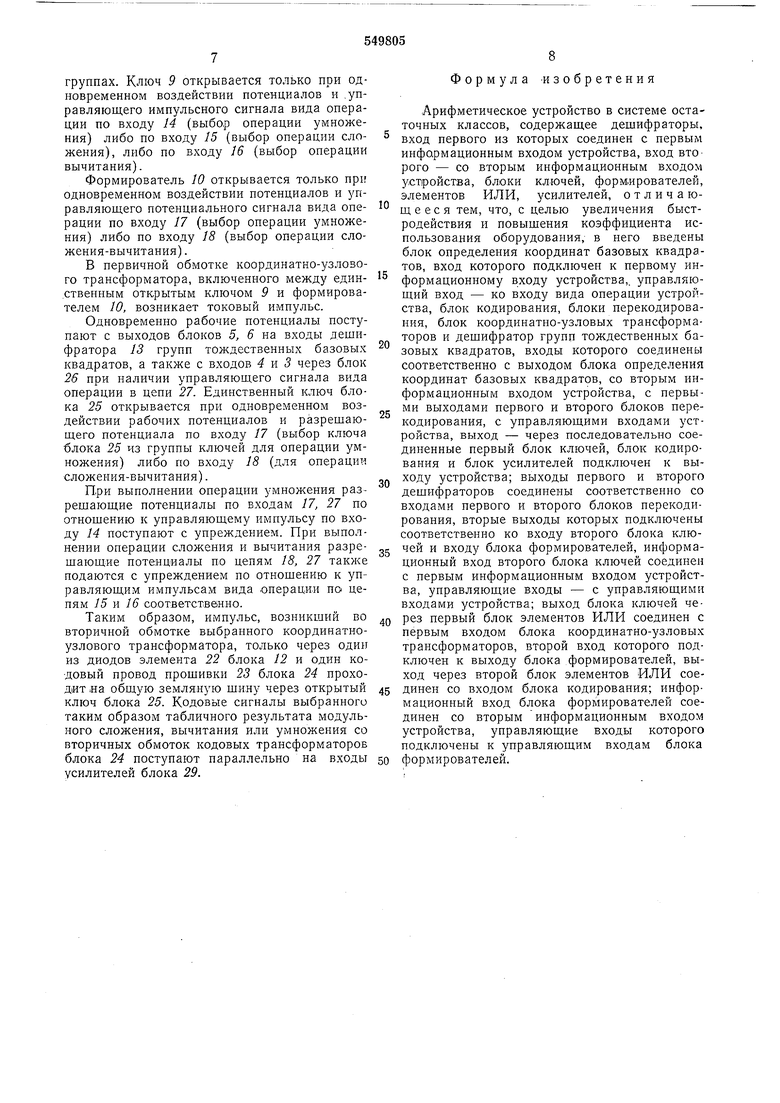

ко входу вида операций устройства, блок кодирования, блоки перекодирования, блок координатно-узловых трансформаторов и дешифратор групп тождественных базовых квадратов, входы которого соединены соответственно с выходом блока определения координат базовых квадратов, со вторым информационным входом устройства, с первыми выходами первого и вто,рого блоков перекодирования, с управляющими входами устройства, выход - через последовательно соединенные первый блок ключей, блок кодирования и блок усилителей подключен к выходу устройства. Выходы первого и второго дешифраторов соединены соответственно со входами первого и второго блоков перекодирования, вторые выходы которых подключены соответственно ко входу второго блока ключей и входу блока формирователей. Информационный вход второго блока ключей соединен с первым информационным входом устройства, управляющие входы - с управляющими входами устройства. Выход блока ключей через первый блок элементов ИЛИ соединен с первым входом блока координатно-узловых трансформаторов, второй вход которого подключен к выходу блока формирователей, выход через второй блок элементов ИЛИ соединен со входом блока кодирования. Информационный вход блока формирователей соединен со вторым информационным входом устройства, управляющие входы которого подключены к управляющим входам блока формирователей. В устройстве достигается аппаратурпое совмещение трех арифметических операций в одной табличной схеме, сложность которой сравнима со сложностью схемы, реализующей операцию умножения. При реализации операции модульного умнож.ения используется индексное преобразование вместе со свойствами симметрии и микроструктурными свойствами двухаргументных таблиц арифметических операций. Индексное преобразование позволяет перейти от мультипликативного к аддитивному виду таблиц операции умножения, а использование микроструктурных свойств таблиц, обеспечивающих однозначность взаимного отображен1ия зпачений функции между группами сходных квадратных табличных конфигураций, а также привести таблицы мультипликативного вида для модулей т - 2, к таблицам, у которых структура квадратных конфигураций аддитивного вида. Комплексное использование индексного преобразования и микроструктурных табличных свойств обеспечивает определение узловых значений арифметических таблиц как сложения, вычитания, так и умножения для простых, составных и четных моделей по одному и тому же принципу. На фиг. 1 представлена схема устройства; на фиг. 2 - пример реализации отдельных узлов устройства; па фиг. 3 - таблица еложения-вычитания по модулю «27 с учетом перекодировки одного из операндов при операции вычитания с разбиением на базовые квадраты; на фиг. 4 - таблица умножения по модулю «27 с учетом перекодировки входных операндов с разбиением на базовые квадраты; на фиг. 5 - таблица умножения по модулю «32 с учетом перекодировки входных операндов с разбиением на базовые квадраты; на фиг. 6 - таблица соединений выходо: ключей (к) и формирователей (ф); на фиг. 7 - таблица номеров тождественных базовых квадратов в зависимости от вида операции по модулю «27. На фиг. 1 и фиг. 2 обозначены: дешифраторы 1, 2, информационные входы 3, 4 устройства, блоки 5, 6 перекодирования, блок 7 формирователей, блок 8 ключей 9, формирователи 10 блока 7, блоки //, 12 элементов ИЛИ, дешифратор 13 групп тождественных базовых квадратов, управляющие импульсные входы умножения 14, сложения 15 и вычитания 16, управляющие потенциальные входы умножения 17 и сложения-вычитания 18, диоды 19 элементов ИЛИ блока 11, первичные обмотки 20 трансформаторов блока 21 координатно-узловых трансформаторов, элементы ИЛИ 22 блока 12, кодовые шины 23 прошивки, блок 24 кодирования, блок 25 ключей, блок 26 определения координат базовых квадратов, управляющий вход 27 вида операции, обмотки 28 считывания, блок 29 усилителей и выход 30 устройства. Блок 8 содержит группы из трех ключей 9, блок 7 - группы из двух формирователей по числу столбцов и строк базового квадрата. Связи первичных обмоток координатно-узловых трансформаторов с ключами и формирователями отражают диагональную структуру базового квадрата и выполнены в соответствии с таблицей на фиг. б. Число координатно-узловых трансформаторов соответствует числу неравнозначных состояний базового квадрата, а число первичных обмоток зависит от числа равнозначных мест базового квадрата, принадлежащих одному из состояний. Максимальное число первичных обмоток в коордипатно-узловых трансформаторах равно числу строк (столбцов) реализуемого базового квадрата. Конкретное число первичных обмоток соответствующего координатно-узлового трансформатора 20 (Тр 1-15), т. е. число равнозначных мест базового квадрата, принадлежащих одному из 15 состояний, представлено в таблице на фиг. 6. Диоды 19, принадлежащие первичным обмоткам, включены в направлении, совпадающем с проводимостью открытых ключей 9, и используются для разделения управляемых цепей при прохождении импульсных сигналов в схеме. Вторичные обмотки координатно-узловых трансформато,ров 20 через диоды элементов 22 (число диодов определяется числом узловых значений, подлежащих расшифровке выбранным состоянием; максимальное число диодов соответствует числу групн тождественных базовых квадратов, для схемы по модулю 27 элементы содержат от 7 до 12 диодов) соединены соответственно с началами кодовых шин ирошивки 23 блбка 24. Диоды элементов 22 используются также для разделения управляемых цепей при прохождении импульсных сигналов в схеме и включены в направлении, проводящем для ключей блока 25, с выходами которых соединены вторые концы кодовых шин 23.

Ключи блока 25 в проводящем состоянии подключают вторые концы кодовых шин 23 к общей замля-ной шине устройства. Входы ключей блока 25, реализующие трехвходовую функцию И, .и группа логичесиих элементов фу,нкп И10наль«о могут выполнять роль дешифратора /5 групп тождественных базовых квадратов.

Блок кодирования 24 состоит из кодовых трансформаторов по числу двоичных разрядов результата операции, первичными обмотками которых являются кодовые шины 23 прошивки, а вторичными - обмотки 28 считывания сигналов, соединяемые со входами усилителей блока 29 (фиг. 4, 5). Входы усилителей блока 29 подключаются к выходу 30 устройства и связываются со входными цепями регистра для результата операции (на фиг. 1 не показан).

Соединяя вторичные обмотки координатноузловых трансформаторов с соответствующими кодовыми щинами прощивки можно получать на выходе усилителей двоичные коды состояний в группе неравнозначных базовых квадратов.

Построение схемы устройства основано:

на диагональной структуре таблиц помодульных арифметических операций сложения, вычитания, умножения, выполненных с соответствующей перекодировкой входных операндов (на фиг. 3, 4, 5 приведены примеры наиболее сложных табличных структур составных модулей),

на микроструктурных свойствах таблиц однозначности взаимного отображения значений функции между группами сходных квадратных табличных конфигураций, начиная с базового квадрата со стороной в 2 значения oneрандов и более,

и незначительности объема неравнозначных значений функции в пределах указанных табличных конфигураций.

Конкретная величина базового квадрата выбрана из оптимального схемного рещения, включающего минимизацию общих аппаратурных затрат и оптимального .разбиения между узлами схемы допустимого временного запаздывания.

Оптимальным базовым квадратом для мащинного множества двоичнокодированных модулей (32, 31, 29, 27, 25) является квадрат со стороной 2 (фиг. 3-5).

Всем неравнозначным узлам базового

квадрата присвоены соответствующие порядковые номера состояний.

Таким образом, кодирование всех узлов базового квадрата обеспечивается с помощью пятнадцати различных состояний.

Используемые свойства табличной микроструктуры проявляются при этом в однозначности взаимных отображений соответствующих узловых значений для разных групп базовых квадратов. Так первое значение узла базового квадрата 00-00 (фиг. 4), взаимно однозначно соответствует значениям 10 и 19 квадратов 00-01 и 00-10 соответственно, эти значения определены одним и тем же состоянием с номером 1. Тем же состоянием с номером 1 определяются значения узлов 0,8 базовых квадратов 00-00, 00-01 на фиг. 3 и т. д.

При схемной реализации единственного базового квадрата определение любого узлового значения таблиц модульных арифметических операций сводится к поиску этого значения среди состояний базового квадрата и к параллельной во времени расщифровке значения состояния в зависимости от номера группы базовых квадратов (таблицы содержат тождественные базовые квадраты) и операции.

Объем реализуемых узловых значений таблиц помодульных операций при этом сокращается для любого из модулей множества { 32, 31, 29, 27, 25 }. Кроме того, таблицы помодульных операций сложения и вычитания (с учетом перекодировки одного из операндов) идентичны.

Объем узловых значений для каждой таблицы определяется как 2 «;&,-, где а; - чис/ 1

ло состояний базового квадрата (возможно и неполного), bi - число групп тождественных базовых квадратов с одинаковым числом состояний (7,.

Таким образом для табличного умножения по модулям j 32, 31, 29, 27, 25 } число узлов соответственно равно: 116, 54, 52, (11x5 55), 80 при числе полных узлов в таблицах 1024. 961, 841, 729, 625; для табличного сложениявычитания по модулям { 32, 31, 29, 27, 25} число узлов соответственно равно: 60, 102, 96 (15 x5-t-10 X 1-f 5 X 1 90), 84 при числе полных узлов в таблицах: 1024, 961, 841, 729, 625 соответственно. Для перестраиваемой помодульной схемы диапазон узловых значений определяется 174-ь145 узлами.

Устройство работает следующим образом.

Наличие операндных кодов X т У на входах 3, 4 приводит в соответствующее активное состояние дешифраторы / и 2, на единственном выходе каждого из которых появляется потен1ииал.

Через диоды блоков 5, 6 перекодирования потенциальные сигналы поступают на входы первых ключей 9 и первых формирователей 10 в группах, также операндные коды непосредственно со входов 3, 4 поступают на входы других ключей 9 и формирователей 10 в группах. Ключ 9 открывается только при одновременном воздействии потенциалов и .управляющего импульсного сигнала вида операции по входу 14 (выбор операции умножения) либо по входу 15 (выбор операции еложения), либо по входу 16 (выбор операции вычитания). Формирователь 10 открывается только при одновременном воздействии потенциалов и управляющего потенциального сигнала вида oneрации по входу 17 (выбор операции умножения) либо по входу 18 (выбор операции сложения-вычитания). В первичной обмотке координатно-узлового трансформатора, включенного между единственпым открытым ключом 9 и формирователем 10, возникает токовый импульс. Одновременно рабочие потенциалы поступают с выходов блоков 5, 6 иа входы дешифратора 13 групп тождественных базовых квадратов, а также с входов 4 и 5 через блок 26 при наличии управляющего сигнала вида операции в цепи 27. Единственный ключ блока 25 открывается при одновременном воздействии рабочих потенциалов и разрешающего потенциала по входу 17 (выбор ключа блока 25 из группы ключей для операции умножения) либо по входу 18 (для операции сложения-вычитания). При выполнении операции умножения разрешающие потенциалы по входам 17, 27 по отношению к управляющему импульсу по входу 14 поступают с упреждением. При выполнении операции сложения и вычитания разрешающие потенциалы по цепям 18, 27 также подаются с упреждением по отношению к управляющим импульсам вида операции по цепям 15 и 16 соответственно. Таким образом, импульс, возникший во вторичной обмотке выбранного координатноузлового трансформатора, только через один из диодов элемента 22 блока 12 и один кодовый провод прошивки 23 блока 24 проходит на общую землялую шину через открытый ключ блока 25. Кодовые сигналы выбранного таким образом табличного результата модульного сложения, вычитания или умножения со вторичных обмоток кодовых трансформаторов блока 24 поступают параллельно на в.ходы усилителей блока 29. Формула -изобретения Арифметическое устройство в системе остаточных классов, содержащее дешифраторы, вход первого из которых соединен с первым информационным входом устройства, вход второго - со вторым информационным входом устройства, блоки ключей, формирователей, элементов ИЛИ, усилителей, отличающееся тем, что, с целью увеличения быстродействия и повышения коэффициента использования оборудования, в него введены блок определения координат базовых квадратов, вход которого подключен к первому информационному входу устройства,, управляющий вход - ко входу вида операции устройства, блок кодирования, блоки перекодирования, блок координатно-узловых трансформаторов и дешифратор групп тождественных базовых квадратов, входы которого соединены соответственно с выходом блока определения координат базовых квадратов, со вторым информационным входом устройства, с первыми выходами первого и второго блоков перекодирования, с управляющими входами устройства, выход - через последовательно соединенные первый блок ключей, блок кодирования и блок усилителей подключен к выходу устройства; выходы первого и второго дешифраторов соединены соответственно со входами первого и второго блоков перекодирования, вторые выходы которых подключены соответственно ко входу второго блока ключей и входу блока формирователей, информационный вход второго блока ключей соединен с первым информационным входом устройства, управляющие входы - с управляющими входами устройства; выход блока ключей через первый блок элементов ИЛИ соединен с первым входом блока координатно-узловых трансформаторов, второй вход которого подключен к выходу блока формирователей, выход через второй блок элементов ИЛИ соединен со входом блока кодирования; информационный вход блока формирователей соединен со вторым информационным входом устройства, управляющие входы которого подключены к управляющим входам блока формирователей.

,- В..

/J

25Н24

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ ИЗ ОСТАТОЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ПОЛИАДИЧЕСКУЮ | 1973 |

|

SU407301A1 |

| Арифметическое устройство в системе остаточных классов | 1981 |

|

SU999050A1 |

| Табличный сумматор-вычислитель в системе остаточных классов | 1971 |

|

SU446056A1 |

| Табличное устройство для модульного умножения в системе остаточных классов | 1971 |

|

SU550636A1 |

| Побайтный преобразователь из двоичного в двоично-кодированное остаточное представление | 1972 |

|

SU437067A1 |

| Устройство для вычитания по модулю | 1980 |

|

SU959067A1 |

| СПОСОБ КОМПРЕССИИ-ДЕКОМПРЕССИИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2488960C2 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для умножения в системе остаточных классов | 1978 |

|

SU922731A1 |

ArVNX

2J

25

7 -

0

л- 1-5-12

7 - « Ш.-2-6-Ю

N-3-8-13- 15-16-17

-S:- -9-1 -18-20-21-227-10-J3

-t

/5

Авторы

Даты

1977-03-05—Публикация

1973-03-26—Подача