1

Изобретение относится к области вычислительной техники и может найти применение для построения устройства связи между объектами различного назначения.

Известно устройство связи в вычислительной системе, содерн ащее дискрипторные регистры связей, с которыми может работать ЭВМ.

Однако, это устройство не позволяет сократить объем оборудования устройства связи и повысить его надежность 1.

Из известных устройств наиболее близким по технической супдности является устройство связи, содержащее блок передачи, первый и второй элементы «И, первый и второй элементы «НЕ, регистр сдвига, шифратор, первый вход устройства соединен с первым входом первого элемента «И, второй вход устройства соединен с первым входом второго элемента «Pi, третий вход устройства соединен со входом шифратора, четвертый вход- с первым входом регистра сдвига и со входом первого элемента «НЕ, выход которого соединен со вторым входом второго элемента «И, выход которого соединен со вторым входом регистра сдвига и через второй элемент «НЕ с третьим входом регистра сдвига, выход первого элемента «И соединен с четвертым входом регистра сдвига, первый выход которого соединен с его пятым входом, группа выходов регистра сдвига соединена с соответствующими входами шифратора, выход которого соединен с первым входом блока передачи, группа входов блока передачи является входами устройства, группа выходов- выходами устройства 2.

Недостаток - невозможность выполнить его в виде интегральной схемы. Цель - упрощение устройства.

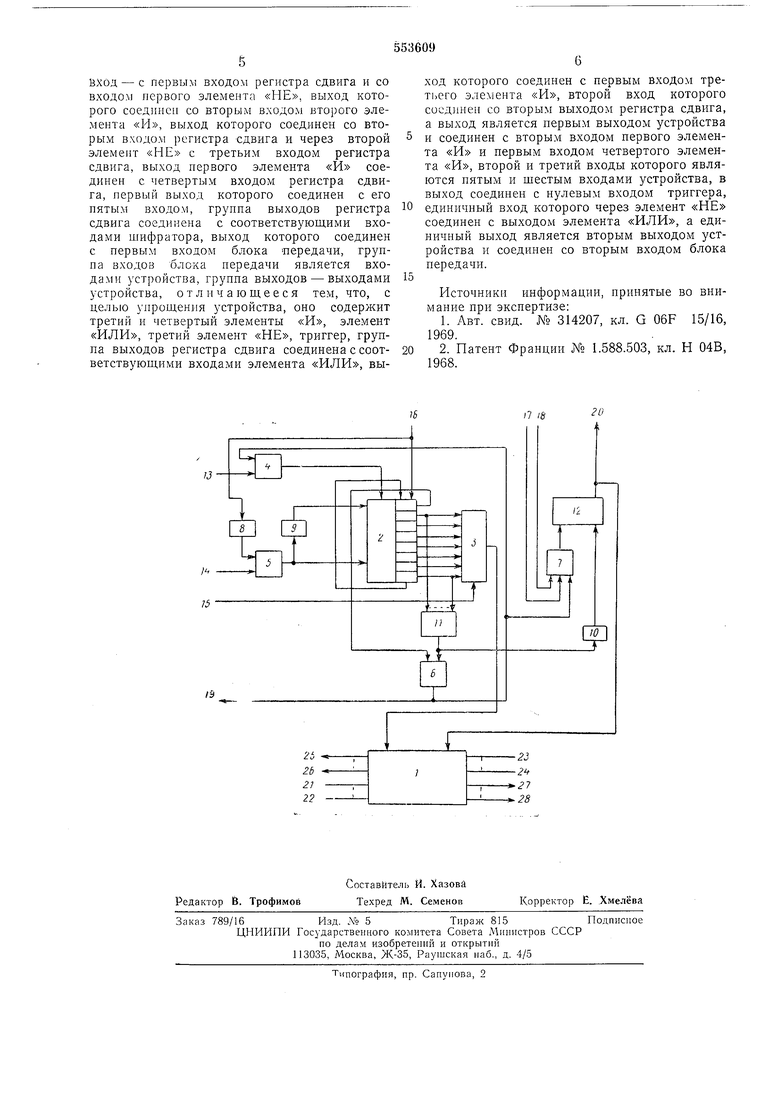

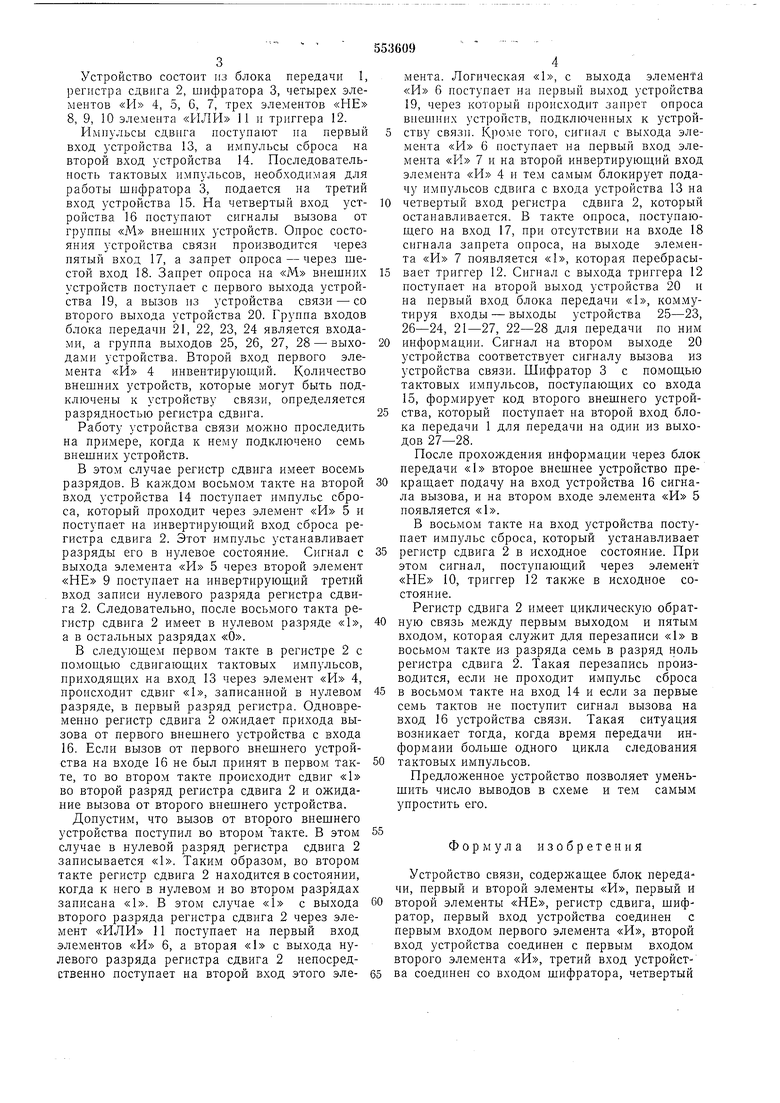

Поставленная цель достигается тем, что устройство содержит третий и четвертый элементы «И, элемент «ИЛИ, третий элемент «НЕ, триггер, группа выходов регистра сдвига соединена с ответствующими входами элемента «ИЛИ, выход которого соединен с первым входом третьего элемента «И, второй вход которого соединен со вторым выходом регистра сдвига, а выход является первым выходом устройства и соединен со вторым входом первого элемента «И и первым входом четвертого элемента «И, второй и третий входы которого являются пятым и шестым входами устройства, а выход соединен с нулевым входом триггера, единичный вход которого через элемент «НЕ соединен с выходом элемента «ИЛИ, а единичный выход является вторым выходом устройства и соединен со вторым входом блока передачи. На чертелсе изображена функциональная

схема устройства связи.

Устройство состоит из блока передачи 1, регистра сдвига 2, шифратора 3, четырех элементов «И 4, 5, 6, 7, трех элементов «НЕ 8, 9, 10 элемента «ИЛИ 11 и триггера 12.

Импульсы сдвига иостуиают иа первый вход устройства 13, а импульсы сброса на второй вход устройства 14. Последовательиость тактовых импульсов, необходимая для работы шифратора 3, подается на третий вход устройства 15. На четвертый вход устройства 16 поступают сигналы вызова от группы «М внешних устройств. Опрос состояния устройства связи производится через иятый вход 17, а запрет опроса - через шестой вход 18. Запрет опроса на «М внешних устройств поступает с первого выхода устройства 19, а вызов из устройства связи - со второго выхода устройства 20. Груипа входов блока передачи 21, 22, 23, 24 является входами, а группа выходов 25, 26, 27, 28 - выходами устройства. Второй вход первого элемента «И 4 инвентируюи.;ий. Количество внешних устройств, которые могут быть подключены к устройству связи, определяется разрядностью регистра сдвига.

Работу устройства связи можно проследить на примере, когда к нему подключено семь внешних устройств.

В этом случае регистр сдвига имеет восемь разрядов. В каждом восьмом такте на второй вход устройства 14 поступает импульс сброса, который проходит через элемент «И 5 и поступает на инвертируюший вход сброса регистра сдвига 2. Этот импульс устанавливает разряды его в нулевое состояние. Сигнал с выхода элемента «И 5 через второй элемент «НЕ 9 поступает на инвертирующий третий вход записи нулевого разряда регистра сдвига 2. Следовательно, после восьмого такта регистр сдвига 2 имеет в нулевом разряде «1, а в остальных разрядах «О.

В следуюш;ем первом такте в регистре 2 с иомошью сдвигаюш,их тактовых импульсов, приходяших на вход 13 через элемент «И 4, происходит сдвиг «1, записанной в нулевом разряде, в первый разряд регистра. Одновременно регистр сдвига 2 ожидает прихода вызова от первого внешнего устройства с входа 16. Если вызов от первого внешнего устройства на входе 16 не был принят в первом такте, то во втором такте происходит сдвиг «1 во второй разряд регистра сдвига 2 и ожидание вызова от второго внешнего устройства.

Допустим, что вызов от второго внешнего устройства поступил во втором такте. В этом случае в нулевой разряд регистра сдвига 2 записывается «1. Таким образом, во втором такте регистр сдвига 2 находится в состоянии, когда к него в нулевом и во втором разрядах записана «1. В этом случае «1 с выхода второго разряда регистра сдвига 2 через элемент «ИЛИ 11 поступает на первый вход элементов «И 6, а вторая «1 с выхода нулевого разряда регистра сдвига 2 непосредственно поступает на второй вход этого элемента. Логическая «1, с выхода элемента «И 6 поступает на первый выход устройства 19, через который происходит запрет опроса впешиих устройств, подключенных к устрой5 ству связи. того, сигнал с выхода элемента «И 6 поступает на первый вход элемента «И 7 и на второй инвертируюш,ий вход элемента «И 4 и тем самым блокирует подачу имиульсов сдвига с входа устройства 13 на 10 четвертый вход регистра сдвига 2, который останавливается. В такте опроса, поступаюш,его на вход 17, при отсутствии на входе 18 сигнала запрета опроса, на выходе элемента «И 7 появляется «1, которая перебрасы15 вает триггер 12. Сигиал с выхода триггера 12 поступает на второй выход устройства 20 и иа первый вход блока передачи «1, коммутируя входы - выходы устройства 25-23, 26-24, 21-27, 22-28 для иередачи по ним 0 информации. Сигнал на втором выходе 20 устройства соответствует сигналу вызова из устройства связи. Шифратор 3 с помощью тактовых импульсов, поступающих со входа 15, фор.мирует код второго внешнего устрой5 ства, который поступает на второй вход блока передачи 1 для передачи на одии из выходов 27-28.

После прохождения информации через блок передачи «1 второе внешнее устройство пре0 кращает подачу на вход устройства 16 сигнала вызова, и на втором входе элемента «И 5 появляется «1.

В восьмом такте иа вход устройства поступает импульс сброса, который устанавливает 5 регистр сдвига 2 в исходное состояние. При этом сигнал, поступающий через элемент «НЕ 10, триггер 12 также в исходное состояние.

Регистр сдвига 2 имеет циклическую обрат0 ную связь между первым выходом и пятым входом, которая служит для перезаписи «1 в восьмом такте из разряда семь в разряд ноль регистра сдвига 2. Такая перезапись производится, если не проходит импульс сброса 5 в восьмо.м такте на вход 14 и если за первые семь тактов не иоступит сигнал вызова на вход 16 устройства связи. Такая ситуация возникает тогда, когда время передачи информаии больше одного цикла следования тактовых импульсов.

Предложенное устройство позволяет уменьшить число выводов в схеме и тем самым упростить его.

Формула изобретения

Устройство связи, содержащее блок передачи, первый и второй элементы «И, первый и

второй элементы «НЕ, регистр сдвига, шифратор, первый вход устройства соединен с первым входом первого элемента «И, второй вход устройства соединен с первым входом второго элемента «И, третий вход устройства соедииен со входом шифратора, четвертый

s

вход - с первым входом регистра сдвига и со входом первого элемента «НЕ, выход которого соединен со вторы1м входом второго элемента «И, выход которого соединен со вторым входом регистра сдвига и через второй элеме1гг «НЕ с третьим входом регистра сдвига, выход первого элемента «И соединен с четвертым входом регистра сдвига, первый выход которого соединен с его пятым входом, группа выходов регистра сдвига соединена с соответствующими входами шифратора, выход которого соединен с первым входом блока передачи, группа входов блока передачи является входами устройства, группа выходов- выходами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит третий и четвертый элементы «И, элемент «ИЛИ, третий элемент «НЕ, триггер, группа выходов регистра сдвига соединена с соответствующими входами элемента «ИЛИ, вы6

ход которого соединен с первым входом третьего элемента «И, второй вход которого соединен со вторым выходом регистра сдвига, а выход является первым выходом устройства и соединен с вторым входом первого элемента «И и первым входом четвертого элемента «И, второй и третий входы которого являются пятым и шестым входами устройства, в выход соединен с нулевым входом триггера, единичный вход которого через элемент «НЕ соединен с выходом элемента «ИЛИ, а единичный выход является вторым выходом устройства и соединен со вторым входом блока передачи.

Источники информации, принятые во внимание при экспертизе:

1.Авт. свид. № 314207, кл. G 06F 15/16, 1969.

2.Натент Франции № 1.588.503, кл. Н 04В, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения абонентов с каналом передачи данных | 1987 |

|

SU1444791A1 |

| Устройство для отображения состояния контролируемых объектов | 1990 |

|

SU1800646A1 |

| Устройство для сопряжения процессоров с внешними абонентами | 1978 |

|

SU750472A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

| Диспетчерский полукомплект телемеханического устройства | 1975 |

|

SU556479A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Многоканальный измеритель интенсивности импульсов | 1991 |

|

SU1807423A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1363224A1 |

IS

22 /7

Авторы

Даты

1977-04-05—Публикация

1973-11-30—Подача