Изобретение относится к информационно-измерительной технике и может быть использовано при регистрации случайных импульсных потоков, поступающих до детекторов ионизирующих излучений.

Целью изобретения является увеличение быстродействия при обработке группы датчиков,

Цель достигается тем, что в измеритель интенсивно сти импульсов, содержащий блок управления, первый дешифратор, делитель частоты, четыре элемента И, блок датчиков, генератор, мультиплексор и регистрирующее устройство, введены второй мультиплексор, три счетчика, четыре тригге- ра, второй, третий, четвертый и пятый дешифраторы, пятый и шестой элементы И, два элемента ИЛИ, два элемента задержки, два регистра, шифратор, блок управления номером канала, причем выход блока датчиков через первый мультиплексор подключен к первому входу схемы И, выход которого подключен к первому входу первого счетчика, первый выход которого соединен через дешифратор с первым входом второго триггера, а второй выход через второй дешифратор соединен с первым входом третьего триггера, причем выходы второго и третьего триггеров подключены к входу шифратора, первый и второй выходы кото- рого через элемент И подключены соответственно к вычитающему и суммирующему входам второго счетчика импульсов и через схему ИЛИ к первому входу четвертого элемента И, выход которого соединен с первым входом четвертого триггера и первым входом второго элемента ИЛИ, выход которого подключен к первому входу первого триггера, к вторым входам первого счетчика и второго и третьего триггеров, а через пер- вый элемент задержки к второму входу четвертого триггера, выход которого соединен с первым входом шестого элемента И, второй вход которого подключен к первому входу третьего счетчика и через второй элемент задержки к выходу пятого дешифратора, вторым входом второго, третьего и четвертого элементов И и к второму входу первого триггера, выход которого соединен с вторым входом первой схемы И и первым вхо- дом пятой схемы И, второй вход которой подключен к первому генератору, а выход через первый делитель - к первому входу второго мультиплексора, выход которого через второй вход третьего счетчика соединен с входом пятого дешифратора, а второй вход второго мультиплексора - с выходом второго счетчика и первым входом блока управления номером канала и регистрирующим устройством, второй вход которого соединен с третьим выходом первого счетчика, а третий вход подключен к первому выходу блока управления, второй выход которого соединен с вторым входом второго элемента ИЛИ, третий выход - с вторым входом блока управления номером канала, четвертый выход-с первым входом первого регистра, выход которого подключен к управляющему входу первого мультиплексора, а второй вход - к выходу второго регистра, второй вход которого соединен с соответствующим выходом блока управления номером канала, причем выход шестого элемента И соединен с входом блока управления, а второй и третий выходы второго счетчика через соответствующий третий и четвертый дешифратор подключены к третьему входу второй и третьей схемы.

Анализ заявленного технического решения показывает, что в сравнении с аналогом и прототипом оно содержит мультиплексор, три счетчика, четыре триггера, два элемента И, два элемента ИЛИ, два элемента задержки, два регистра, шифратор, блок управления номером канала, которые отсутствуют у аналога и пр ототипа, причем выполняемые этими блоками функции обеспечивают существенное увеличение быстродействия обработки группы датчиков. Таким образом, за счет наличия вышеперечисленных блоков и принадлежащих им связей заявленное техническое решение соответствует критерию новизна по сравнению с прототипом и обладает существенными отличиями по сравнению с аналогами.

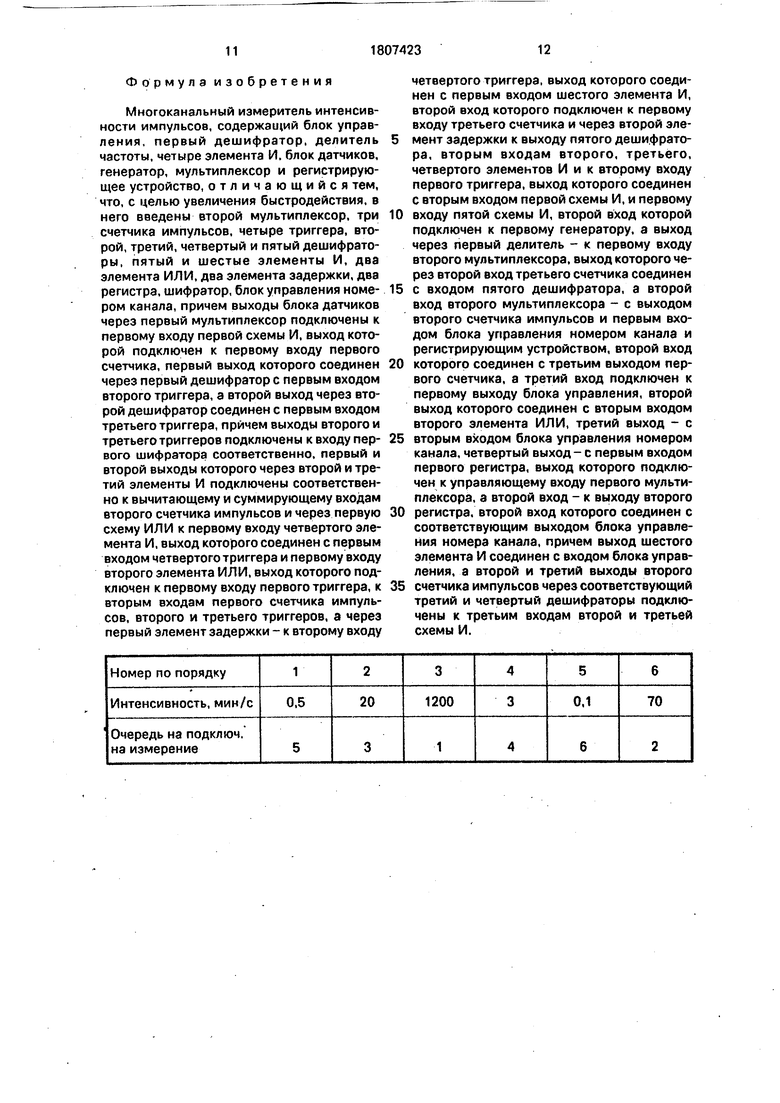

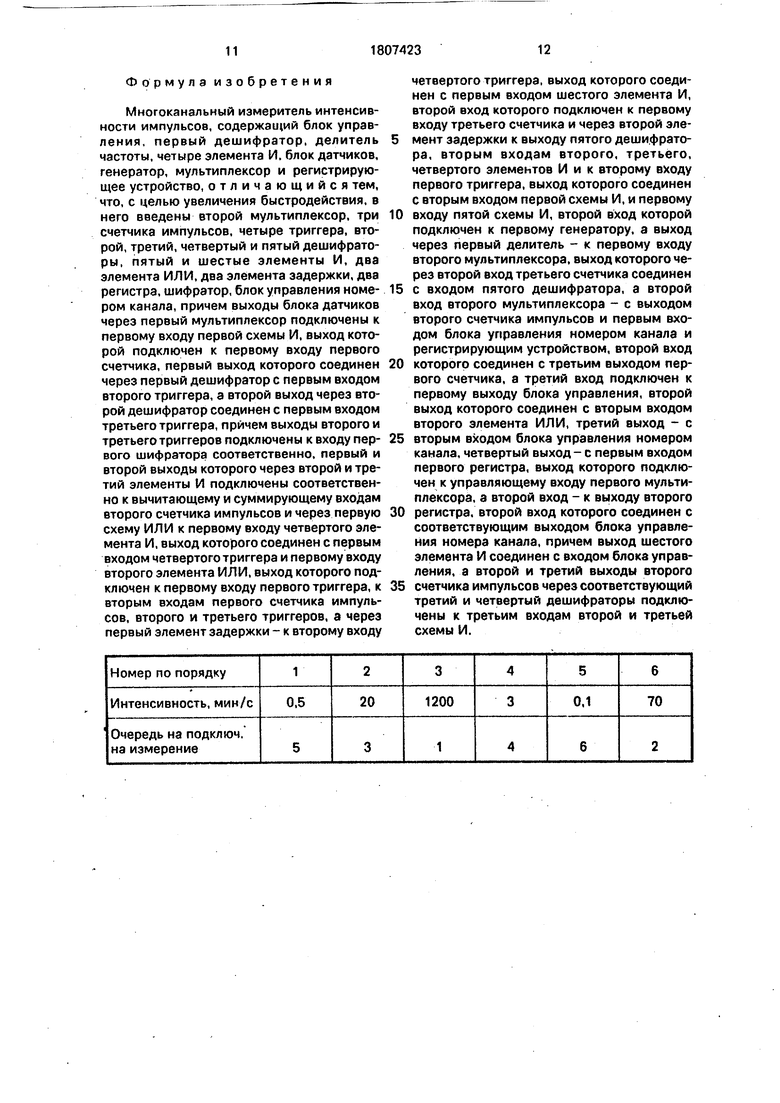

Суть изобретения состоит в том, что порядок подключения для измерения каналов осуществляется не по жесткому алгоритму (например, в порядке возрастания номера канала), а в очередности, обеспечивающей плавное (монотонное) убывание (возрастание) интенсивности от канала к каналу, т.е. канал с большей интенсивностью обрабатывается раньше канала с меньшей интенсивностью. При этом его порядковый номер может быть больше. Пример приведен в таблице.

На фиг.1 представлена функциональная схема устройства многоканального преобразования массивов аналоговой информации; на фиг.2 - структурная схема блока управления номером канала; на фиг.З -функциональная схема анализатора чисел; на фиг.4 - пример реализации блока управления.

На фиг.1 представлена функциональная схема многоканального измерителя интенсивности поступления импульсов с широким динамическим диапазоном. Входы блока 1 датчиков через мультиплексор 2

подключены к первому входу схемы И 3, выход которой подключен к первому входу счетчика 4. Первый выход счетчика 4 соединен через дешифратор 5 с первым входом триггера (Т) 6, а второй выход - через дешифратор 7 с первым входом Т 8. Выходы Т 6 и 8 подключены к шифратору 9. Первый и второй выходы шифратора 9 через элементы И 10 и 11 подключены соответственно к вычитающему и суммирующему входам счетчика 12 и через схему ИЛИ 13 к первому входу элемента И 14. Выход элемента И 14 соединен с первым входом Т 15 и первым входом элемента ИЛИ 16, выход которого подключен к первому входу Т 17, к вторым входам счетчика 4 и Т б и 8, через элемент 18 задержки к второму входу Т 15. Выход Т 15 соединен с первым входом элемента И 19, второй вход которого подключен к первому входу счетчика 20 и через элемент 21 задержки к выходу дешифратора 22, вторым входом элементов И 10, 11 и 14 и к второму входу Т 17. Выход Т 17 соединен с вторым входом схемы И 3 и первым входом схемы И 23, второй вход которой подключен к генератору 24, а выход через делитель 25 - к первому входу мультиплексора 26. Выход мультиплексора 26 через второй вход счетчика 20 соединен с входом дешифратора 22, а второй вход - с выходом счетчика 12 и первым входом 27 регистрирующего устройства 28, второй вход которого соединён с третьим выходом счетчика 4, а третий вход подключен к первому выходу блока 27 управления номером канала. Первый выход блока 29 управления соединен первым входом регистрирующего устройства 28, второй выход - с вторым входом элемента ИЛИ 16, третий выход - с вторым входом блока 27 управления номером канала, четвертый выход-с первым входом регистра 30, выход которого подключен к управляющему входу мультиплексора 2, а второй вход - к выходу регистра31. Два входа регистра31 соединены с соответствующими выходами блока 27. Выход элемента И 19 соединен с входом блока 29 управления. Второй и третий выходы счетчика 12 через соответствующие дешифраторы 32 и 33 подключены к третьим входам схем И 10 и 11.

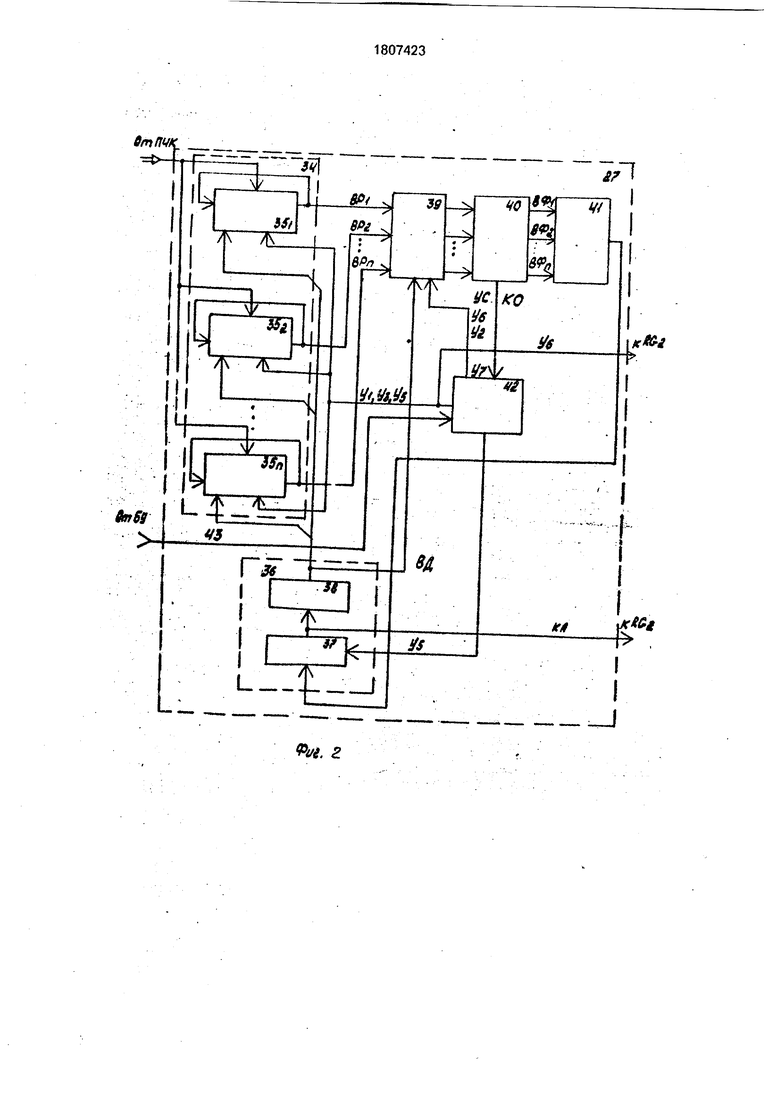

На фиг.2 представлена структурная схема блока 27 управления номером канала. Упорядочение цифровых кодов, формируемых на выходах, выполняется параллельно по словам и последовательно по разрядам, но сами цифровые коды не выделяются, а выделяются коды их адресов в порядке убывания.

Блок 27 содержит блок 34 памяти, выполненный на базе параллельно-последовательных регистров . В блоке 34 памяти осуществляется параллельный по рэзрядэм рием цифрового кода в регистр 35 I (I 1,п) и одновременный последова- 5 тельный вывод цифровых кодов из регистров 35i-35n. Для адресации регистра 35 используется адресный блок 36. Он содержит счетчика 37 и дешифратор 38. Кроме того, адресный блок 36 выполняет выбор Т

10 в анализаторе 39 чисел для установки его в нулевое состояние. ,

Анализатор 39 чисел предназначен для определения максимального цифрового кода путем анализа битовых срезов содержи5 мого блока 34 памяти. В том случае, если в анализаторе чисел установлено наличие нескольких максимальных цифровых кодов (равных между собой), определение первых максимальных цифровых кодов (равных

0 между собой), определение первого максимального цифрового кода выполняет приоритетный формирователь 40. Выходы формирователя 40 (ВФ1-ВФП) подключены к шифратору 41, на выходах которого выра5 батывается код адреса, соответствующий установленному в анализаторе 39 чисел максимальному цифровому коду. По сигналу блока 42 управления код адреса переписывается с выходов шифратора 41 в счетчик 37

0 адресного блока 36, Затем по коду адреса определяется регистр 35, в которой из ПЧК заносится новый цифровой код на место найденного максимального цифрового кода, Кроме того, в анализаторе 39 чисел

5 сбрасывается Т для маскирования (выключение из работы) содержимого регистра 35 i до тех пор, пока не будет заключена обработка предыдущего массива цифровых кодов, размер которого определяется числом

0 входных сигналов на шине I. Управление работой и синхронизацию всех узлов в блоке 27 выполняет блок 42 управления, имеющий управляющие входы 43.

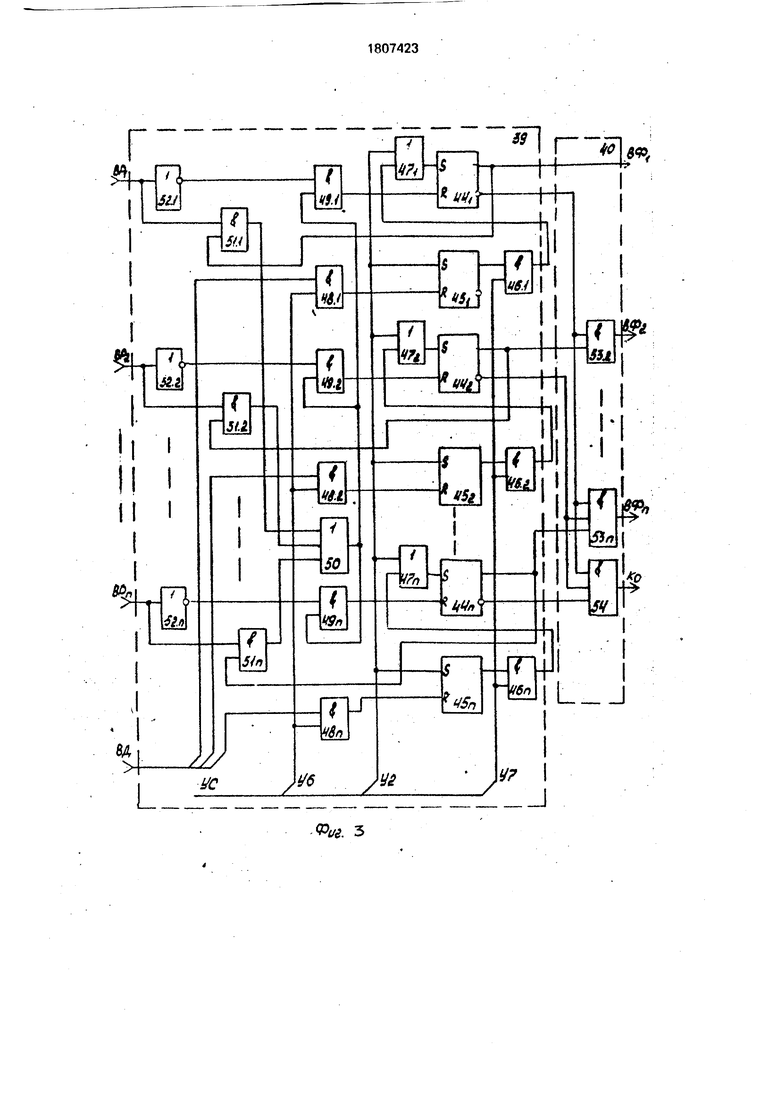

На фиг.З показана функциональная схе5 ма анализатора 39 чисел и приоритетного формирователя 40. Анализатор чисел содержит тяговые Т 44i-44n, , первую группу элементов И 46i-46n, необходимую для передачи значений Т45г45п в T44i-44n,

.0 группу элементов ИЛИ 47i-47n, вторую группу элементов И 48i-48n, третью группу элементов И 49i-49n, n- входовой элемент ИЛИ 50, четвертую группу элементов И 51i-51n и группу инверторов . В

5 состав приоритетного формирователя входят группа элементов И и п-входо- вой элемент И 54.

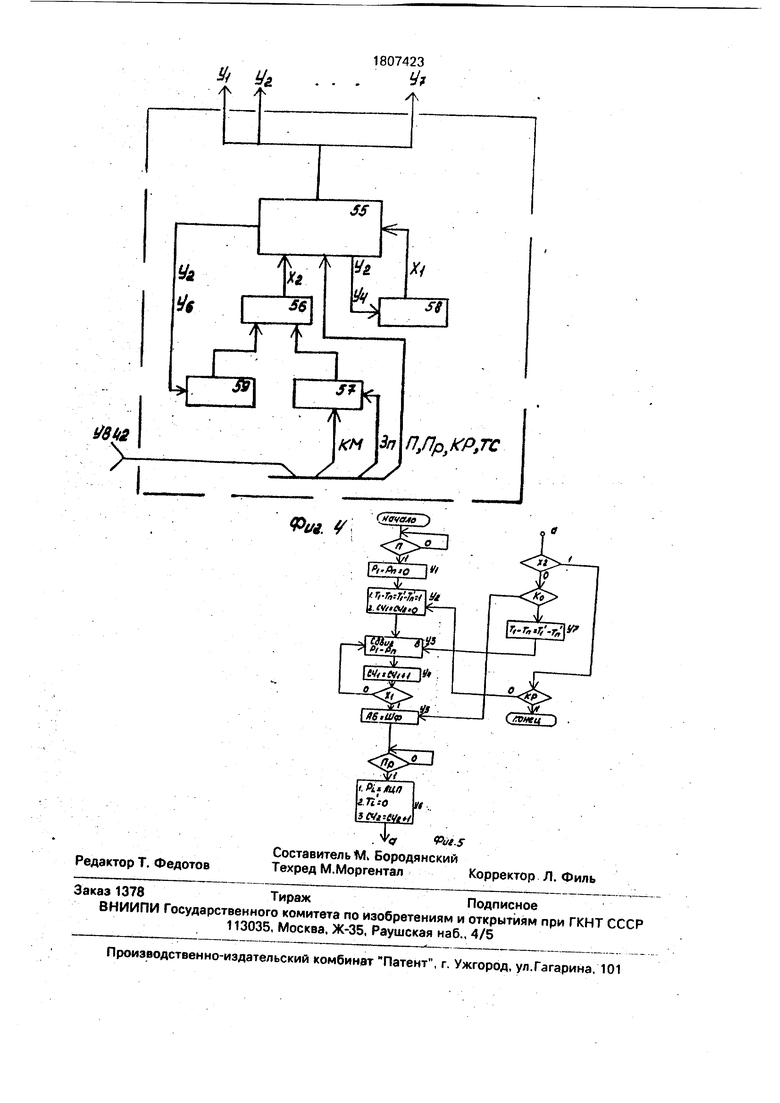

На фиг.4 представлена структурная схема блока 42 управления, в состав которого входят автомат 55 управления, блок 56 сравнения, регистр 57 и два счетчика 58 и 59. Автомат 55 управления может быть реализован по известным принципам, как автомат Мура или автомат Мили. Счетчик 58 необходим для определения конца сдвига цифрового кода из регистров 35i-35n, a счетчик 59 предназначен для подсчета количества уже упорядоченных цифровых кодов в анализаторах 39 чисел для определения конца обработки массива цифровых кодов. Это необходимо делать в том случае, если массивы цифровых кодов имеют произвольные размеры ( п). Тогда регистр 57 используется для записи кода границы массива (КМ) по сигналу Зп, например, со сторону пульта управления, который на фиг.2 и 4 не показан. Для синхронизации работы автомата 55 управления применяются тактовые сигналы (ТС).

Принцип функционирования блока 27 управления номером канала описывается графом микропрограммы (фиг.5), реализуемым автоматом 55 управления.

По управляющим входам 43 в блок 42 управления поступает сигнал ПУСК (П). С приходом первого сигнала ТС блок управления формирует сигнал YI, по которому регистры устанавливаются в нулевое состояние. По второму сигналу ТС блок 42 управления вырабатывает сигнал Y2, выпол- няющий установку в единичное состояние триггеров и 45i-45n в анализаторе 39 чисел и сброс счетчиков 58 и 59 в нулевое состояние. В соответствии с третьим сигналом ТС блок 42 управления формирует сиг- нал Уз, вызывающий сдвиг информации в регистрах 35i-35n на один разряд. Затем в следующем такте содержимое счетчика 58 увеличивается на единицу (в счетчике 58 отмечается число сдвигов информации для оп- ределения момента окончания вывода цифровых кодов). Если сигнал окончания вывода Xi 0 на выходе счетчика 58, то в 4цикле происходит поочередная выработка сигналов Уз и УА. При Xi 1 (установлен первый максимальный цифровой код, в анализаторе 39 чисел Т 44i, TI 1) блок 42 управления формирует сигнал YS, по которому выполняется передача кода адреса из шифратора 41 в адресный блок 36.

После этого блок 42 управления ожидает поступления внешнего сигнала ПРИЕМ (ПР), сообщающего о наличии цифрового ко- да на входах регистров 35i-35n. С приходом очередного сигнала ТС блок 42 управления формирует сигнал Ye, выполняющий, во- первых, запись из ПЧК цифрового кода в регистр 35i в соответствии с его кодом адреса, во-вторых, сброс 45i в нулевое состояние (маскируется 1-й максимальный цифровой

код); и, в-третьих, увеличивается содержимое счетчика 59 на единицу. Затем блок 42 управления организует свою работу в соответствии со значениями осведомительных сигналов Х2. Конец опроса (КО), поступающего из приоритетного формирователя 40, - конец работы (КР). Если Ха 0 (не просмотрены все входные сигналы) и КО 0 (наличие нескольких равных максимальных цифровых кодов), то вновь выполняется блоком 42 управления поочередное формирование сигналов Ys, Ye. При Х2 0 и КО 1 блоком управления формируется сигнал YT, по которому осуществляется перезапись содержимого Т в Т 44г-44з.

. С помощью триггеров И 44i-44n осуществляется определение одного или нескольких максимальных цифровых кодов. Триггеры И 45i-45n используются для маскирования (исключения из работы)тех регистров блока 34 памяти, в которых хранились найденные максимальные цифровые коды.

Рассмотрим более подробно процесс установления максимального цифрового кода.

Предварительно сигналом Ya блока 42 управления Т 44i-44n и 45i-45n установлены в единичное состояние. Затем на входы BPi-BPn анализатора 39 чисел поступают битовые срезы из регистров 35i-35n старшими разрядами вперед. При наличии в битовом срезе хотя бы одной единицы на выходе элемента ИЛИ 50 формируется единичный уровень сигнала, который поступает на первые входы группы элементов И 49i-49n. На вторые входы группы элементов И 49i-49n поступают соответствующие биты цифровых кодов. Если бит (Б 0 равен 1, то Т 44| не сбрасывается в нулевое состояние. В нулевое состояние переходит тот Т 44j, у Которого Bj 0. Таким образом, после прохода всех битовых срезов цифровых кодов несброшенные в нулевое состояние Т фиксируют максимальные (равные) цифровые коды в соответствующих регистрах. Для поочередного выделения единичного Т 44 i используется приоритетный формирователь 40.

После того, как с помощью шифратора 41 определен код адреса и занесен в адресный блок 36, выполняется сброс сигналом Ye блока 42 управления Т 45t в нулевое состояние. Это осуществляется для того, чтобы исключить найденный максимальный цифровой код из дальнейшего упорядочения. Затем по сигналу Y блока 42 управления содержимое Т 45i-45n переписывается в ,Т 44i-44n и для оставшихся цифровых кодов выполняется поиск максимального цифрового кода.

Многоканальный измеритель интенсивности импульсов с широким динамическим диапазоном работает следующим образом.

В исходном состоянии счетчики 4, 12, 20, Т б. 8, 15, 17, регистры 30 и 31, блок 27 управления номером канала устанавливаются в нулевое состояние, а входы мультиплексора соединены с соответствующими номерами датчиков. По команде ПУСК с блока управления Т 17 устанавливается в единичное состояние и разрешает прохождение импульсов с выхода мультиплексора 2 на вход счетчика А и прохождение импульса с тактового генератора через делитель 25 и мультиплексор 26 на вход счетчиков 4 и 20 одного порядка; причем если ттакт fax, то к моменту заполнения счетчиков 20 и 4 устанавливается число, пропорциональное интенсивности поступления импульсов. По достижении счетчиком 20 числа 1000 с выхода дешифратора 22 сигнал устанавливает Т 17 в нулевое состояние и с задержкой, определяемой элементом 18, поступает в блок управления, который вырабатывает команду переписи информации из счетчика 12 в блок 27, а по следующему такту переписи информации из счетчиков 4 и 12 в регистрирующее устройство 28.

В случае, если fBx оказалось существенно больше или меньше fiatcr fт fax или tV « fox (fax fe, fax н). то срабатывает система, обеспечивающая переключение диапазонов. По комбинации сигналов дешифратора ДСН ДСВ Т 6 и 8 занимают соответствующие состояния, которые ин- формируются шифратором и через элементы И 10 и 11 воздействуют на счетчик 12, увеличивая или уменьшая число в нем. Это число определяет диапазон измеряемого сигнала и соответственно через мульти- плексор 2 выбирает номер выхода делителя частоты для подключения счетчика 20. В случае, если при поступлении сигнала с дешифратора 22 на выходе схемы ИЛИ будет сигнал, свидетельствующий о наличии необ- ходимости переключения диапазона, то элемент И 14 Т 15 устанавливается в нулевое состояние и запрещает прохождение задержанного импульса с дешифратора 22 на вход блока 29. При этом через схему ИЛИ 16 Т 17 устанавливается в единичное состояние и процесс измерения интенсивности по тому же каналу повторяется, но на другом диапазоне измерения. Переключение с канала на канал в процессе измерения всего массива каналов осуществляется в порядке, определяемом блоком 27, который осуществляет ранжирование каналов по уровню интенсивности поступления импульсов в каждом из них (например, в порядке возрастания). По завершении измерения очередного канала информация о диапазоне измерения этого канала поступает в блок 27. где после обработки за время измерения следующего канала с выхода блока 27 номер очередного канала записывается в регистр 31. Поэтому после записи информации в регистр 31 и блок 27 блок 29 осуществляет перепись значения номера канала, подлежащего измерениям из регистра 31 в регистр 30.

Таким образом, упорядочение последовательности подключения каналов для измерения в порядке убывания (возрастания) интенсивности в них обеспечивает мини- мгтьное время поиска диапазона при переходе от канала к каналу и тем самым существенное сокращение времени преобразования группы каналов, т.е. увеличение быстродействия.

Например, для ухудшения случая, когда в группе из N каналов по четным каналам поступают сигналы с высоким уровнем интенсивности, а по нечетным - с низким уровнем, оценим величину выигрыша.

Предположим, что TI - время измерения канала с высоким уровнем интенсивности; Та - время измерения канала с низким уровнем интенсивности; Tin - время поиска диапазона при переходе от верхнего до нижнего диапазонов; Т2п - время поиска диапазона при переходе от нижнего до верхнего диапазонов.

Примем следующие соотношения:

Ti « Та, Tni Тп2 и .

Тогда в первом случае, когда измерение ведется без упорядочения, общее время измерения группы из N каналов будет

тт- N...-г N, Тизм1 Tl-jj-H- Та -j-t- Tni -rf-+

+Тпа() - -у- (Ti + Т2+Tni + ТП2) .

Во втором случае, когда измерение ведется с упорядочением, общее время измерения группы каналов будет

N

+Та) + Тпа + ТП1

Л 2

N +2

N

ТИзм2 Тг-у-+ Та -лг+ Тпа + ТП1 -гг-0 1+

1 Та

Таким образом, для принятых условий выигрыш можно оценить:

М

Формула изобретения

Многоканальный измеритель интенсивности импульсов, содержащий блок управления, первый дешифратор, делитель частоты, четыре элемента И. блок датчиков, генератор, мультиплексор и регистрирующее устройство, отличающийся тем, что, с целью увеличения быстродействия, в него введены второй мультиплексор, три счетчика импульсов, четыре триггера, второй, третий, четвертый и пятый дешифраторы, пятый и шестые элементы И, два элемента ИЛИ, два элемента задержки, два регистра, шифратор, блок управления номером канала, причем выходы блока датчиков через первый мультиплексор подключены к первому входу первой схемы И, выход которой подключен к первому входу первого счетчика, первый выход которого соединен через первый дешифратор с первым входом второго триггера, а второй выход через второй дешифратор соединен с первым входом третьего триггера, причем выходы второго и третьего триггеров подключены к входу первого шифратора соответственно, первый и второй выходы которого через второй и третий элементы И подключены соответственно к вычитающему и суммирующему входам второго счетчика импульсов и через первую схему ИЛИ к первому входу четвертого элемента И, выход которого соединен с первым входом четвертого триггера и первому входу второго элемента ИЛИ, выход которого подключен к первому входу первого триггера, к вторым входам первого счетчика импульсов, второго и третьего триггеров, а через первый элемент задержки - к второму входу

четвертого триггера, выход которого соединен с первым входом шестого элемента И, второй вход которого подключен к первому входу третьего счетчика и через второй элемент задержки к выходу пятого дешифратора, вторым входам второго, третьего, четвертого элементов И и к второму входу первого триггера, выход которого соединен с вторым входом первой схемы И, и первому

входу пятой схемы И, второй вход которой подключен к первому генератору, а выход через первый делитель - к первому входу второго мультиплексора, выход которого через второй вход третьего счетчика соединен

с входом пятого дешифратора, а второй вход второго мультиплексора - с выходом второго счетчика импульсов и первым входом блока управления номером канала и регистрирующим устройством, второй вход

которого соединен с третьим выходом первого счетчика, а третий вход подключен к первому выходу блока управления, второй выход которого соединен с вторым входом второго элемента ИЛИ, третий выход - с

вторым входом блока управления номером канала, четвертый выход-с первым входом первого регистра, выход которого подключен к управляющему входу первого мультиплексора, а второй вход - к выходу второго

регистра, второй вход которого соединен с соответствующим выходом блока управления номера канала, причем выход шестого элемента И соединен с входом блока управления, а второй и третий выходы второго

счетчика импульсов через соответствующий третий и четвертый дешифраторы подключены к третьим входам второй и третьей схемы И.

dmГМ t

---

лП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для выделения признаков при распознавании случайных сигналов | 1990 |

|

SU1797134A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Селекторный канал | 1982 |

|

SU1053096A1 |

| Полевая телеметрическая сейсмическая станция | 1986 |

|

SU1327031A2 |

Изобретение относится к измерительной технике и может быть использовано при регистрации случайных импульсных потоков, поступающих от детекторов ионизирующих излучений. Измеритель содержит блок 1 датчиков, мультиплексоры 2,26, схемы И 3, 10,11,14,19,23, счетчики 4,12,20 импульсов, дешифраторы 5,7,22,32,33, триггеры 6,8,15, 17. шифратор 9, схемы ИЛИ 13,16, элементы 18. 21 задержки, генератор 24 импульсов, делитель 25, блок 27 управления каналами, регистрирующее устройство 28, блок 29 управления, регистры 30, 31. 1 табл., 5 ил.

Фиг. г

L

«W. з

iff У&

1807423 #

| Цифровой измеритель средней частоты | 1977 |

|

SU705360A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-04-07—Публикация

1991-06-03—Подача