1

Изобретение относится к области аналогоцифровой техники, а также области радиотехники, использующей дискретные методы обработки сигналов, и предназначено для дискретизации непрерывных сигналов. Оно может найти применение при построении аналогоцифровых преобразователей и нри согласовании анало,говых и цифровых устройств в различных системах обработки сигналов.

Известно устройство выборки и запоминания 1, содержащее последовательный аналоговый ключ на биполярном транзисторе. Известно устройство выборки и запоминания 2, содержащее последовательный ключ на полевом транзисторе.

Недостатком таких зстройств выборки и запоминания является сравнительно высокий уровень пролезаний через паразитные параметры ключей, что ограничивает как точность их работы, так и достижимую частоту дискретизации.

Из известных устройств выборки и запоминания наиболее близким по технической сущности является устройство 3, содержащее п-р-«-транзистор, база которого подключена ко входу устройства и через первый резистор к щине нулевого потенциала и к одной из обкладок конденсатора. Эмиттер л-р-п-транзистора соединен через второй резистор с отрицательной щиной питания. Другая обкладка

конденсатора подключена к выходу устройства и к коллектору первого р-п-р-транзистора, а через третий резистор к эмиттеру второго р-п-р-транзистора, база которого соединена с коллектором третьего р-п-р-транзистора, коллекторы я-р-п-транзистора и второго р-п-р-транзистора подсоединены к шинам питания соответственно, четвертый резистор, шину напряжения смещения, шину стробирования и шину напряжения ограничения. Недостатками прототипа являются: ограниченное быстродействие в режиме образования выборочного значения, обусловленное наличием ограничительного резистора и

использованием насыщенного параллельного ключа;

ограниченная частота дискретизации, связанная с необходимостью полного разряда накопительного конденсатора сравнительно малым коллекторным током разрядного транзистора перед каждым новым стробом;

наличие существенных погрешностей образования выборочных значений при работе на нарастающих зчастках входного сигнала, что

обусловлено работой выходного транзистора в режиме, близком к режиму иикового детектора и отнесением выборочных значений к моментам окончания стробов;

униполярность схемы с точки зрения входного сигнала.

Целью изобретения является повышение быстродействия устройства.

Эта цель достигается тем, что предложенное устройство содержит диод, анод которого подключен к эмиттеру л-р-я-транзистора, к базе второго р-п-р-транзистора и к коллектору третьего р-п-р-транзистора, эмиттер которого соединен с эмиттером первого р-п-ртранзистора и через четвертый резистор с положительной шиной питания. Базы третьего и первого р-п-/7-транзисторов подключены к шине стробируюш,его импульса и шине напряжения смеш,ения соответственно. Катод диода соединен с шиной напряжения ограничения.

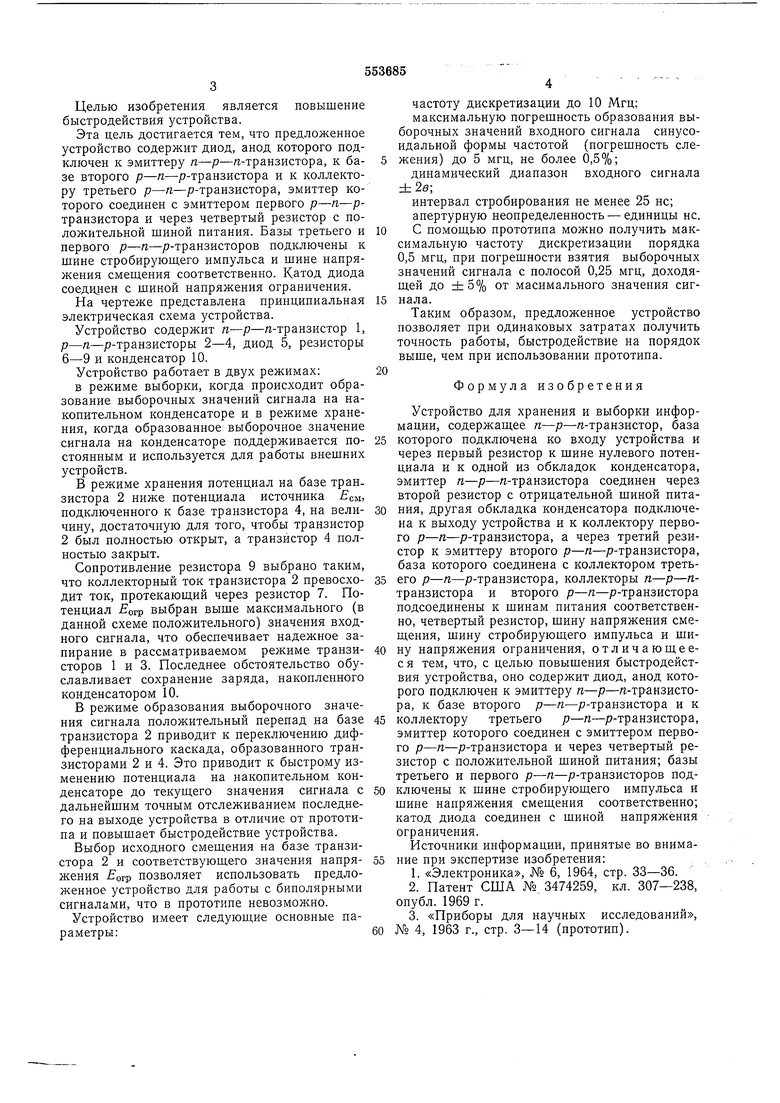

На чертеже представлена принципиальная электрическая схема устройства.

Устройство содержит п-р-«-транзистор 1, р-п-р-транзисторы 2-4, диод 5, резисторы 6-9 и конденсатор 10.

Устройство работает в двух режимах:

в режиме выборки, когда происходит образование выборочных значений сигнала на накопительном конденсаторе и в режиме хранения, когда образованное выборочное значение сигнала на конденсаторе поддерживается постоянным и используется для работы внешних устройств.

В режиме хранения потенциал на базе транзистора 2 ниже потенциала источника смподключенного к базе транзистора 4, на величину, достаточную для того, чтобы транзистор 2 был полностью открыт, а транзистор 4 полностью закрыт.

Сопротивление резистора 9 выбрано таким, что коллекторный ток транзистора 2 превосходит ток, протекаюш;ий через резистор 7. Потенциал огр выбран выше максимального (в данной схеме положительного) значения входного сигнала, что обеспечивает надежное запирание в рассматриваемом режиме транзисторов 1 и 3. Последнее обстоятельство обуславливает сохранение заряда, накопленного конденсатором 10.

В режиме образования выборочного значения сигнала положительный перепад на базе транзистора 2 приводит к переключению дифференциального каскада, образованного транзисторами 2 и 4. Это приводит к быстрому изменению потенциала на накопительном конденсаторе до текущего значения сигнала с дальнейшим точным отслеживанием последнего на выходе устройства в отличие от прототипа и повышает быстродействие устройства.

Выбор исходного смешения на базе транзистора 2 и соответствующего значения напряжения огр позволяет использовать предложенное устройство для работы с биполярными сигналами, что в прототипе невозможно.

Устройство имеет следующие основные параметры:

частоту дискретизации до 10 Мгц;

максимальную погрешность образования выборочных значений входного сигнала синусоидальной формы частотой (погрешность слежения) до 5 МГЦ, не более 0,5%;

динамический дианазон входного сигнала ±28;

интервал стробирования не менее 25 не;

апертурную неопределенность - единицы не.

С помощью прототипа можно получить максимальную частоту дискретизации порядка 0,5 МГЦ, при погрещности взятия выборочных значений сигнала с полосой 0,25 мгц, доходящей до ±5% от масимального значения сигнала.

Таким образом, предложенное устройство позволяет при одинаковых затратах получить точность работы, быстродействие на порядок выше, чем при использовании прототипа.

Формула изобретения

Устройство для хранения и выборки информации, содержащее п-р-п-транзистор, база которого подключена ко входу устройства и через первый резистор к шине нулевого потенциала и к одной из обкладок конденсатора, эмиттер п-р-«-транзистора соединен через второй резистор с отрицательной шиной питания, другая обкладка конденсатора подключена к выходу устройства и к коллектору первого р-п-р-транзистора, а через третий резистор к эмиттеру второго р-п-р-транзистора, база которого соединена с коллектором третьего р-п-р-транзистора, коллекторы п-р-птранзистора и второго р-п-р-транзистора подсоединены к шинам питания соответственно, четвертый резистор, шину напряжения смещения, шину стробирующего импульса и шину напряжения ограничения, отличающеес я тем, что, с целью повышения быстродействия устройства, оно содержит диод, анод которого подключен к эмиттеру п-р-«-транзистора, к базе второго р-п-р-транзистора и к коллектору третьего р-п-р-транзистора, эмиттер которого соединен с эмиттером первого р-я-р-транзистора и через четвертый резистор с положительной шиной питания; базы третьего и первого р-п-р-транзисторов подключены к шине стробирующего импульса и шине напряжения смещения соответственно; катод диода соединен с шиной напряжения ограничения.

Источники информации, принятые во внимание при экспертизе изобретения:

1.«Электроника, № 6, 1964, стр. 33-36.

2.Патент США № 3474259, кл. 307-238, опубл. 1969 г.

3.«Приборы для научных исследований, № 4, 1963 г., стр. 3-14 (прототип).

0-Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104587A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU903988A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1261013A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Устройство для выборки и хранения информации | 1986 |

|

SU1388955A1 |

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Устройство выборки и хранения | 1988 |

|

SU1571680A1 |

Авторы

Даты

1977-04-05—Публикация

1975-06-02—Подача