(5) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1973 |

|

SU517941A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Аналоговое запоминающее устройство | 1986 |

|

SU1345262A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU634374A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1261013A1 |

| Устройство для хранения и выборки информации | 1975 |

|

SU553685A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Генератор стробирующих импульсов для стробоскопического осциллографа | 1982 |

|

SU1072256A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено пя хранения выбранного значения напряжения сигнала и может быть использовано при построении аналого-цифровых преобразователей и при согласовании аналоговых и цифровых устройств в системах обработки сигналов. Известно аналоговое запоминающее устройство, содержащее накопительный конденсатор, р-п-р-транзисторы, п-р-п-транзистор, резисторы и ключ .11 Однако известное устройство характеризуется невысоким быстродействием и точностью. Наиболее близким к предлагаемому по технической сущности является аналоговое запоминающее устройство, которое содержит п-р-п-транзистор, р-п-р-транзисторы, диод, резисторы, накопительный конденсатор, шину стро бирующего импульса, шину питания. шину напряжения смещения и шину напряжения ограничения 21. Недостатками известного устройства являются пролезание импульса, формирующегося на аноде диода и имеющего значительную амплитуду, равную в худшем случае динамическому диапазону входного сигнала через база-эмиттерную емкость второго эмиттерного повторителя на запоминающий конденсатор, низкая статическая точность коэффициента передачи устройства, определяемая тем, что первый и второй эмиттерные повторители выполнены на транзисторах различного типа проводимости и работают при разных эмиттерных , так как в известной схеме необходимо иметь сравнительно более мощный второй эмиттерный повторитель. В режиме выборки при перезарядке запоминающего конденсатора от положительных значений напряжения к более отрицательным он пропускает

через себя кроме тоКа перезаряда конденсатора выходной ток переключателя тока, ток которого, в свою очередь, должен быть больше эмиттерного тока первого эмиттерного повторителя.

Кроме того, наличие задержки включения/выключения устройства, определяемой необходимостью перезаряда паразитной емкости, подключенной к аноду диода, на напряжение, равное в худшем случае динамическому диапазону входного сигнала.

Цель изобретения - повышение точности и быстродействия устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее накопительный элемент,например конденсатор, первый п-р-п-транзистор, база которого соединена со входом устройства и через первый резистор с шиной нулевого потенциала, второй п-р-п-транзистор, включенный диодом, первый, второй и третий р-п-р-транзисторы, второй и третий резисторы, шину стробирующего импульса, шины питания и шину напряжения смещения, введены третий и четвертый п-р-п-транзисторы, эмиттеры которых соединены через второй резистор с первой шиной питания, базы третьего и четвертого п-р-п-транзисторов соединены соответственно с шиной стробирующего импульса и с шиной напряжения смещения, коллектор третьего п-р-п-транзистора соединен с шиной нулевого потенциала, коллектор четвертого п-р-п-транзистора соединен с эмиттерами первого и второго п-р-п-транзисторов, коллекторы которых соединены соответственно с коллекторами первого и второго р-п-ртраузисторов, коллектор и база второго п-р-п-транзистора соединены с выходом устройства и с одной из обкладок конденсатора, другая обкладка которого соединена с шиной нулевого потенциала, эмиттеры первого и второго р-п-р-транзисторов соединены со вторрй шиной питания, базы первого и второго р-п-р-транзисторов соединены через третий резистор со второй шиной питания, база третьего р-п-р-тран.зистора,подключена к коллектору первого п-р-п-транзистора, коллектор третьего р-п-р-транзистор соединен с шиной нулевого потенциала,а эмиттер - с базами первого и второго . р-п-р-транзисторов.

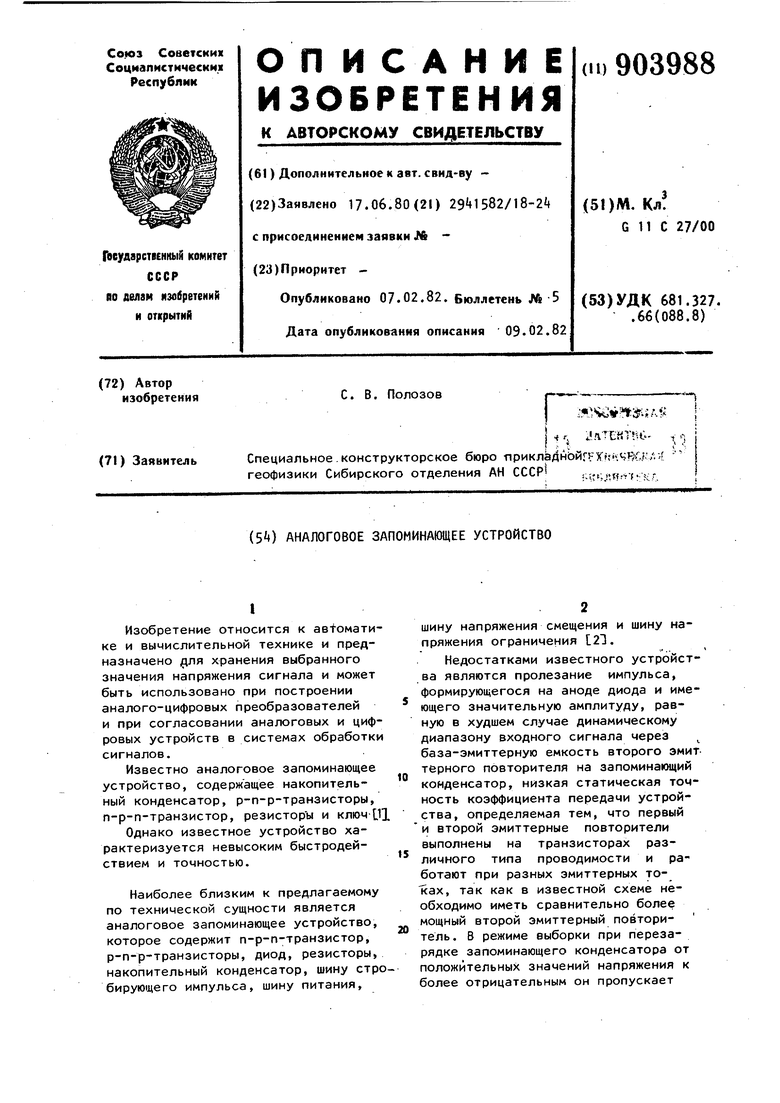

На чертеже изображена электрическая схема предлагаемого аналогового запоминающего устройства.

Устройство содержит п-р-п-транзисторы 1-, р-п-р-транзистрры 5-7, резисторы 7-9, накопительный элемент, например конденсатор 10, шину 11 стробирующего импульса, шины 12 и 13 питания, шину }k напряжения смещения

и шину 15 нулевого потенциала. Транзисторы 5-7 и резистор 9 образуют стабилизатор тока, на основе токового зеркала. Транзисторы 3 и i. и резистор 8 образуют управляемый генератор

тока. Транзистор 2 включен по схеме диода.

Предлагаемое устройство функционирует следующим образом.

В режиме выборки на шину 11 подается стробирующий импульс, в результате чего открывается транзистор и его ток перераспределяется между транзисторами 1 и 2 в зависимости от уровней сигнала на входе устройства

и напряжения на конденсаторе 10. Если входной сигнал более положителен, |чем напряжение на конденсаторе 10, то транзистор 1 открыт, а транзистор 2 закрыт, коллекторный ток транзистора 1 поступает на базу транзистора 7 и через транзистор 6 начинается заряд конденсатора 10 до более положительных значений напряжения до тех пор, пока входное напряжение и напряжение на конденсаторе 10 не сравняются с точностью до разности базаэмиттерного напряжения транзистора и падения напряжения на транзисторе 2. При этом ток управляемого генератора тока, образованного транзисторами 3 и и, перераспределяется поровну между транзисторами 1 и 2 и дальнейшего изменения напряжения на конденсаторе 10 не будет. При условии

идентичности вольт-амперных характеристик база-эмиттерного перехода транзисторов 1 и 2 выходное напряжение будет в точности равно входному напряжению. В том случае, KOI- да входное напряжение меньше напряжения на конденсаторе 10, транзисторы 3 и через открытый транзистор 2 разряжают конденсатор 10 до выравнивания уровней входного напряжения и напряжения на конденсаторе 10.

В режиме хранения транзисторы 3 и Ц закрыты, транзистор 1 и транзисторы 2, 5-7 обесточены и напряжение на конденсаторе 10 не изменяется. Цепь вход-выход разомкнута встречно включенными база-эмиттерными переходами транзисторов 1 и 2.

Транзистор 2 используется в диодном включении, идентичный по характеристикам первому п-р-п-транзистору. Коллектор и база его объединены и служат анодом эквивалентного диода, а эмиттер - катодом диода.

Повторитель тока, выполненный на основе токового зеркала на транзисторах 5-7 имеет близкий к единице коэффициент передачи тока и высокое быстродействие, определяемое тем, что транзисторы 5-7 работают в ненасыщенном режиме и заряд в базах транзисторов 5 и 6 быстро разряжается через низкоомный резистор 9.

Использование предлагаемого устройства позволяет по сравнению с известным вдвое увеличить частоту образования выборок сигнала, вдвое уменьшить погрешность слежения за сигнал6м)в три раза уменьшить апертурную неопределенность, в 10 раз уменьшить смещение уровня выходного сигнала в момент перехода к режиму слежения.

Формула изобретения

Аналоговое запоминающее устройство, содержащее наокпительный элемент, например конденсатор, первый п-р-птранзистор, база которого соединена со входом устройства и через первый резистор с шиной нулевого потенциала, второй п-р-п-транзистор, включенный диодом, первый, второй и третий р-п-р-транзисторы, второй и

третий резисторы, шину стробирующего импульса, шины питания и шину напряжения смещения, отличающееся тем, что, с целью повышения точности и быстродействия устройства в него введены третий и четвертый п-р-п-транзисторы, эмиттеры которых соединены через второй резистор с первой шиной питания, базы третьего и четвертого п-р-п-транзисторов соединены соответственно с шиной стробирующего импульса и с шиной напряжения смещения, коллектор третьего п-р-п-тр; нзистора соединен с шиной нулевого потенциала, коллектор четвертого п-р-п-транзистора соединен с эмиттерами первого и второго п-р-птранзисторов, коллекторы которых соединены соответственно с коллекторами первого и второго р-п-р-тра«зисторов, коллектор и база второго п-р-п-транзистора соединены с выходом устройств и с одной из обкладок конденсатора, другая обкладка которого соединена с шиной нулевого потенциала, эмиттеры первого и второго р-п-р-транзисторов соединены со второй шиной питания , базы первого и второго р-п-р-транзисторов соединены через третий резистор., со второй шиной питания, база третьего р-п-ртранзистора подключена к коллектору первого п-р-п-транзистора, коллектор третьего р-п-рТ(анзистора соединен с шиной нулевого потенциала, а эмиттер - с базами первого и второго р-п-р-транзисторов.

Источники информации, принятые во внимание при экспертизе

Cmfmff iX

/ //

«W

Авторы

Даты

1982-02-07—Публикация

1980-06-17—Подача