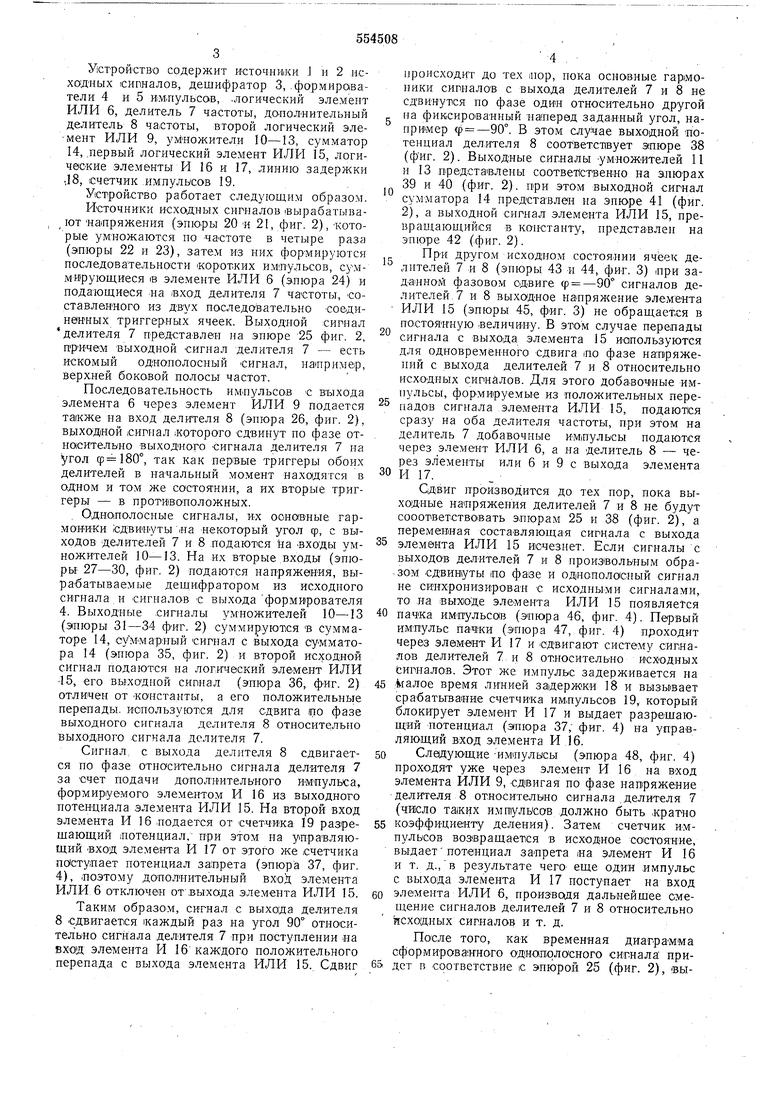

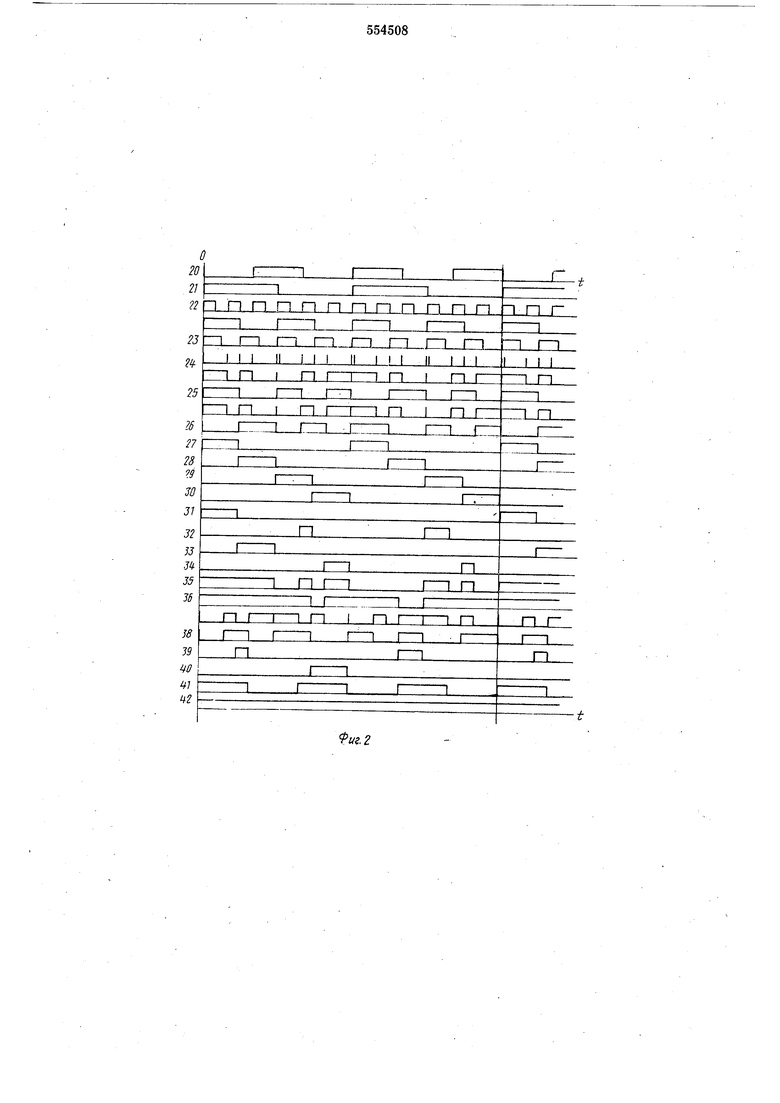

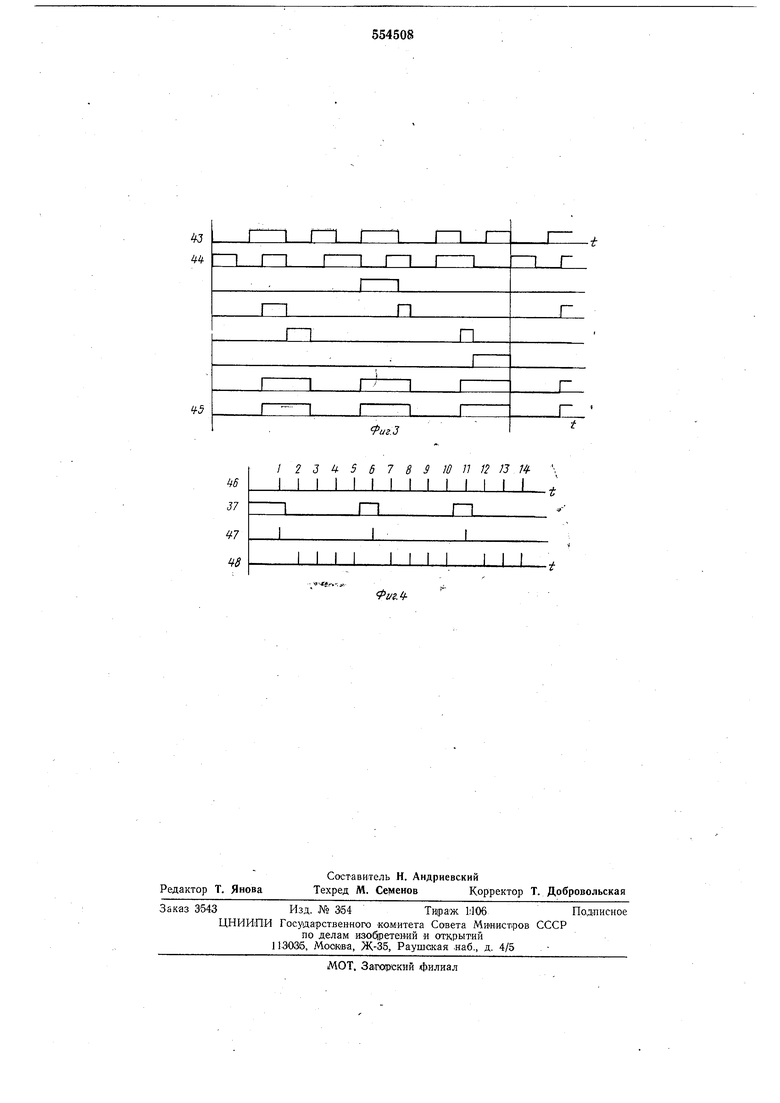

Устройство содержит источники J и 2 исходных сигналов, дешифратор 3, .формирователи 4 и 5 имлульсов, .логический элемент ИЛИ 6, делитель 7 частоты, дополнительный делитель 8 частоты, второй логический эле-мент ИЛИ 9, умножители 10-13, сумматор 14, .первый логический элемент ИЛИ 15, логические элементы И 16 и 17, линию задержки 18, счетчик .импульсов 19. Устройсгво работает следующим образом. Источники исходных сигналов (вырабатывают «а/пряжения (эпюры 20 « 21, фиг. 2), которые умножаются по частоте в четыре раза (эпюры 22 и 23), затем из них формируются последовательности коротких иматульсов, суммирующиеся IB элементе ИЛИ 6 (эпюра 24) и подающиеся на (Вход делителя 7 частоты, составленного из двух последовательно соединенных триггерНых ячеек. Выходной сигнал делителя 7 представлен на эпюре 25 фиг. 2, причем выходной сигнал делителя 7 - есть искомый однонолосный сигнал, иа1приме1р, верхней боковой полосы частот. Последовательность имлульсов с выхода элемента 6 через элемент ИЛИ 9 подается та|кже на вход делителя 8 (эпюра 26, фиг. 2), выходной сигнал ;которого сдвинут по фазе относительно -выходного сигнала делителя 7 на угол , так как первые триггеры обоих делителей в начальный момент находятся в одном и том же состоянии, а их вторые триггеры - в ПрОТИ ВОПОЛОЖИЫХ. Однополосные сигналы, их основные гармоники |сдвиНуты на некоторый угол ф, с выходов делителей 7 и 8 .подаются на «ходы умножителей . На их вторые.входы (эпюры- 27-30, фиг. 2) подаются нап-ряжения, выра-батываемые дешифратором из исходного сигнала . и сигнало в с выхода формирователя 4. Выходные сигналы умножителей 10-13 (эпюры 31-34 фиг. 2) суммируются в сумматоре 14, суМмаряый сигнал с выхода сумматора 14 (эпюра 35, фиг. 2) и второй исходной сигнал подаются на логический элемент ИЛИ 15, его выходной сипнал (эпюра 36, фнг. 2) отличен от Константы, а его положительное перепады, используются для сдвига по фазе выходного сигнала делителя 8 относительно выходного сигнала делителя 7. Сигнал, с выхода делителя 8 сдвигается по фазе отнасительно сигнала делителя 7 за счет подачи до полнительного импульса, формируемого элементом И 16 из выходного потендиала элемента ИЛИ 15. На второй вход элемента И 16 подается от счетчика 19 разрещающий .Потенциал, при этом на управляющий ВХОД элемента И 17 от этого же счетчика по1ступает потенциал заПрета (эпюра 37, фиг. 4), поэтому донолнительный вход элемента ИЛИ 6 отключен от .выхода элемента ИЛИ 15. Таким образом, сигнал с выхода дел-ителя 8 сдвигается каждый раз иа угол 90° относительно сигнала .делителя 7 при поступлении на вход элемента И 16каждого положительного перепада с выхода элемента ИЛИ 15. Сдвиг происходит до тех inop, пока основные гармоники сигналов с выхода делителей 7 и 8 не сдвинутся по фазе один относительно другой на фиксир01ванный на первд зада.нный угол, например ф -90°. В этом слу;чае выходной потенциал делителя 8 соответствует э:пюре 38 (фиг. 2). Выходные сигналы ум-нож«телей 11 и 13 вредставлены соотвеКствеННо на эпюрах 39 и 40 (фиг. 2). при этом выхо-дной сигнал сумматора 14 представлен на эпюре 41 (фиг. 2), а выходной сигна.л элемента ИЛИ 15, преврап ающийся в константу, представлен на эпюре 42 (фиг. 2). ИрИ другом исходном состоянии ячеек делителей 7 и 8 (эпюры 43 и 44, фиг. 3) лри заданной фазовом сдвиге ф -90° сигналов делителей. 7 и 8 выходное напряжение элемента ИЛИ 15 (эпюры 45, фиг. 3) не обращается в постояиную величину. В этом случае перепады сигнала с выхода элемента 15 иапользуются для одновременного сдвига по фазе иапряжеиий с выхода делителей 7 и 8 относительно исХОДных сигийлов. Для этого добаВочные импульсы, формируемы-е из положительных перепадов сигнала элемента ИЛИ 15, подаются сразу на оба делителя частоты, при этом на делитель 7 добавочные импульсы подаются через элемент ИЛИ 6, а на делитель 8 - через элементы или 6 и 9 с выхо.да элемента И 17. Сдвиг производится до тех нор, пока выход-ные наПряжеиия делителей 7 и 8 не будут сооответствовать эпюрам 25 и 38 (фиг. 2), а переменная составляющая сигнала с выхо.да элемента ИЛИ 15 исчезнет. Если сигналы с выходов делИтелей 7 и 8 произвольным образом Сдвинуты по фазе и однополосный сигнал не синхронизирован с исходными сигналами, то .на выходе элемента ИЛИ 15 появляется пачка имггульсав (э1ПЮ1ра 46, фиг. 4). Иервый импульс пачки (эпюра 47, фиг. 4) проходит через элемент И 17 и сдвигают систему сигналов делителей 7. и 8 относительно исходных Сигна.лов. Этот же импульс задерживается на .kaaoe время линией задержки 18 и вызывает срабатывание счетчика импульсов 19, который блокирует элемент И 17 и выдает разрешающий потенциал (эпюра 37, фиг. 4) на управляЮЩий в-ход элемента И .16. Следующие -импулысы (эпюра 48, фиг. 4) проходят уже через эле.ме-нт И 16 на вход элемента ИЛИ 9, СДВигая по фазе напряжение делителя 8 относителыно сигнала .делителя 7 (число таких импульсов .должно быть «ратно коэф.фИЦиеиту деления). Затем счетчик импульсов возвращается в исходное соснюяние, выдаетпотенциал запрета на элемент И 16 и т. д.,в результате чего еще один .импульс с выхода элемента И 17 поступает на вход элемента ИЛИ 6, производя дальнейшее смещение сигналов делителей 7 и 8 относительно исходных сигналов и т. д. После того, как временная диаграмма сформированного одадаполосного сигнала придет п Соответствие с эпюрой 25 (фиг. 2), выходной сигнал элемента ИЛИ 15 исчезает, нроцесс синхронизации заканчивается. В дальнейшем при ВОЗМОЖНЫХ сбоях :В СИСТвМе СИНхронизм восстанавливается авто-матически.

Устройство ооллостью выПОЛНено .на стандартных микросхемах и имеет высокие метрологические параметры и надежность.

Формула и 3 о б р е т е н и я

Устройство для фор1мирования однополосного сигнала, содержащее источники исходных сигналов, иодключен.ные к ним формирователи коротких импульсов, которые своими выходами через логический элемент ИЛИ соединен с дел-ителем частоты, отличающееся тем, что, с целью устранения фазовой неоднозначности однополосного сигнала, в схему введены дополнительный делитель частоты, счетчик импульсов, первый к второй логические элементы ИЛИ, логические элементы И, сумматор, линия задержки, дешифратор и ум«ожител-и, ВХОДЫ которых подключены к выходам обоих делителей частоты н через дешифратор - к одно.му из источников исходного сигнала и к фор-мирователю коротких импульсощ, а выходы - через сумматор соединены с одним из входов первого логического

элемента ИЛИ, второй вход которого подключен к второму источнику исходного сигнала, выход его через логические элементы И соединен с -входами логического элемента ИЛИ и донолеителыпого второго логического элемента ИЛИ, выход которого связан со входом дополнительного делителя частоты, и один из входов подключен к выходу логического элемента ИЛИ, приче-м вторые входы логических элеме1 тов И подключены к выходам счетчика

импульсов, вход которого соединен с выходом первого дополнительного логического элемента ИЛИ через линию задержки.

Источ«и1ш информации, принятые во внимание при проведении экспертизы по данной

заявке:

1.,М. В. Верзунов и др. «Однонолосная модулящия, М., связьиэдат, 1962 г., стр. 51-61. 2. Авторское свидетельство № 259266, М. Кл.2 G ОШ, 25/00, 15.07.68 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный генератор импульсов | 1985 |

|

SU1257867A1 |

| Способ определения мгновенных значений фазового сдвига электрических сигналов | 1988 |

|

SU1559308A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1990 |

|

SU1714817A1 |

| Приемник сигналов офсетной фазовой манипуляции | 1987 |

|

SU1434559A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство синхронизации корреляционного приемника псевдослучайных сигналов | 1982 |

|

SU1069182A1 |

| Устройство для формирования дальномерного синхронизирующего кода | 1981 |

|

SU987835A1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ С КОДОВЫМ УПЛОТНЕНИЕМ СИГНАЛОВ | 1991 |

|

RU2014738C1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

29

Выход V/2

П1 /

- Выход О

Фиг. 1

20 21 22

PJZl П П П П П П П П.. П П r

I-i I-11-I i- I-I

n I n I I I n

in I n Г

n

JIL

n

L

Xl

JIl-I

П I n r

I n

n

n.

n I I in

n

Авторы

Даты

1977-04-15—Публикация

1975-12-02—Подача