1

Изобретение относится к связи и радиолокации и может использоваться в совмещенных системах измерения параметров движения и передачи информации и в системах связи, использующих «ансамбль ортогональных бинарных кодов.

Известно устройство слежения за задержкой, содержащее опорный генератор псевдослучайных видеопоследовательностей, выполненный на регистре сдвига с обратной связью, два разряда которого подключены к одним входам двух перемножителей, другие входы последних соединены с входной шиной.

Однако известное устройство имеет невысокую надежность работы.

Известно цифровое устройство слежения за задержкой псевдослучайных последовательностей, содержащее на входе два перемножителя, выходы которых подключены к соответствующим входам реверсивного счетчика и сумматора по модулю два, выход последнего через элемент И подключен к счетному входу реверсивного счетчика, а его выходы сложения и вычитания через последовательно соединенные управляющий элемент и делитель частоты подключены к входу генератора опорных сигналов, причем выход кварцевого генератора подключен к соответствующему входу элемента И.

Однако известное устройство не может использоваться в системах, использующих «ансамбль ортогональных бинарных кодов.

С целью обеспечения слежения за задержкой сигналов, передаваемых ортогональными бинарными кодами, в цифровое устройство слежения за задержкой псевдослучайных последовательностей введены распределитель, первый и второй элементы ИЛИ, 2п элементов И и rt элементов задержки (где п - число ортогональных бинарных сигналов), при этом каждый выход генератора опорных сигналов подключен к соответствующей паре элементов И, причем выход генератора опорных

сигналов подключен к первому входу одного элемента И непосредственно, а к первому входу другого - через элемент задержки, к управляющему входу которого подключен выход делителя частоты, а к вторым входам одного

и другого элементов И подключены соответствующие выходы распределителя, к управляющему входу которого подключен выход кварцевого генератора, кроме того, выходы нечетных элементов И через первый элемент ИЛИ

и выходы четных элементов И через второй элемент ИЛИ подключены к вторым входам соответствующих перемножителей, а один из выходов распределителя подключен к соответствующему входу управляющего элемента.

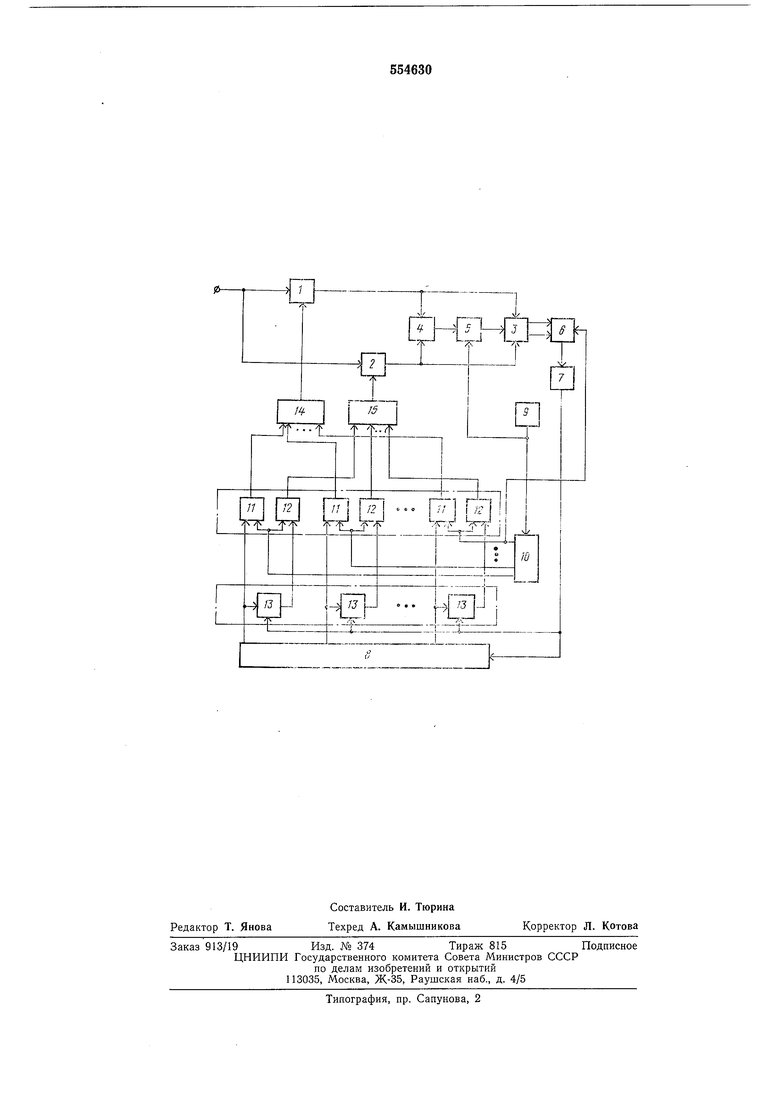

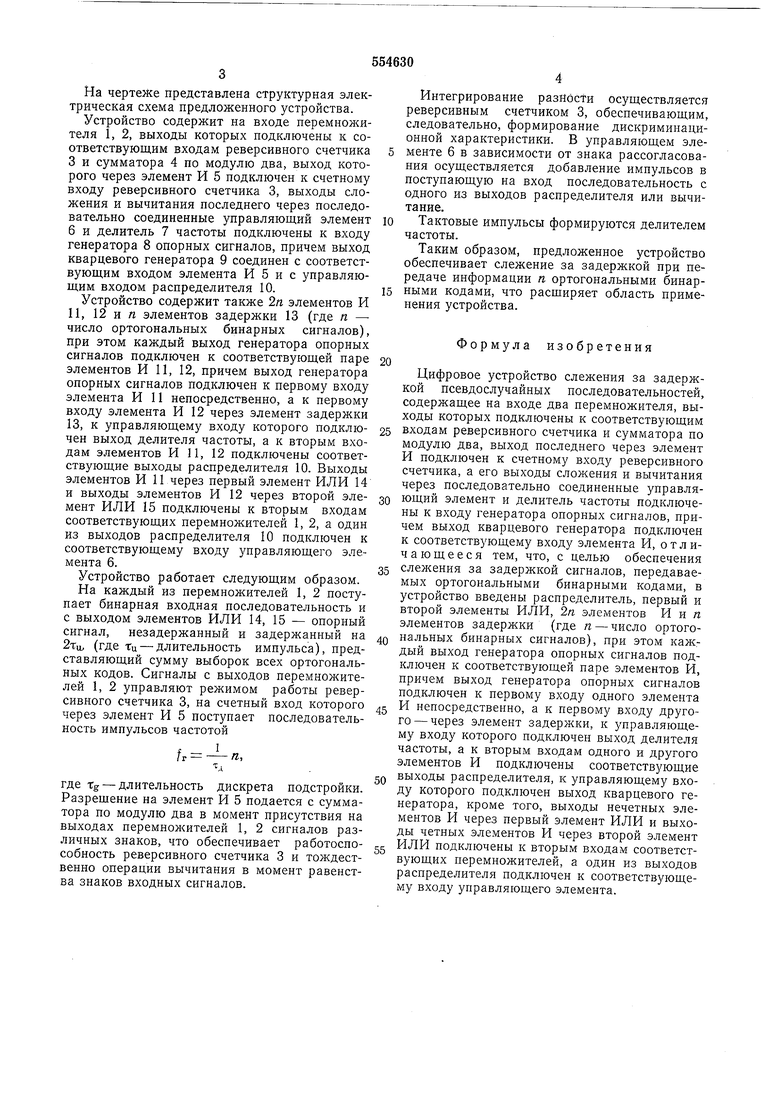

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство содержит на входе перемножителя 1, 2, выходы которых подключены к соответствующим входам реверсивного счетчика 3 и сумматора 4 по модулю два, выход которого через элемент И 5 подключен к счетному входу реверсивного счетчика 3, выходы сложения и вычитания последнего через последовательно соединенные управляющий элемент 6 и делитель 7 частоты подключены к входу генератора 8 опорных сигналов, причем выход кварцевого генератора 9 соединен с соответствующим входом элемента И 5 п с управляющим входом распределителя 10.

Устройство содержит также 2л элементов И 11, 12 и л элементов задержки 13 (где п - число ортогональных бинарных сигналов), при этом каждый выход генератора опорных сигналов подключен к соответствующей паре элементов И 11, 12, причем выход генератора опорных сигналов подключен к первому входу элемента И 11 непосредственно, а к первому входу элемента И 12 через элемент задержки 13, к управляющему входу которого подключен выход делителя частоты, а к вторым входам элементов И П, 12 подключены соответствующие выходы распределителя 10. Выходы элементов И И через первый элемент ИЛИ 14 и выходы элементов И 12 через второй элемент ИЛИ 15 подключены к вторым входам соответствующих перемножителей 1, 2, а один из выходов распределителя 10 подключен к соответствующему входу управляющего элемента 6.

Устройство работает следующим образом.

На каждый из перемножителей 1, 2 поступает бинарная входная последовательность и с выходом элементов ИЛИ 14, 15 - опорный сигнал, незадержанный и задержанный на 2ти, (где Тц - длительность импульса), представляющий сумму выборок всех ортогональных кодов. Сигналы с выходов перемножителей 1, 2 управляют режимом работы реверсивного счетчика 3, на счетный вход которого через элемент И 5 поступает последовательность импульсов частотой

I

fr

п.

где Tg - длительность дискрета подстройки. Разрешение на элемент И 5 подается с сумматора по модулю два в момент присутствия на выходах перемножителей 1, 2 сигналов различных знаков, что обеспечивает работоспособность реверсивного счетчика 3 и тождественно операции вычитания в момент равенства знаков входных сигналов.

Интегрирование разйОсти осуществляется реверсивным счетчиком 3, обеспечивающим, следовательно, формирование дискриминационной характеристики. В управляющем элементе 6 в зависимости от знака рассогласования осуществляется добавление импульсов в поступающую на вход последовательность с одного из выходов распределителя или вычитание.

Тактовые импульсы формируются делителем частоты.

Таким образом, предложенное устройство обеспечивает слежение за задержкой при передаче информации п ортогональными бинарными кодами, что расширяет область применения устройства.

Формула изобретения

Цифровое устройство слежения за задержкой псевдослучайных последовательностей, содержащее на входе два перемножителя, выходы которых подключены к соответствующим

входам реверсивного счетчика и сумматора по модулю два, выход последнего через элемент И подключен к счетному входу реверсивного счетчика, а его выходы сложения и вычитания через последовательно соединенные управляющий элемент и делитель частоты подключены к входу генератора опорных сигналов, причем выход кварцевого генератора подключен к соответствующему входу элемента И, отличающееся тем, что, с целью обеспечения

слежения за задержкой сигналов, передаваемых ортогональными бинарными кодами, в устройство введены распределитель, первый и второй элементы ИЛИ, 2п элементов И и л элементов задержки (где л - число ортогональных бинарных сигналов), при этом каждый выход генератора опорных сигналов подключен к соответствующей паре элементов И, причем выход генератора опорных сигналов подключен к первому входу одного элемента

И непосредственно, а к первому входу другого - через элемент задержки, к управляющему входу которого подключен выход делителя частоты, а к вторым входам одного и другого элементов И подключены соответствующие

выходы распределителя, к управляющему входу которого подключен выход кварцевого генератора, кроме того, выходы нечетных элементов И через первый элемент ИЛИ и выходы четных элементов И через второй элемент

ИЛИ подключены к вторым входам соответствующих перемножителей, а один из выходов распределителя подключен к соответствующему входу управляющего элемента.

m Г7| «.« Г77 nrni i:O2:.jp4yj|X

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство слежения за задержкой псевдослучайной последовательности | 1983 |

|

SU1088146A1 |

| Цифровое устройство слежения за задержкой | 1973 |

|

SU467489A1 |

| Цифровое устройство слежения за задержкой | 1975 |

|

SU555553A2 |

| Устройство слежения за задержкой | 1978 |

|

SU849520A1 |

| Цифровое устройство для слежения за задержкой псевдослучайной последовательности | 1978 |

|

SU999172A1 |

| Цифровое устройство слежения за задержкой | 1975 |

|

SU543184A2 |

| Цифровое устройство слежения за задержкой | 1977 |

|

SU711696A2 |

| Устройство слежения за задержкой шумоподобных сигналов | 1978 |

|

SU966926A1 |

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1978 |

|

SU726671A1 |

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1983 |

|

SU1131034A2 |

Авторы

Даты

1977-04-15—Публикация

1975-04-21—Подача