1

Изобретение относится к области электросвязи, а именно к устройствам измерительной аппаратуры в области связи и может быть использовано для оценки качества передачи данных в каналах тональной частоты.

Известно устройство для автоматического определения коэффициента ошибок, содержащее последовательно соединенные фазирующий блок, датчик эталонного сигнала, схему сравнения, на второй вход которой поданы входные сигналы, счетные декады, выходы разрядов которых соединены с индикатором, а выходы пяти старщих разрядов каждой счетной декады, кроме первой, подключены через элемент ИЛИ к соответствующей схеме округления, второй вход которой подключен к одному из выходов счетчика времени, к входу которого подключен фазирующий блок, и схемы переноса, к одному из входов каждой из которых подключен выход соответствующей счетной декады 1.

Однако в известном устройстве необходимо вводить специальные схемы переключения входов индикатора при сеансах измерения коэффициента ощибок различной длительности. Кроме того, для увеличения точности измерения коэффициента ошибок на каждый вновь вводимый разряд требуется свой индикатор, что приводит к значительному усложнению схемы и понижению надежности устройства.

Целью изобретения является повыщение надежности за счет упрощения устройства.

Для этого в устройство для автоматического определения коэффициента ощибок, содержащее иоследовательно соединенные фазирующий блок, датчик эталонного сигнала, схему сравнения, на второй вход которой поданы входные сигналы, счетные декады, выходы разрядов которых соединены с индикатором, а выходы пяти старших разрядов каждой счетной декады, кроме первой, подключены через элемент ИЛИ к соответствующей схеме округления, второй вход которой подключен к одному из выходов счетчика времени, к входу которого подключен фазирующий блок, и схемы переноса, к одному из входов каждой из которых подключен выход соответствующей счетной декады, введены элементы И, дополнительные элементы ИЛИ по числу счетных декад, реверсивный счетчик и распределитель, при этом между выходом схемы сравнения и входом каждой счетной

декады включены последовательно соединенные элемент И, к двум другим входам которых и к одному входу элемента И первой счетной декады подключены соответствующие выходы распределителя, и дополнительный

элемент ИЛИ, к другим входам которого

подключены выходы соответствующих схем переноса и окрзгления соответственно, а дополнительный выход счетчика времени подключен к одному из входов реверсивного счетчика, другой вход которого соединен с входом первого разряда и с выходом старшего разряда первой счетной декады и с входом распределителя.

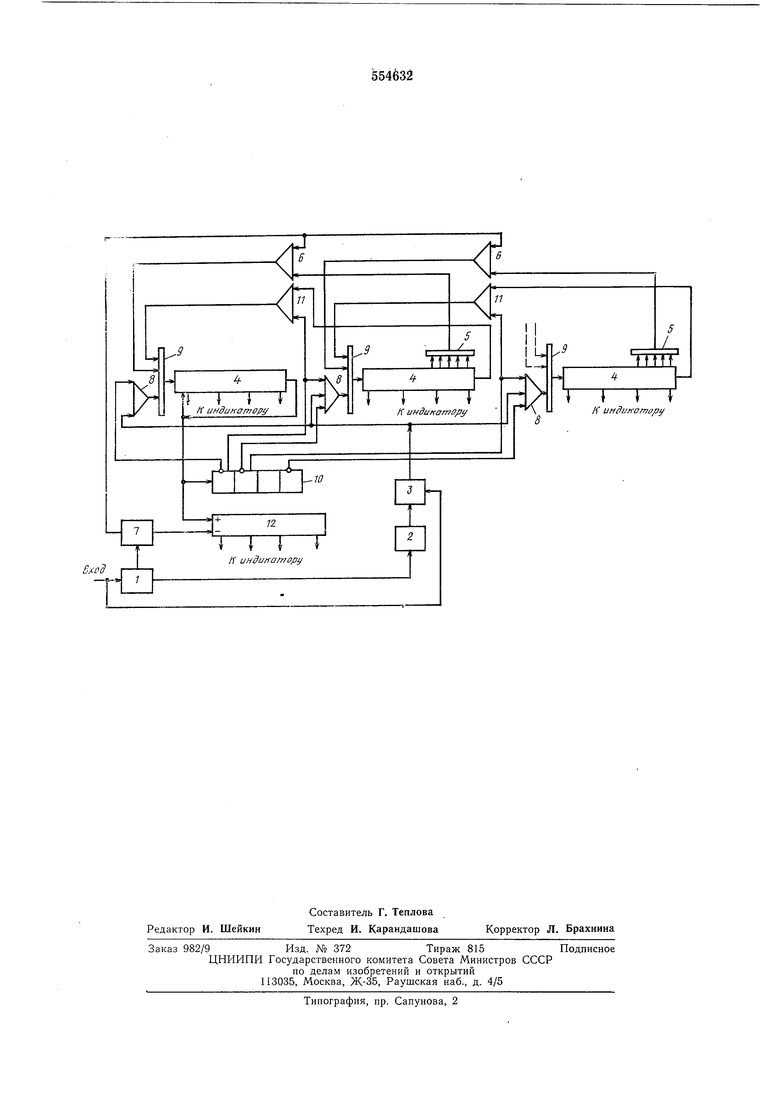

На чертеже приведена структурная электрическая схема описываемого устройства.

Устройство содержит последовательно соединенные фазирующий блок 1, датчик 2 эталонного сигнала и схему сравнения 3, второй вход которой и вход фазирующего блока 1 соединены с входом устройства, счетные декады 4, выходы разрядов которых соединены с индикатором (на чертеже не показанным), а выходы пяти старщих разрядов каждой счетной декады 4, кроме первой, подключены через элемент ИЛИ 5 к соответствующей схеме округления 6, к другим входам которых подключен один из выходов счетчика времени 7, к входу которого подключен фазирующий блок 1. Между выходом схемы сравнения 3 и входом каждой счетной декады 4 включены последовательно соединенные элемент И 8 и дополнительный элемент ИЛИ 9, при этом к двум другим входам элементов И 8, кроме элемента И 8 первой счетной декады 4, и к одному входу элемента И 8 первой счетной декады 4 подключены соответствующие выходы распределителя 10, к другим входам дополнительных элементов ИЛИ 9 подключены выходы соответствующих схем переноса 11 и схем округления 6 соответственно, а дополнительный выход счетчика времени 7 подключен к одному из входов (вычитающему входу) реверсивного счетчика 12, другой вход (суммирующий) которого соединен с входом первого разряда и выходом старшего разряда первой счетной декады 4 и с входом распределителя 10. Выходы реверсивного счетчика 12 подключены к упомянутому индикатору. Одни из входов схем переноса 11 соединены с выходами старших разрядов соответствующих счетных декад 4, кроме первой, другие входы - с соответствующими выходами распределителя 10.

Устройство работает следующим образом.

В начале сеанса измерения коэффипиента ошибок все счетные декады 4 и реверсивный счетчик 12 обнуляются, а расиределитель 10 устанавливается в такое состояние, что с его первого разрядного ииверсного выхода поступает разрешающий сигнал на вход первого элемента И 8.

Сигналы информации из капала связи поступают на вход устройства и далее в фазирующий блок 1, который выделяет из приходящей информации синхросигналы, осуществляющие запуск датчика 2 и счетчика времени 7.

Схема сравнения 3 производит поразрядное сравнение входных сигналов информации с эталонными сигналами, поступающими от

датчика 2, и формирует сигналы ощибок, которые поступают в счетные декады 4 через элементы И 8 и ИЛИ 9. Так как в начале измерения разрешающий сигнал с инверсного выхода распределителя 10 поступает только на первый элемент И 8, то счет количества ошибок осуществляет первая счетная декада 4.

Если число ошибок за сеанс измерения превысит десять, то импульсом с выхода первой счетной декады 4 осуществляется запись единицы в первый разряд первой счетной декады 4, распределителя 10 и реверсивного счетчика 12 по суммирующему входу.

После записи единицы в распределитель 10 с его инверсного выхода первого разряда прекращает поступать сигнал разрешения на первый элемент И 8 и начинают поступать сигналы разрешения с прямого выхода первого разряда и с инверсного выхода второго разряда на второй элемент И 8. В это же время сигналом с прямого выхода первого разряда распределителя 10 подготавливается к работе первая схема переноса И.

Таким образом, если количество ощибок превысило десять, то сигналы ощибок от схемы сравнения 3 поступают на вторую счетную декаду 4 через соответствующие элементы И 8 и ИЛИ 9.

После каждых последующих десяти сигналов ошибок с выхода второй счетной декады 4 через соответствующие схему переноса 11 и эле.мент ИЛИ 9 поступают сигналы на вход первой счетной декады 4. Следовательно, в первой счетной декаде 4 всегда формируется старший разряд множителя, его целая часть.

В случае, если число ошибок иревысит 100, то вторым имиульсом со старшего разряда первой счетной декады 4 вновь запишется единица в ее первый разряд и улсе во второй разряд распределителя 10, а также в реверсивный счетчик 12. Запись единицы во втором разряде распределителя 10 приводит к тому, что закрывается второй и открывается следующий элементы И 8 и подготавливается к работе вторая схема переноса 11.

Таким образом, при увеличеиии числа ошибок на иорядок увеличивается число разрядов распределителя 10, устанавливаемых в едииичное состояние, а в реверсивном счетчике 12 но суммирующему входу каждый раз добавляется единица.

В случае, если число ошибок превысит 100, встуиает в работу третья счетная декада 4. Счетные декады 4, начиная с второй, формируют дробную часть множителя, выраженную в десятичной форме. Так вторая счетная декада 4 формирует десятичные доли множителя, третья - сотые.

Из счетчика времени 7 на вычитаюший вход реверсивного счетчика 12 поступают импульсы каждый раз, когда число проанализированных элементов поступающей информации увеличивается на порядок. Таким образом, в реверсивном счетчике 12 формируется показатель десятичной степени. Число разрядов реверсивного счетчика 12 зависит от длительности сеанса измерения коэффициента ошибок.

Число счетных декад 4 зависит от длительности сеанса измерения, диапазона измерения множителя коэффициента ошибок и определяет точность его измерения.

Все разряды множителя выводятся с соответствующих счетных декад 4 на соответствующие разряды индикатора.

Для округления результатов измерения в устройстве предусмотрены элементы ИЛИ 5 и схемы округления 6, на входы которых поступает сигнал от счетчика времени 7, разрешающий округление результата измерения в конце сеанса.

Округление происходит тогда, когда есть единица в одном из последних пяти разрядов счетной декады 4, начиная с второй. Сигналы с этих разрядов через определенные элементы ИЛИ 5 поступают на другие входы соответствующих схем округления 6.

Таким образом, устройство позволяет измерять коэффициент ошибок с высокой точностью при сеансах связи различной длительности.

Формула изобретения

Устройство для автоматического определения коэффициента ошибок, содержащее последовательно соединенные фазирующий блок, датчик эталонного сигнала, схему сравнения, на второй вход которой поданы входные сигналы, счетные декады, выходы разрядов которых соединены с индикатором, а выходы пяти старших разрядов каждой счетной декады, кроме первой, подключены через элемент ИЛИ к соответствующей схеме округления, второй вход которой подключен к одному из выходов счетчика времени, к входу которого подключен фазирующий блок, и схемы переноса, к одному из входов каждой

из которых подключен выход соответствующей счетной декады, отличающееся тем, что, с целью повышения надежности за счет упрощения устройства, введены элементы И, дополнительные элементы ИЛИ по числу

счетных декад, реверсивный счетчик и распределитель, при этом между выходол схемы сравнения и входом каждой счетной декады включены последовательно соединенные элемент И к двум другим входам которых и к

одному входу элемента И первой счетной декады подключены соответствующие выходы распределителя, и дополнительный элемент ИЛИ, к другим входам которого подключены выходы соответствующих схем переноса и округления соответственно, а дополнительный выход счетчика времени подключен к одному из входов реверсивного счетчика, другой вход которого соединен с входом первого разряда и с выходом старшего разряда первой счетной декады и с входом распределителя.

Источники информации, принятые во внимание при экспертизе.

1. Авторское свидетельство СССР № 351334, М. кл. Н 04 11/08, 1970 (прототип).

J

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНАЯ ?11ДШТЙО-ТЕХ!?И=]ЕСНД?| БИБЛИОТ^К.А I | 1972 |

|

SU351334A1 |

| Устройство для измерения коэффициента ошибок | 1974 |

|

SU543187A1 |

| Устройство для приема трехкратноповторенных команд телеуправления | 1977 |

|

SU720775A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство для автоматического определения коэффициента ошибок | 1974 |

|

SU518009A1 |

| Устройство для измерения коэффициента ошибок | 1988 |

|

SU1518893A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Устройство цифровой индикации положения сосуда шахтной подъемной машины | 1989 |

|

SU1745659A1 |

| Устройство для цифровой индикации | 1979 |

|

SU903961A1 |

77 1f 1 I /Y индикатуру T-п /г UrtduffO/nOpy

77 тптт 11 i II /г индикатору TUTt } I г utidutfomopy

Авторы

Даты

1977-04-15—Публикация

1974-12-04—Подача