Изобретение относится к телеграфии и передаче данных и может использоваться для оценки качества передачи дискретной информации в каналах тональной частоты.

Известно устройство для измерения коэффициента ошибок, содержащее последовательно соединенные фазирующий блок, датчик эталонных сигналов и блок сравнения, на второй вход которого и вход фазирующего блока подан анализируемый сигнал, а также датчик времени и цифровые индикаторы 1.

Однако известное устройство обладает недостаточно высокой точностью измерения.

С целью повышения точности измерения коэффициента ошибок в предлагаемое устройство для измерения коэффициента ошибок введены делитель с неременным коэффициентом деления, распределитель, ключевой блок н регистр сдвига, нри этом выходы блока сравнения и датчика времени подключены к входам первого цифрового индикатора через ключевой блок, делитель с переменным коэффициентом деления и регистр сдвига, выход последнего разряда которого подключен к своему входу «записи, к входу «начальной установки делителя с переменным коэффициентом деления непосредственно, а к входам второго цифрового индикатора - через распределитель, выходы которого подключены к управляющим входам делителя с переменным коэф2

фициентом Деления, дополнительный выход которого подключен к входу «записп единицы в первый элемент распределителя, причем дополнительный управляющий вход делителя с переменным коэфф щиентом деления подключен к первому разряду регистра сдвига.

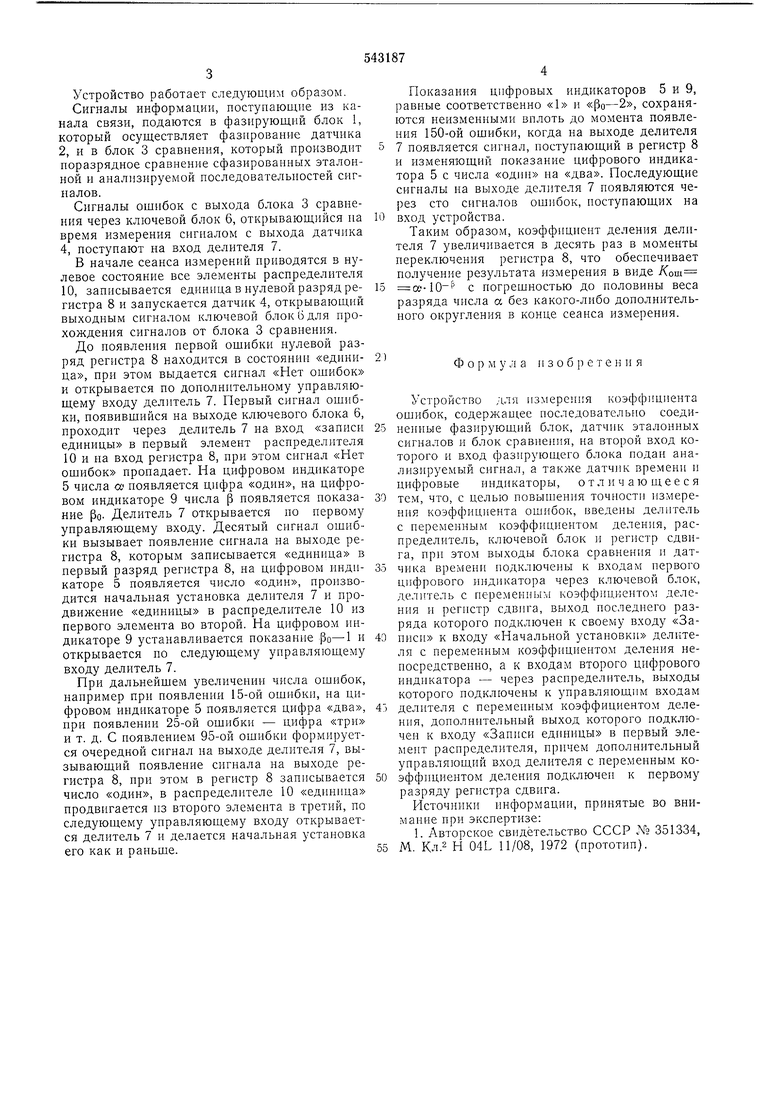

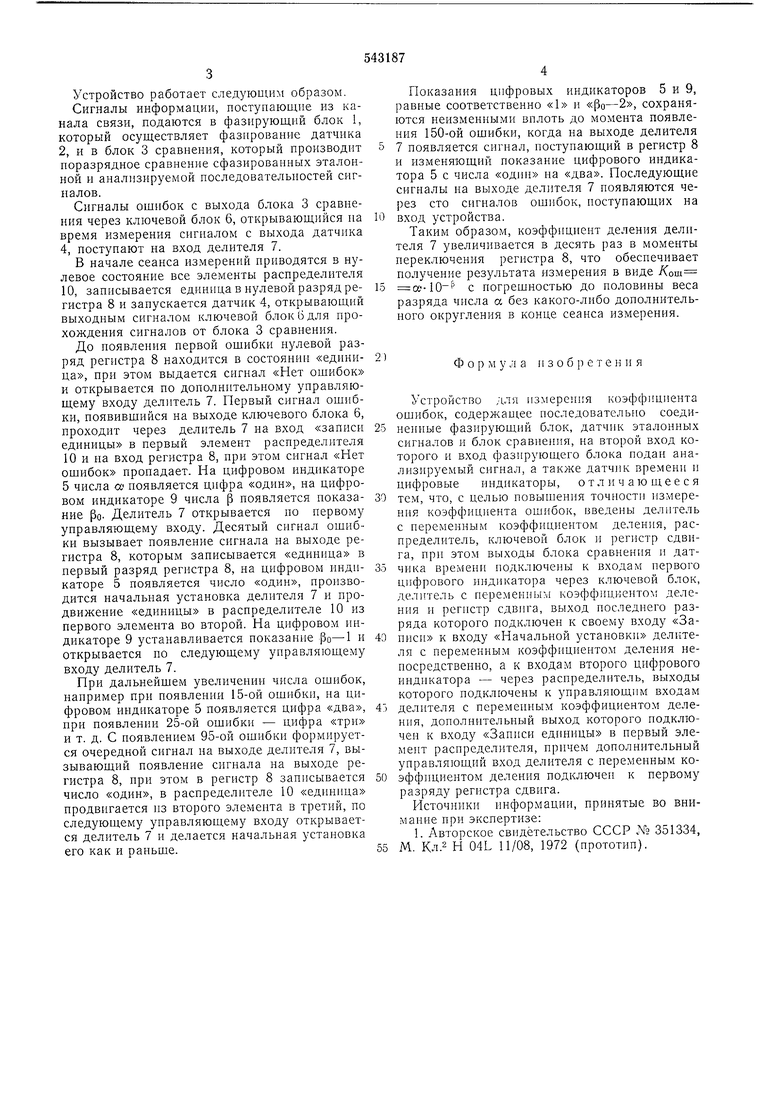

На чертеже приведена структурная электрпческая схема предложенного зстройства.

Устройство для измерения коэффициента ошибок содержит последовательно соединенные фазирующий блок 1, датчик 2 эталонных сигналов и блок 3 сравнения, второй вход которого и вход фазирующего блока 1 соедннены с входом устройства, датчик 4 времени, причем выходы блока 3 сравнения и датчика 4 подключены к входам первого цифрового индикатора 5 через ключевой блок 6, делитель 7 с переменным коэффициентом деления и регистр 8 сдвига, выход последнего разряда которого подключен к своему входу «Записи, к входу «Начальной установки делителя 7 непосредственно, а к входам второго цифрового индикатора 9 - через распределитель 10,

его выходы подключены к управляющим входам делителя 7, дополпптельный выход последпего подключен к входу «Записи единицы в первый элемент распределителя 10, причем дополнительный управляющий вход делителя

7 подключен к первому разряду регистра 8.

Устройство работает следуюпи-ш образом.

Сигналы информации, постуиающне из канала связи, подаются в фазирующий блок 1, который осуществляет фазирование датчика 2, и в блок 3 сравнения, который ироизводит иоразрядиое сравнение сфазироваиных эталонной н анализируемой носледовательиостей сигналов.

Сигналы ощибок с выхода блока 3 сравнения через ключевой блок 6, открывающийся на время измерения сигиалом с выхода датчика 4, иоступают на вход делителя 7.

В начале сеанса измерений ириводятся в нулевое состояние все элементы распределителя 10, записывается единица в нулевой разряд регистра 8 и запускается датчик 4, открывающий выходным сигналом ключевой блок 6 для прохождения сигналов от блока 3 сравнения.

До появлеиия первой ошибки нулевой разряд регистра 8 находится в состоянии «единица, при этом выдается сигнал «Нет ощибок и открывается по дополнительиому управляющему входу делитель 7. Первый сигнал ошибки, появившийся на выходе ключевого блока 6, проходит через делитель 7 на вход «записи единицы в первый элемент распределителя 10 и на вход регистра 8, при этом сигиал «Нет ошибок пропадает. На цифровом индикаторе 5 числа а появляется цифра «один, на цифровом индикаторе 9 числа р появляется показание Ро Делитель 7 открывается по первому управляющему входу. Десятый сигнал ошибки вызывает появление сигнала на выходе регистра 8, которым записывается «едииица в первый разряд регистра 8, на цифровом индикаторе 5 появляется число «один, производится начальная установка делителя 7 и продвижение «единицы в распределителе 10 из первого элемента во второй. На цифровом иидикаторе 9 устанавливается показание |3о-1 и открывается ио следующему управляющему входу делитель 7.

При дальнейшем увеличении числа ошибок, например ири появлении 15-ой ошибки, па цифровом индикаторе 5 появляется цифра «два, при появлении 25-ой ошибки - цифра «три и т. д. С иоявлеиием 95-ой ошибки формируется очередной сигнал на выходе делителя 7, вызывающий появление сигнала на выходе регистра 8, при этом в регистр 8 записывается число «одии, в распределителе 10 «едииица продвигается из второго элемента в третий, по следующему управляющему входу открывается делитель 7 и делается начальиая устаиовка его как и раньше.

Показания цифровых индикаторов 5 и 9, равные соответственно «1 и «ро-2, сохраняются неизменными вплоть до момента появлеиия 150-ой ошибки, когда на выходе делителя 7 появляется сигнал, иоступающий в регистр 8 и изменяющий показание цифрового индикатора 5 с числа «один на «два. Последующие сигиалы на выходе дел 1теля 7 появляются через сто сигналов ошибок, поступающих на

вход устройства.

Таким образом, коэффициент деления делителя 7 увеличивается в десять раз в моменты переключения регистра 8, что обеспечивает получение результата измерения в виде Кот

а-10 с погрешностью до половины веса разряда чпсла а без какого-либо дополнительного округления в конце сеанса измерения.

Форм у л а и 3 о б ji е т е н и я

Устройство для измерения коэффициента ошибок, содержаи1,ее последовательно соединенные фазирующий блок, датчик эталонных сигналов и блок сравнения, на второй вход которого и вход фазпруюшего блока подан анализируемый сигнал, а также датчик времени и цифровые индикаторы, от л и ч аю ил,е е с я

тем, что, с целью повышения точности измерения коэффициента ошибок, введены делитель с иеременным коэффнциентом деления, распределитель, ключевой блок н регистр сдвига, при этом выходы блока сравнения и датчика времеии подключены к входам первого цифрового индикатора через ключевой блок, делитель с иеременным коэфф и:,иептом деления н регистр сдвига, выход иоследиего разряда которого подключен к своему входу «Записп к входу «Начальиой устаиовки делителя с переменным коэффициентом деления непосредственно, а к входам второго цифрового индикатора - через распределитель, выходы которого подключены к управляющим входам

делителя с перемепным коэффициентом деления, дополнительный выход которого подключен к входу «Записи единицы в иервый элемент распределителя, причем дополнительный управляюший вход делителя с переменным коэффпциентом деления подключеп к первому разряду регистра сдвига.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидёте.тьство СССР Х- 351334,

М. Кл.2 Н 04L 11/08, 1972 (прототип).

ВхоЗ

o

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ УСТОЙЧИВОСТИ ФАЗИРУЮЩИХ УСТРОЙСТВ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ | 1968 |

|

SU211151A1 |

| Приемное устройство цикловой синхронизации | 1976 |

|

SU578670A1 |

| Устройство для оценки достоверности принимаемой информации | 1985 |

|

SU1251153A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Устройство для контроля качества канала связи | 1979 |

|

SU856023A1 |

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1984 |

|

SU1185617A2 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1982 |

|

SU1016845A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

Авторы

Даты

1977-01-15—Публикация

1974-07-08—Подача