Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей в системах управления и в устройствгис считывания rpai-i фической информации.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий группу элементов И, входа котогялх соединены с инфррмацйонншга входами преобразователя, блок опроса, десятичный счетчик, состоящий из декад и последовательно соединенных с ними элементов задержки, регистр двоичного кода, шифратсф, группу элементов или, делитель, триггер и элемент И .1 .

Недостаток преобразователя сосхоит в низком быстродействии, связан ном с последовательной обработкой двоичных разрядов и -отсутствием учета нулевых значений двоичных разрядов.

Наиболее близким к предлагаемо по технической сущности является преобразователь, содержащий группу элементов И, первые входы которых соединены с информационнюш входами преобразователя, блок опроса, первый вход которого сочинен с входом пуска преобразователя, десятичшлй счетчик, включающий К декад и группу . из (()-ro элемента задержки, причем выходы переполнения декад кроме К-й соединены с входом соответствующего элемента задержки регистр двоичного кода, шифратор, первую группу элементов ИЛИ, информационные входы которых соединены с выходами

to шифратора, вьссод i-ro элемента задержки соединен с дополнительным входом (i-fl)-ro элемента ИЛИ первой группы, формирователь последовательности икшульсов 2.

15

Недостаток, преобразователя состоит в относительно низком быстродействии, связанном с использованием десяти импульсов для каждого, цикла шифрования группы одновременно опра20шиваемых разрядов двоичного кода.

Цель изобретения - првьй11ение быстродействия преобразователя.

Поставленнгш цель; достигается тем, что в преобразователь двоичного ко25 да в дво1|чно-десятичный, содержащий первую группу элементов И, распределитель импульсов, десятичный счетчик, включающий К декад « первую группу из {К-1)-го элел4ента задержки.

30

где К - число десятичных разрядов

преобразуемого кода, регистр двоичного кода, шифратор, первую группу элементов ИЛИ, формирователь последовательности импульсов, тактовый вход которого соединен с тактовым выходом распределителя импульсов, выход сброса которого соединен с тактовым входом регистра двоичного кода и с входом сброса формирователя последовательности импульсов, тактовый выход которого соединен с тактовым входом шифратора информационный вход которого соединен с выходом регистра двоичного кода и с первым информационным входом распределителя импульсов, второй информационный вход которого соединен с вх дом нуля преобразователя, информационные входы которого соединены .с первыми входами элементов И первой группы, первая группа выходов которой соединена с информационными входами первой декады десятичного счетчика, а вторая группа выходов соединена с информационными входами регистра двоичного кода, вход опрос шифратора соединен с выходом опроса распределителя импульсов, первый вход которого соединен с вторыми вхдами всех элементов И первой группы и с входом пуска преобразователя, выходы которого являются выходами десятичного счетчика, выходы переполнения 1-декады которого (1 1-К-1)-й через соответствующие элементы задержки первой группы соединены с первыми входами ( i 1 ) элементов ИЛИ первой группы, остальные входы которых соединены с первой группой выходов шифратора, вхол переключени распределителя импульсов соединен с выходом переполнения формирователя последовательности импульсов, введены блок управления, вторая группа элементов И, а десятичный счетчик выполнен реверсивным и содержит вторую группу элементов задержки, вход 1-го элемента которой соединен с выходом заема 1-й декады десятичного с,четчика, а выход 1-го элемент задержки второй группы соединен с первым входом ()-го элемента ИЛИ второй группы, остальные входы элементов ИЛИ второй группы соединены соответственно с второй группой выходов шифратора, третья группа выходов которого соединена с информационным входом блока управления, тактовый вход которого соединен с тактовым выходом блока опроса, выхо сброса которого соединен с входом сброса блока управления, вход пуска которого соединен с входом пуска преобразователя, первый установочны и разрешанвдйй выходы блока управления соединены соответственно с входами установки в нуль и входакга раз решения установки всех декад десятичного счетчика, входы сложения и вычитания которого соединены соответственно с выходами первой и второй групп элементов ИЛИ, второй установочный выход блока управления соединен с установочным входом шифра тора.

Блок управления содержит элемент И-НЕ, элемент И, первый и второй элементы ИЛИ, четыре элемента НЕ, элемент дифференцирования, элемент задержки и триггер, S-вход которого через элемент дифференцирования соединен с выходом первого элемента ИЛИ, входы которого являются информационными входами .блока управления, первый и второй установочные выходы которого соединены соответственно с выходами второго элемента ИЛИ и элемента И выход которого через элемент задержки соединен с R-входом триггера, выход которого соединен с первым входом элемента И, второй вход которого является входом сброса, блок управления, вход пуска которого чере первый элемент НЕ соединен с первым входом элемента И-НЕ, второй вход которого через второй элемент НЕ соединен с выходом второго элемента ИЛИ, первый вход которого через ключ и третий элемент НЕ соединен с входом нуля, второй вход второго элемента ИЛИ является тактовыги входом блока управления, разрешающий выход которого через четвертый элемент НЕ соединен с выходом элемента И-НЕ.

Формирователь последовательностей импульсов содержит дешифратор, группу элементов ИЛИ и- счетчик, включающий два элемента И и три триггера, входы сброса которых соединены с сброса формирователя последовательностей импульсов, тактовый вход которого соединен со счетным входом триггера первого разряда счетчика, первьгм входом первого элемента И и тактовым входом дешифратора, информационные входы которого соединены с выходами счетчика, прямой и инверсный выходы триггера второго разряда которого соединены соответственно со счетным входом триггера третьего разряда счетчика и вторым входом первого элемента И, третий вход которого соединен с прямым выходом триггера третьего разряда счетчика, являющегося выходом переполнения формирователя последовательности импульсов, информационные выходы которог соединены с выходами элементов ИЛИ группы, выход первого элемента И соединен с управ ляющим входом триггера третьего разряда счетчика, инверсный выход которого соединен с первым входом второго элемента И, второй вход которого соединен с прямым выходом

триггера первого разряда счетчика, а выход второго элемента И соединён со счетным входом триггера второго разряда счетчика, j-й (j«l-5) выход дешифратора соединен с входами с j-го попятый элементов ИЛИ группы.

На фиг. 1 представлена блок-схема предлагаемого прео«5раэователя; на фиг. 2 и 3 - функциональная схема шифратора; на фиг. 4 - функциональная схема формирователя последовательности импульсов

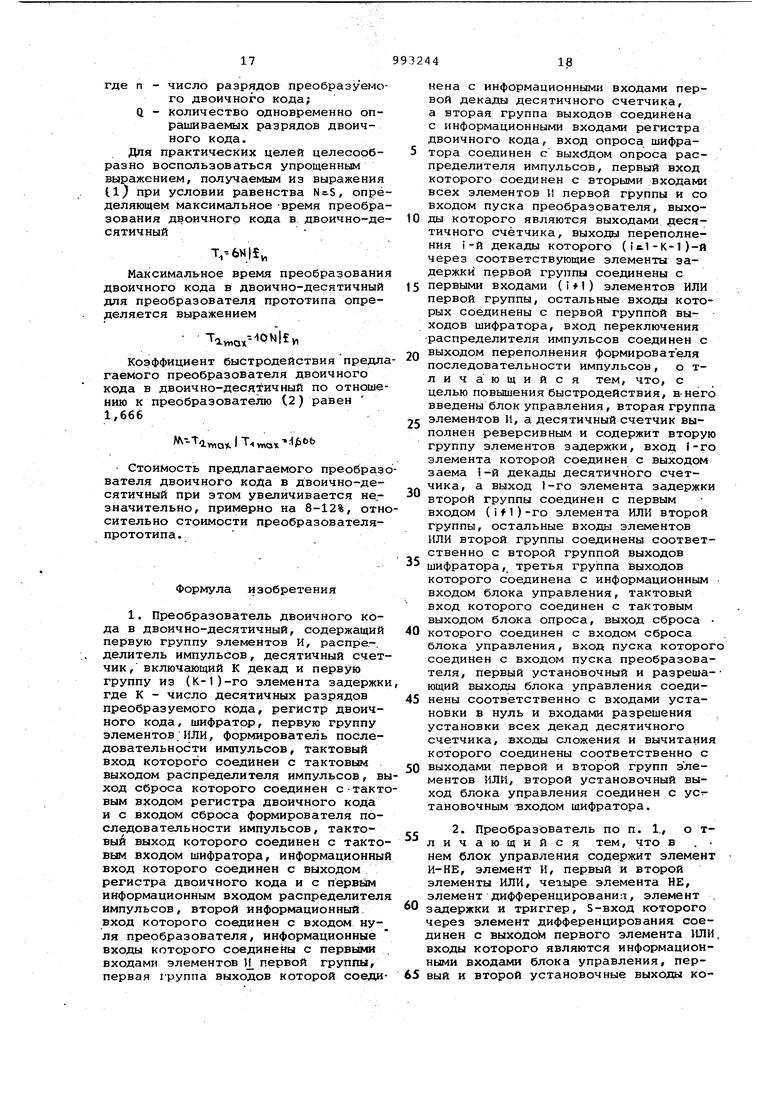

Преобразователь двоичного кода в лвоично-десйтичный содержит группу 1 элементов И, входы которых подключены к информационньоч входам 2. преобразователя, распределитель 3 импульсЪв, пoдкJiючeнный к входу 4 пуска преобразователя, шифратор 5, десятичный счетчик 6, включающий сченые декады 7( -7, первую и вторую группы элементов ((j,) и (.«) задержки, регистр 10. двоичного, кода, формирователь 11 последовательности импульсов, первую группу 12 элементов ИЛИ (j, вторую группу 14 элементов ИЛИ ,; и блок 16 управления, содержащий ключ 17 управления, элементы ИЛИ 18, элемент НЕ 19, элемент И-НЕ 20, элементы НЕ 21-23, элемент ИЛИ 24, элемент 25 Дифференцирования, триггер 26, элемент И 27 и элемент 28, задержки. Шифратор J5 для случая од новременного опроса четырех разрядов регистра 10 двоичного кода (фиг. 2 и 3), содержит элементы И 29-44, первые входы которых подключены к информационному входу М шифратора 5, а вторые/ - к входу опроса U шифратора 5, выходы элементов И 29-44 соединены с соответствующими в ходами элемен тов ИЛИ 45-48, выходца которых соединены соответствующим образом с входами элементов И 49-63, а выходы элементов И 49-63 соединены с входами элементов И 50-63 через элементы НЕ 64-68. Выходы элементов И подключены к выходу .Т шифратора 5. Входы элементов ИЛИ соответствующим образом подключены к выходам элементов И 49-63. Выходы элементов ИЛИ ,4 соответствующим образом соединены с первыми входами элементов И 70 , вторые входы которыхподключены к тактовому входу Д шифратора 5, а третьи - к входу И. опроса шифратора 5. Выходы э,77ементов И И 7 Ксоединены с выходами шифратора.5, подключенными к входам первой группы 12 элементов ИЛИ , . Выходы элементов ИЛИ 71 -71|4% соответствующим образом соединены с первыми вхоДсми элементов И ,,, вторые входи которялх подключены к тактовому входу л шифратора 5, а третьи - к входу и опроса шифратора 5. Выходы

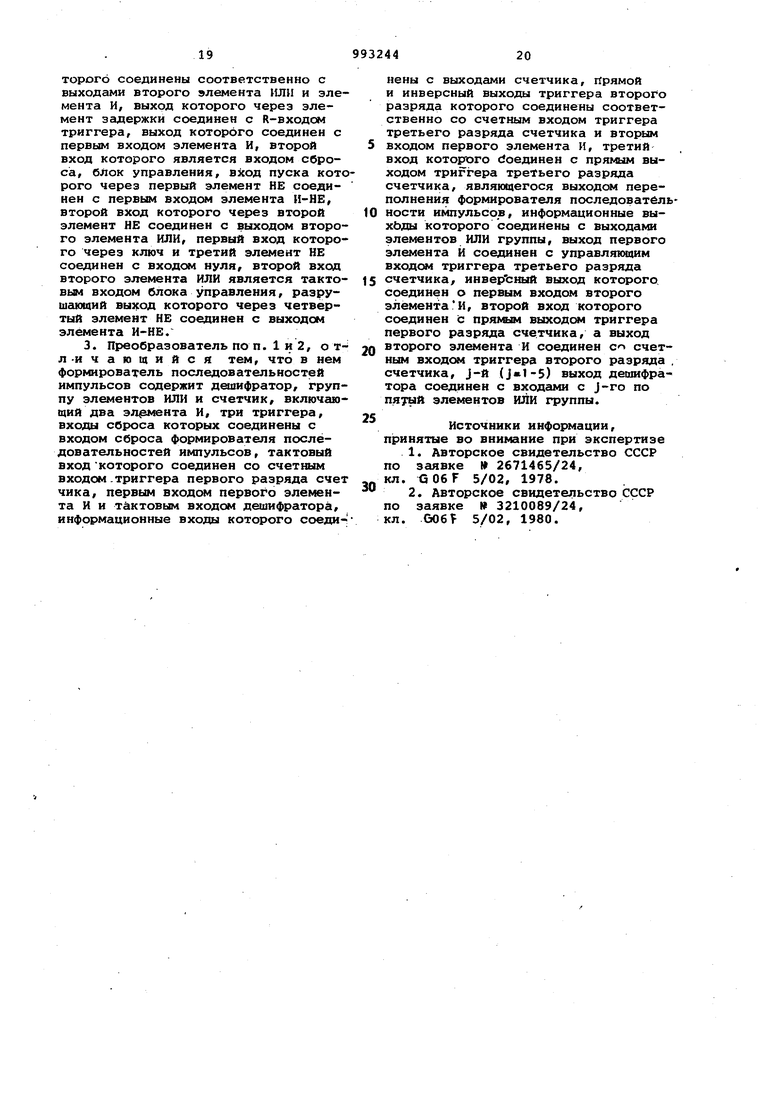

элементов И + 3 соединены с выходами шифратора 5, подключенными к входам второй группы 14 элементов ИЛИ 15 -15ф; . Входы и , и ;ВЫх6Д шифратора 5 соединены с входами блока 73 формирования установочного импульса {фиг. 3). Выходы узла 73 формирования установочного импульса соединены с выходами шифратора 5, подключенными к соответствующим

входам первой группы 12 элементов

ИЛИ 13-1-13,,.

Блок 73 формирования установочного импульса содержит элементы ИЛИ 74 -V7« k)V элементы И ,

элементы ИЛИ 76 -76 , И 77| -77ц Выходы элементов И 77 -77, подключены к соответствующим входам группы 12 элементов 1ШИ 13„-13.

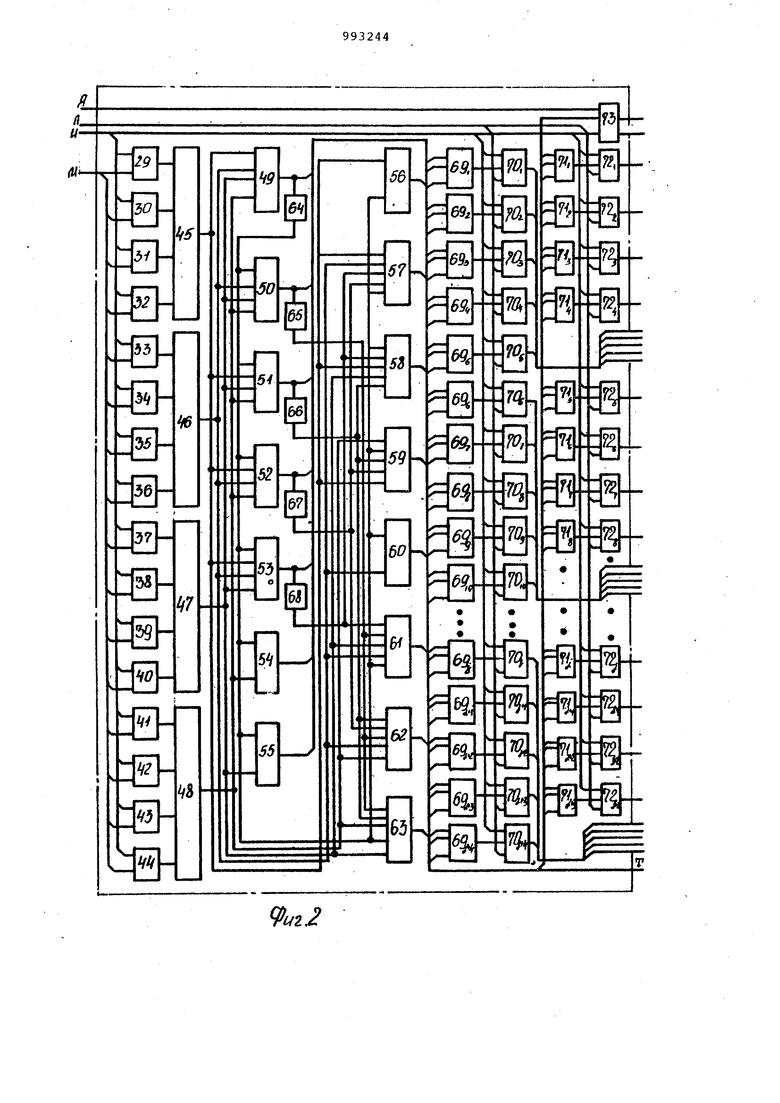

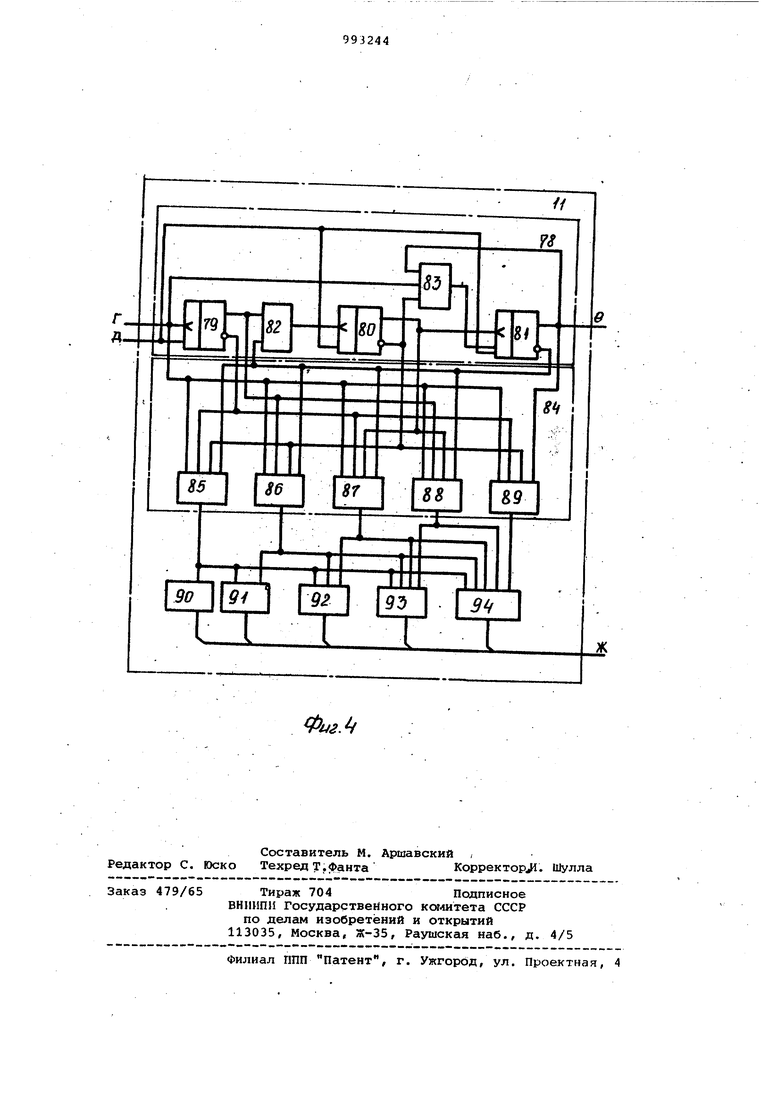

Формирователь 11 последовательности импульсов (фиг. 4) содержит счетчик 78, коэффициент пересчета которого равен шести, выполненный на триггерах 79-81 и двух элементах И 82 и 83, дешифратор 84,:выполненный на элементах И 85-89 группы, : группу элементов ИЛИ 90-94. Вход сброса счетчика 78 подключен к входу ) сброса формирователя 11.

Преобразователь двоичного кода в .

двоично-десятичный работает следую- i щим образом.

Перед началом работы производится начальная установка всех триггеров преобразователя в нулевое состояние

(цепи начальной установки на фиг. 1 не показаны). Установка в нулевое состояние десятичного счетчика 6 производится сигналом Единица, подаваемым на управляющие входы V счетных декад 7( -7 , который поступает с выхода Ш блока 16 управления при нажатии ключа 17 управления, на управляющим входе ю счетных декад 7f -7|, при этом сигнал низкого уровня..

После начальной установки преобразователя на выходе б распределителя импульсов появляется сигнал. С выхода Ь которого первый сигнал опроса поступает на вход И шифратора 5.

При поступлении на вход 4 преобразователя сигнала Пуск, поступающего на первые входы группы 1 элементов И, на вторые входы которых поступают информационные сигналы разря дов 2-2 двоичного кода, информат ция трех младших разрядов 2-2 постуйает на установочные входы ts6, fj и Y счетной декады 7 , осталь

ные разряда двоичного кЬда записывеиотся в регистр 10 двоичного кода. Сигнал Пуск поступает также на вход р блока 16 управления и на вход элетлента НЕ 22, с выхода

которого сигнал низкого уровня

поступает на второй вход элемента И-НЕ 20, на первый вход которого поступает сигнал высокого уровня с выхода элемента НЕ 19. На выходе элемента И-НЕ 20 появляется сигнал высокого уровня, поступающий на вход элемента НЕ 23. Сигнал низкого уровня с выхода элемента НЕ 23 поступает на выход блока 16 управления и далее на управляющие входы ю счетных декад 7, -7 . Наличие сигналов низкого уровня на управляющих входах у и ю счетных декад , десятичного реверсивного счетчика 6 позволяет произвести установку триггеров в состояния, соответствующие сигналам, поданным на установочные входы о{. , р и У первой счетной декады 7 .

Сигналы с прямых и инверсных выходов разрядов регистра 10 двоичного кода поступают на входы а- распределителя 3 импульсов, в котором производится анализ одновременно опрашиваемых, например, четырех разрядов двоичного кода. Если указа нные опрашиваемые разряды двоичного кода находятся в нулевом состоянии, то на выходе -в распределителя 3 импульсов появляется сигнал опроса следующих, например, четырех разрядов двоичного кода. Если хотя бы один из опрашиваемых разрядов двоичного кода находится в единичном состоянии, то сигнал появляется, на выходе t распределителя импульсов и поступает на вход блока 11 формирователя последовательности импульсов и на вход н блока 16 управления.

Тактовые импульсы с выхода Z- распределителя импульсов поступает на вход г. формирователя 11 последовательности импульсов и далее на счетный вход счетчика 78 (фиг. 4 ) и на первые входы элементов И 85- И 89 группы, с помощью которых выделяются все пять состояний счетчика 78. Тактовые . импульсы с выходов элементов И 85-89 поступают на входы пяти элементов ИЛИ 90-94. На первый элемент ИЛИ 90 заводится первое состояние счетчика 78, на второй элемент ИЛИ 91 - первое и второе, на третий элемент ИЛИ 92 - первое, второе и третье и т.д., на пятый элемент ИЛИ 94 - все пять состояний счетчика 78 Тактовые импульсы с выходов элементов ИЛИ 90-94 поступают на выход Ж формирователя 11 последовательности импульсов.

Работа предлагаемого преобразователя основана на параллельном суммировании в счетных декадах 7 -7 десятичг.ого реверсивного счетчика б импульсных последов а т бальное те и, которые соответствуют сумме весов одновременно опрашиваемых и имеющих единичное состояние, например четырех разрядов двоичного кода. Числа 1-5 суммируют обычным путем, а числа 6-9 заменяются соответственно на числа-4-1 в шифраторе 5 и подаются на вычитающий вход Ксоответствующей декады 7, десятичного ревер-, сивного счетчика 6, при этом на суммирующий вход К следующей старшей счетной декады подается установочный импульс с выхода блока 73

0 формирования установочного импульса щи фра тора 5.

Прямые сигналы разрядов 2 -2 двоичного кода поступают с регистра 10 двоичного кода на вход Л шифра5 тора 5. В предлагаемом преобразователе могут использовать и другие шифраторы, например рассчитанные на одновременное шифрование двух, трех, пяти и более разрядов двоично0 го кода.

С выхода АЛ шифратора 5 сигналы поступают на .вторые входы элементов И 29-44, при этом сигналы с прямых выходов первых опрашиваемых, напри5 мер, четырех разрядов двоичного кода поступаю на вторые входы элементов И 29, 33, 37 и 41, на первых входах которых уже присутствует сигнал опроса, поступивший с входа и шифратора 5. Сигналы с выходов элементов И 29, 33, 37 и 41 поступают на первые входы элементов ИЛИ 45-48, с выхода которых сигналы поступают на входы элементов И 49-63, с помощью которых, а также с помощью элементов НЕ 64-68, осуществляется шифрование опрашиваемых разрядов двоичного кода.

Сигналы с выходов элементов И 49-63.поступают на входы элементов

0 ИЛИ 69 на входы элементов ИЛИ Сигналы с выходов

элементов ЪМ , 7 lj) + , поступают соответственно на , первые входы элементов И 7СЦ

5 и 72i-72;j.. вторые входы которых поступают определенные последовательности ИМПУЛЬСОВ с входа л .шифратора 5, а на третьи - сигнал опроса с входа И шифратора 5. Сигналы с вы0 ходов элементов И 70/ i

И 72,j-72/44 I поступают на выходышифратора 5, с выхода которого сигналы соответственно поступают ни вхо- ды первой и второй групп 12 и 14

5 ИЛИ. Сигналы с выходов элементов И 49-63 шифратора 5 поступают также на выход Т шифратора 5 и далее на информационный вход С блока 16 управления.

Q На выходах элементов И . шифратора 5 может появиться лгобая последовательность импульсов от одного до пяти, которая через группу

12 элементов ИЛИ поступает на суммирующий вход счетных декад 7 -7к.

На выходах элементов И .45 может появиться любая последовательность импульсов от одного до четырех которая через группу 14 элементов ИЛИ поступает на вычитающий вход К счетных декад 7 7|с Перед подачей последовательности импульсов на этот вычитающий вход бЛок 73 шифратора 5 осуществляет формирование установочного импульса, подаваемого с выходов шифратора 5 на соответствую ющие входы группы 12 элементов 1ШИ, с выходов которых сигнал поступает на суммирующий вход К счетных де кад о

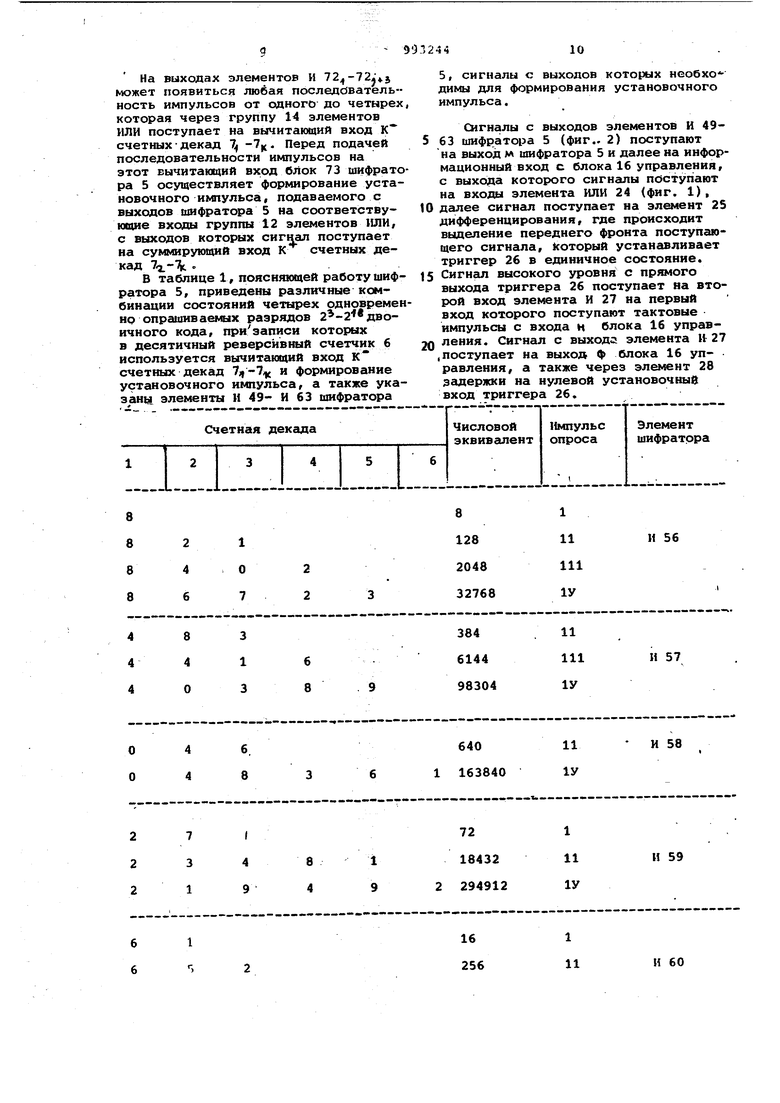

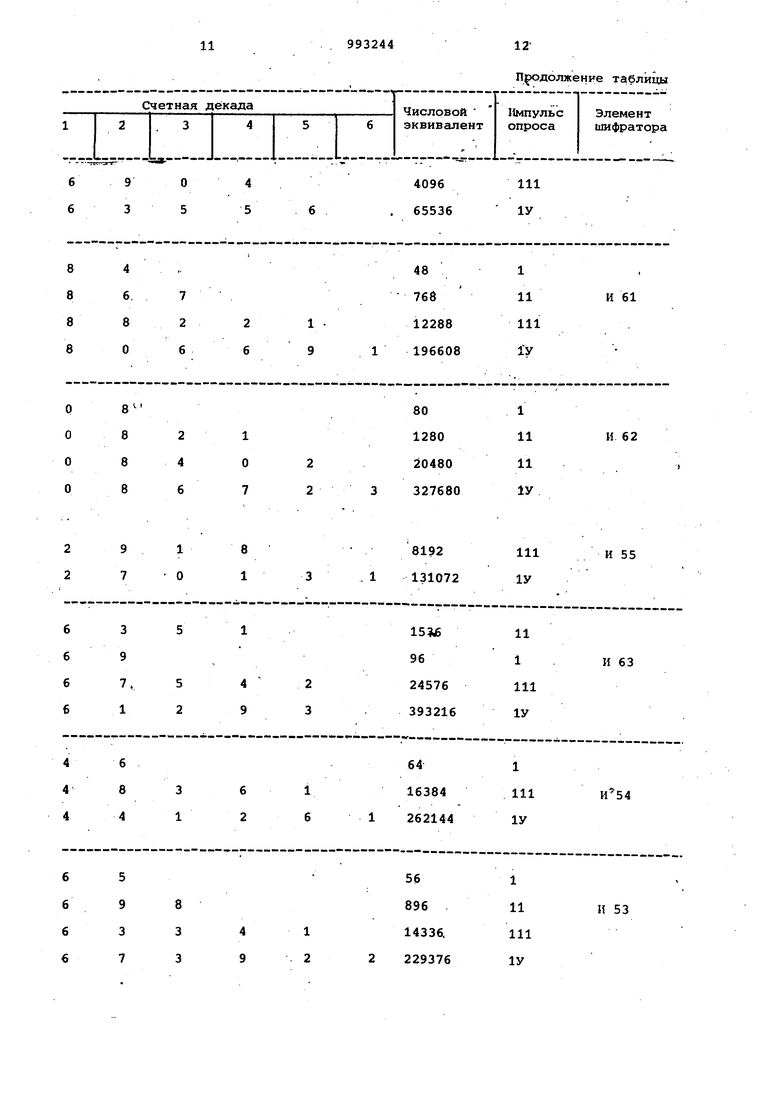

В таблице 1, поясняющей работу шифратора 5, приведены различные комбинации состояний четырех одновременно опрашив аемых разрядов 2 - 2 дв оичного кода, призаписи которых в десятичный реверсивный счетчик 6 используется вычитающий вход К счетных декад 7;f-7 и формирование установочного импульса, а также указанц элементы И 49- И 63 шифратора

5, сигналы с выходюв которых нсобхо ДИМЫ для формирования установочного импульса.

Сигналы с выходов элементов И 4963 шифратора 5 (фиг.. 2) поступают на выход м шифратора 5 и далее на информационный вход с блока 16 управления, с выхода которого сигналы пост упают на входы элемента ИЛИ 24 (фиг. 1), далее сигнал поступает на элемент 25 дифференцирования, где происходит выделение переднего фронта поступающего сигнала, Который устанавливает триггер 26 в единичное состояние. Сигнал высокого уровня с прямого выхода триггера 26 поступает на второй вход элемента И 27 на первый вход которого поступают тактовые импульсы с входа и блока 16 управления. СигнсШ с выходе элемента И 27 поступает на выход ф блока 16 управления, а также через элемент 28 задержки на нулевой установочный вход триггера 26.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Преобразователь двоичного кода в десятичный | 1976 |

|

SU691842A1 |

| Преобразователь двоичного кода в десятичный | 1974 |

|

SU525944A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДЕСЯТИЧНЫЙ | 1971 |

|

SU432486A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU903859A1 |

8 8 8 8

1 О 7

2 4 6

2 2

8

3 1 3

4

6 8 О

4 4

О О

7 3

8 4

4 9

1

6 6

1

11 111

И 56 1У

11

111

И 57

1У

И 58

11 1У

640 1 163840

1

72

И 59

11

18432

1У 2 294912

1 11

16 256

И 60

4 5

О

9 3

5

4 6. 8 О

7 2 6

2 6

1 9

8 8 8

1 О 7

2 4 6

2

2

Продолжение таблицы

111

4096 1У 65536

1

11 111

И 61 1У

1

И 62

11 11 1У

Сигнал с выхода блока 16 управления поступает далее на вход Л шифратора 5 и на в:код 5 блока 73 формирования установочного импульса (фиг. 2 и 3).

Сигналы с выходов элементов И 4963 шифратора 5 поступают также на вход t блока 73 формирования установочного импульса (фиг. 3) и далее на входы элементов ИЛИ (){, с выходов которых сигналы поступают на второй вход элементов И (75 k);i, на первый вход которых поступают сигналы импульсов опроса по входу Ui . Сигналы с выходов элемеН тов И ()i поступают на входы элементов ИЛИ (), , с выходов которых сигналы поступают на вторые входа элемен1Ч в И 77-( -77, на первые входы которых, поступает импульс по входу я блока 73 шифратора 5. На , элементов И формируется установочный импуль поступакицИй с выходов шифратора 5 на срответствующие входы группы 12

Продолженц таблицы

элементов IfflH, с.выходов которых сигнал поступает на суммирукиций вход К счетных декад 7i-7i: . Сигнал с

выхода элемента И 27 через элемент 28 задержки (время задержки элемента 28 выбирается, исходя из времени формирования установочного импульса в блоке 73 шифратора 5)-поступает

на нулевой установочный вход тpи гeра 26, переводя его в нулевое состояние. Сигнал низкого уровня с прямого выхода -триггера 26 поступает на первый вход элемента И 27, запрещая прохождение тактовых импульсов, поступающих с входа и блока 16 управления на второй вход эле54ента И 27.

После окончания сигнала Пуск

на входе р блока 16 управления

(фиг. 1) и соответственно на входе элемента НЕ 22 устанавливается сигнал низкого уровня. Сигнал высокого уровня с выхода элемента НЕ 22 поступает на второй вход элемента

и-НЕ 20, на первсм входе которого

ио--прсжнему присутствует сигнал виС1ЖОГО уровня. Сигнал низкого уровня с выхода элемента И-НЕ 20 инвертируется элементом НЕ 23 и на выход в блока 16 управления поступает сигнал высокого уровня. Наличие сигнала низкого уровня на выходе ш и высокого уровня на выходе э блока 16 управления, поступающих соответственно на управляющие входы у и И) счетных декад 7f -7 десятичног реверсивного счетчика 6, определяет режим счета.

Режим суммирующего счета последовательности импульсов от одного до пяти обеспечивается наличием суммирующих счетных входов К , на которые поступают соответствующие последовательности импульсов с выхода группы 12 элементов ИЛИ.

Режим ВЕлчитающего счета последовательности импульсов от одного .до четырех обеспечивается наличием вычитающих счетных входов к , на которые поступают соответствующие последовательности импульсов с выхода группы 14 элементов ИЛИ.

При переполнении счетных декад TI -7ц перенос из предыдущей счетно декады в последующую осуществляетсяс помощью группы элементов задержки, сигналы с выходов которых поступают на дополнительные входы группы 12 элементов ИЛИ.

Импульс заема с выхода счетных декад . передается в старшую счетную декаду с помощью второй группы элементов 9 -9| задержки, сигналы с выходов которых поступают на дополнительные входы вЛрой группы 14 элементов ИЛИ.

Таким образом, в десятичном реверсивном счетчике 6 после опроса первых, например, четырех разрядов двоичного кода записывается число, соответствующее весу одновременно опрашиваемых разрядсз.

Сигнал переполнения счетчика78 (фиг. 4). поступает на выход в переполнения формирователя 11 и далее на вход переключения распределителя 3 импульсов, после чего (фиг. 1 на выходе в распределителя 3 импульсов формируется сигнал опроса следующих, например, четырех разрядов 2-2 разрядов двоичного кода.

Сигнал опроса с выхода распределителя 3 импульсов поступает на вход U. шифратора 5 и далее на первые входы элементов И 30, 34, 38 и 42, на вторые входы которых уже поступили сигналы с прямых выходов регистра 10 двоичного кода через вход м шифратора 5.

В дальнейшем работа преобразователя двоичного кода в двоично-десятичный происходит аналогично описанному выше.

Процесс преобразования двоичного кода в двоично-десятичный продолжается до тех пор, пока не будут опрошены все разряды двоичного кода, записанного в регистр 10. Как только произойдет преобразование последних,. например,J четырёх разрядов двоичного кода в двоично-десятичный, процесс преобразования заканчивается и на выходе () распределения им0 пульсов появляется сигнал сброса.

Сигнал высокого уровня с выхода (J. распределителя 3 импульсов поступает на тактовый вход регистра 10 .двоичного кодами вход сброса форми5 рователя 11 последовательности импульсов, производя их установку в нулевое состояние. Сигнал высокого уровня с выхода д- распределителя импульсов поступает также на вход

0 П блока 16 управления, в результате чего на выходе m блока 16 управления появляется сигнал высокого уровня, поступающий на управляющий вход У счетных декад 7 -7, десятич5 ного реверсивного счетчика 6. Сигнал высокого уровня с выхода элемента ИЛИ 18 инвертируется элементом НЕ 19 (фиг. 1), С выхода элемента НЕ 19 сигнал низкого уровня поступает на ,

вход элемента И-НЕ 20, на выходе

которого появляется сигнал высокого уровня. Сигнал высокого уровЯя с выхода элемента И-НЕ 20 поступает на вход элемента НЕ 23. С выхода элемента НЕ 23 сигнал низкого уровня по5 ступает на выход э блока 16 управления и далее на управляющий вход VO счетных декад , наличие сигнала высокого уровня на управляющих входах V и низкого - на управляющих

0 входах го счетных декад десятичногО) реверсивного счетчика 6 позволяет произвести его установку в нулевое состояние.

Таким образом, преобразователь

5 двоичного кода в двоично-десятичный подготовлен к приему следующего сигнала Пуск.

Время преобразования двоичного кода в двоично-десятичный равно

°Т,--()/{„, О)

где N - количество импульсов опроса;, S - количество групп одновременно опрашиваемых разрядов двоичного кода, имеющих хотя бы один из разрядов в опрашиваемой группе, установленный в единичное состояние; f.,- частота следования тактовых

импульсов.

Количество импульсов опроса определяется из выражения

«-3

M eMtiev

(г)

Q

65 с округлением в большую сторону,

где n - число разрядов преобразуемого двоичного кода; Q - количество одновременно опрашиваемых разрядов двоичного кода.

Для практических целей целесообразно воспользоваться упрощенным выражением, получаемым из выражения (1 при условии равенства N.5, определяющем максимальное -время преобразования двоичного кода в. двоично-десятичный

V6N|5

Максимальное время преобразования двоичного кода в двоично-десятичный для преобразователя прототипа определяется выражением

ауу ох- 1 и

Коэффициент быстродействияпредлагаемого преобразователя двоичного кода в двоично-десятичный по отношению к преобразователю (2) равен 1,666

- IWOIL I

.

yviQ. I Ч упа

Стоимость предлагаемого преобразователя двоичного кода в двоично-десятичный при этом увеличивается не.значительно, примерно на 8-12%, относительно стоимости преобразователяпрототипа.

Формула изобретения

5 первыми входами (i 1) элементов ИЛИ первой группы, остальные входаа которых соединены с первой группой выходов шифратора, вход переключения распределителя импульсов соединен с

0 выходом переполнения формирователя последовательности импульсов, о тлич ающийся тем, что, с целью повышения быстродействия, в-него введены блок управления, вторая группа

5 элементов И, а десятичный счетчик выполнен реверсивным и содержит вторую группу элементов задержки, вход i-ro элемента которой соединен с выходом заема i-и декады десятичного счетчика, а выход }-го элемента задержки

0 второй группы соединен с первым входом (i f1)-го элемента ИЛИ второй группы, остальные входы элементов ИЛИ второй группы соединены соответственно с второй группой выходов

шифратора, третья группа выходов

которого соединена с информационным входом блока управления, тактовый вход которого соединен с тактовым выходом блока опроса, выход сброса

0 которого соединен с входом сброса

блока управления, вход пуска которого соединен с входом пуска преобразователя, первый установочный и разреша- ющий выходам блока управления соеди5 нены соответственно с входами установки э нуль и входами разрешения установки всех декад десятичного счетчика, входы сложения и вычитания которого соединены соответственно с

0 выходами первой и второй групп элементов ИЛИ, второй установочный выход блока управления соединен с усгтановочным входом шифратора.

личающийся тем, что в , нем блок управления содержит элемент И-НЕ, элемент И, первый и второй элементы ИЛИ, чечыре элемента НЕ, элемент дифференцирования, элемент .

60 задержки и триггер, S-вход которого через элемент дифференцирования соединен с выходом первого элемента ИЛИ. входы которого являются информационными входами блока управления, пер65 вый и второй установочные выходы которого соединены соответственно с выходами второго элемента ИЛИ и элемента И, выход которого через элемент задержки соединен с R-входом триггера, выход которого соединен с первым входом элемента И, второй вход которого является входом сброcia, блок управления, пуска которого через первый элемент НЕ соедннен с первым входом элемента И-НЕ, второй вход которого через второй элемент НЕ соединен с выходом второго элемента ИЛИ, первый вход которого через ключ и третий элемент НЕ соединен с входом нуля, второй вход второго элемента ИЛИ является тактовым входом блока управления, разрушающий выход которого через четвёртый элемент НЕ соединен с выходом элемента И-НЕ.

счетчика, инверсный выход которого, соединен о первым входом второго элементаИ, второй вход которого соединен с прямым выходом триггера первого разряда счетчика, а выход

второго элемента И соединен счетным входом триггера второго разряда , счетчика, j-й (J«1-5) выход дешифратора соединен с входами с J-ro по пятый элементов ИЛИ группы.

Источники информации, принятые во внимание при экспертизе

кл. G06F 5/02, 1978.

кл. G06f 5/02, 1980.

tf2. У

%г1

Фиг.

Авторы

Даты

1983-01-30—Публикация

1981-08-03—Подача