1

Изобретение относится к технике передачи информации.

Известен адаптивный корректор для системы передачи многоуровневых сигналов, содержащий многозвенную аналоговую линию задержки, выходы звеньев которой соединены через регулируемые аттенюаторы с входом сумматора, выход которого является выходом корректора, причем к выходу среднега звена многозвенной аналоговой линии задержки подключены последовательно соеднйбнные нуль-компаратор и первый регистр сдвига, а выход корректора соединен с каскадно включенными устройством оценки полярности ошибки и вторым регистром сдвига; выходы каскадов первого регистра сдвига и выход второго регистра сдвига подключены к входам цифровых перемножителей, выходы которых соединены с управляющими направлением счета входами соответствующих реверсивных счетчиков, а выходы последних подключены к управляющим входам аттенюаторов til.

Включение такого адаптивного корректора до входа демодулятора приемника затруднительно и его применение требует повышения качественных показателей других систем настройки приемника. Кроме того, в стационарном режиме работы адаптивного корректора формируемые из выходных сигналов среднего звена оценки полярностей менее достоверны, чем оценки из выходных сигналов адаптивного корректора, поэтому показатели этого режима работы хуже.

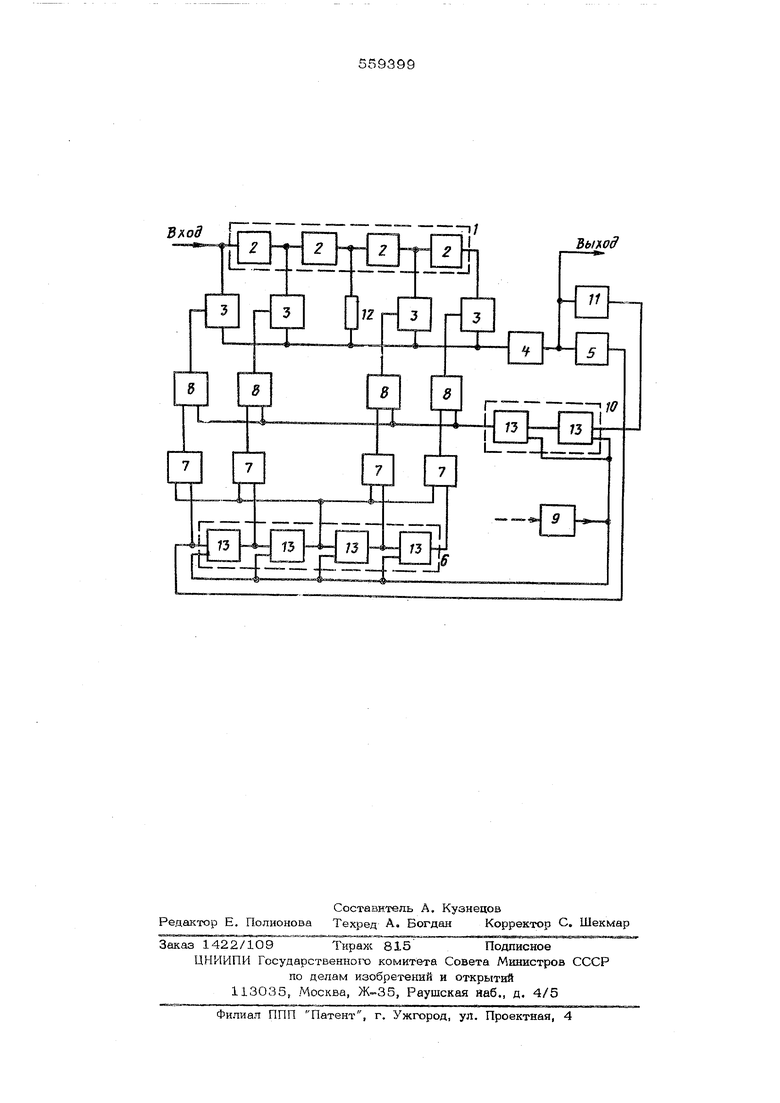

Известен также адаптивный корректор для системы передачи многоуровневых сигналов, содержащий аналоговую линию задержки, выходы соответствующих звеньев и вход которой соединены через регулируемые аттенюаторы с входом сумматора, к выходу которого подключены последовательно соединенные нуль-компаратор и первый регистр сдвига, выходы которого соединены с первыми входами цифровых перемножителей, выходы последних подключены к управляющим входам усредняющих реверсивных счетчиков, выходы которых соединены с управляющими входами регулируемых аттенюаторов и выход генератора тактовой частоты подключен к тактовым входам первого и второго регистров сдвига 2. Однако этот известный адаптивный корректор не обладает высокой помехоустойчивостью. Цель изобретения - повышение помехоустойчивости. Для этого в адаптивный корректор для системы передачи MHoroypoBHeBuxJсигналов, содержащий аналоговую линию задержки, выходы соответствующих звеньев и вход ко торой соединены через регулируемые аттенюаторы с входом сумматора к выходу которого подключены последовательно соединенные нуль-компаратор и первый регистр сдвига, выходы, которого соединены с первыми входами цифровых перемножителей, вы ходы последних подключены к управляющим входам усредняющих реверсивных счетчиков, выходы которых соединены с управляющими входами регулируемых аттенюаторов и выход генератора тактовой частоты подключен к тактовым входам первого и второго регистров сдвига, введен фиксатор превышени уровня максимального значения сигнала, .включенный между сумматором и вторым регистром сдвига, выход которого соедине с тактовыми входами усредншощих реверсив ных счетчиков, причем вторые входы цифровых перемножителей подключены к выходу соответствующего разряда первого регистра сдвига. На чертеже приведена структурная схема адаптивного корректора. Адаптивный корректор- для системы пере дачи мнoгoypoвнeвыx сигналов содержит ана логовую линию задержки 1, выходы соответ ствующих звеньев 2 и вход которой соединены, через perynHpyei ase аттенюаторы 3 с входом сумматора 4, к выходу которого подключены последовательно соединенные нуль-компаратор 5 и первый регистр сдвига 6, выходы которого соединены с первыми входами цифровых перемножителей 7, вы ходы которых подключены к управляющим входам усредняющих реверсивных счетчиков 8, выходы которых соединены с управляющими входами регулируемых аттенюаторов 3, генератор тактовой частоты 9, выход которого подключен к тактовым входам пер вого и второго регистров сдвига 6 и 10, а также фиксатор 11 превышения уровня максимального значения сигнала, включенный между сумматором 4 и вторым регист ром сдвига 1О, выход, которого соединен с тактовыми входами усредняющих реверсивных счетчиков 8, и резистор 12, причем вторые входы цифровых перемножителей 7 подключены к выходу соответствующего ра ряда первого регистра сдвига 6. Первый и второй регистры сдвига 6 и 10 состоят из аналогичных каскадов 13. Адаптивный корректор работает следуюим образом. Поступающие на вход адаптивного корректора искаженные сигналы задерживаются в, веньях 2 аналоговой линии задержки 1 на время, равное периоду частоты передачи информационных сигналов. Выходные сигналы звеньев 2 подаются с некоторыми весами, определяемыми величиной регулируемых аттенюаторов 3, на вход сумматора 4. Вес центрального отвода аналоговой линии задержки задается резистором 12, а возникающие изменения уровня основного отсчета компенсируются известными устройствами автоматической регулировки усиления систем передачи с многоуровневым сигналом. Установка минимизирующих межсимвольные искажения весов по отводам аналоговой линии задержки 1 производится автоматически в процессе передачи информации изменением величин регулируемых аттенюаторов 3. Направление регулировки к оптимальные величины регулируемых аттенюаторов 3 определяются в блоке управления, состоящем из нуль-компаратора 5, фиксатора 11 превыщения уровня максимального значения сигнала, .первого и второго регистров сдвига 6 и 10, цифровых перемножителей 7 и усредняющих реверсивных счетчиков 8, соответствующей обработкой появляющихся в отсчетные моменты времени выходных сигналов аналогового коррелятора. В первый регистр. сдвига 6 записываются отсчетные значения полярностей, определяемые нулькомпаратором 5, выходных сигналов сумматора 4, которые являются оценками полярностей передаваемых позиций многоуровневого сигнала. Первый регистр сдвига 6 для обеспечения необходимых временных соотнощений содержит равное количеству звеньев 2 число каскадов 13. Посредством фиксатора 11 регистрируются превыщения абсолтотным значением выходного сигнала сумматора 4 величины, больщей максимального значения многоуровневого сигнала на задаваемую величину, в частности, на величину, равную полуразности 1Г значений смежных позиций сигнала. Появляющиеся в отсчетные моменты времени сигналы о превыщении с выхода фиксатора J 1 записываются во второй регистр СДВ1.а SO, содержащий количество каскадов 13, раьное.числу устраняемых мещающих отсчетов преддействия импульсного отклика. Вводимые во второй регистр сдвига 10 сигналы о превыщении несут с больщей достоверностью информацию о приеме в этот отсчетный момент позиции сигнала с максимальной абсолютной амплитудой и О превышении абсолютным значением прме-; хи величины полурааности U . Записываемый в тот же отсчетный момент в первый регистр сдвига 7 сигнал полярности принимаемой позиции несет также информацию о полярности помехи. Сдвиг и запись -сигналов в регистрах сдвига 6 и 10 осуществляется с частотой поступления информационных сигналов по выходным сигналам генера тора тактовой чатоть| ,9. Требуемые для управления регулируемых аттенюаторов 3 произведения полярностей помех на сдвинутые во времени полярности информационных сигналов формируются в цифровых перемножителях 7, на входы которых поступают вы ходные сигналы каскадов 13 первого регист ра сдвига 6. Выходные сигналы цифровых перемножителей 7 управляют в моменты появления сигналов о превышении с выхода второго регистра сдвига 1О направлением счета в усредняющих реверсивных счетчиках 8, так как только в эти моменты выходные сигналы центрального отвода первого регист ра сдвига 6 о полярности сигнала совпадают с полярностями помех заданного абсолют ного значения. Формируемые в такие моменты выходные сигналы цифровых перемножитепей 7 усредняются в усредняющих реверсивных счетчиках 8 с целью повышения достоверности правильной регулировки регулируемых аттенюаторов 3. Регулировка любого регулируемого аттенюатора 3 происходит каждый раз при переполнении подключенного к его управляющему входу усредняющего реверсивного счетчика 8, причем направление регулировки определяется соответствующими бинарными значениями сигналов переполнения усредняющего реверсивного счетчика 8. После регулировки веса соответствующего отвода аналоговой лийии задержки 1 усредняюший реверсивный счетчик 8 возвращается в исходное состояние и процесс регулировки весов отводов повторяется до тех пор, пока максимальная величина помех не станет менее заданного порогом фиксатора 11 абсолютного уровня помех, в частности, менее величины, равной полуразности (J . В таком, случае отсутствие помех с амплитудами боль ше этой полуразности U соответствует условию отсутствия ошибок в передаваемой информации. Улучшение помехоустойчивости аналогового корректора обусловлено тремя факторами:- больщой достоверностью правильного формирования оценок полярностей помех, т.к. ложное формирование знака помехи возможно только при маловероятных, даже при больших искажениях, помехах с амплитудами, больше суммы максимального значения сигнал. и удвоенной полуразности {J ; - повышенной достоверностью оценок полярности соседних импульсов в моменты усреднения, так как усреднение производится только-при помехах, больших полуразностн и., а амплитуда межсимвольной помехи прямо пропорциональна амплитудам соседних импульсов, вследствие чего оценки полярностей больших по амплитуде сигналов при приеме более надежны; - вьщелением из суммарной помехи полярности увеличенных значений мешающих отсчетов от позиций сигнала с максимальной абсолютной амплитудой. При возникновении скачкообразных занижений уровня сигнала происходит автоматическая блокировка блока управления регулируемыми аттенюаторами 3 за счет отсутствия в этом случае превыщений порога фиксатора 11. Формула изобретения Адаптивнь й корректор для системы передачи многоуровневых сигналов, содержащий аналоговую линию задержки, выходы соответствующих звеньев и вход которой соединены через регулируемые аттенюаторы с входом сумматора, к выходу которого подключены последовательно соединенные нулькомпаратор и первый регистр сдвига, выходы которого соединены с первыми входами цифровых перемножителей, выходы последних подключены к управляющим входам усредняющих реверсивных счетчиков, выходы которых соединены с управляющими входами регулируемых аттенюаторов, и выход генератора тактовой частоты подключен к тактовым входам первого и второго регистров сдвига, отличающийся тем, что, с целью повышения помехоустойчивости, введоЕ фиксатор превышения уровня максимального значения сигнала, включенный между cyMNfaтором и вторым регистром сдвига, выход которого соединен с тактовыми входами уседняющих реверсивных счетчиков, причем вторые входы цифровых перемножктеле/ подлючены к выходу соответствующего (разряа первого регистра сдвига. Источники информации, принятые во вниание при экспертизе: 1. Патент США К 3753668, класс 33-18, 1971. 2. Данилов Б.С. и др. Однополосноя ередача цифровых сигналов. ., Снязьи., 1974, с. 1ОЗ-1.11 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивной настройки корректора межсимвольных искажений | 1977 |

|

SU743212A1 |

| Нелинейно-нелинейный корректор коррелированного сигнала | 1984 |

|

SU1225017A1 |

| Корректор | 1981 |

|

SU1137583A1 |

| Линейный корректор коррелированного сигнала | 1984 |

|

SU1243136A1 |

| Устройство для адаптивной коррекции межсимвольной интерференции | 1980 |

|

SU987825A1 |

| ЦИФРОВОЙ АВТОМАТИЧЕСКИЙ КОРРЕКТОР СИГНАЛОВ | 1992 |

|

RU2106062C1 |

| Нелинейно-нелинейное устройство коррекции межсимвольной интерференции при приеме коррелированного сигнала | 1983 |

|

SU1125750A1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1210225A1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1989 |

|

SU1809739A1 |

Авторы

Даты

1977-05-25—Публикация

1975-05-12—Подача