Изобретение относится к технике радиосвязи и может использоваться в системах передачи дискретных сообщений по каналам связи с межсимвольной интерференцией (МСИ) и аддитивной помехой (шумом).

Цель изобретения повышение достоверности приема за счет увеличения точности оценивания импульсной реакции канала.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается наличием новых блоков: блок памяти, второй регистр сдвига, вторая линия задержки с N отводами, коммутатор сигналов и их связями с остальными элементами схемы.

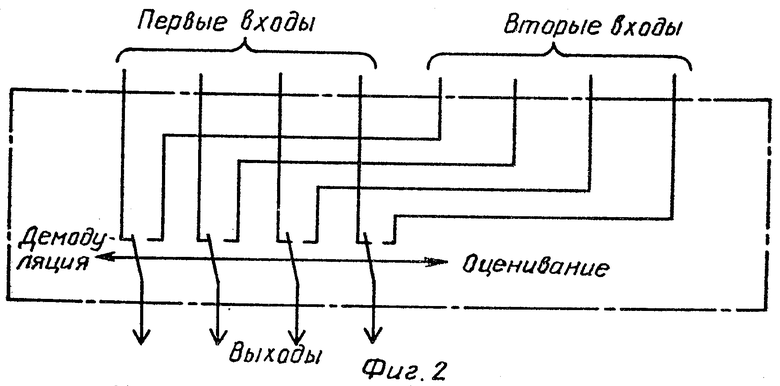

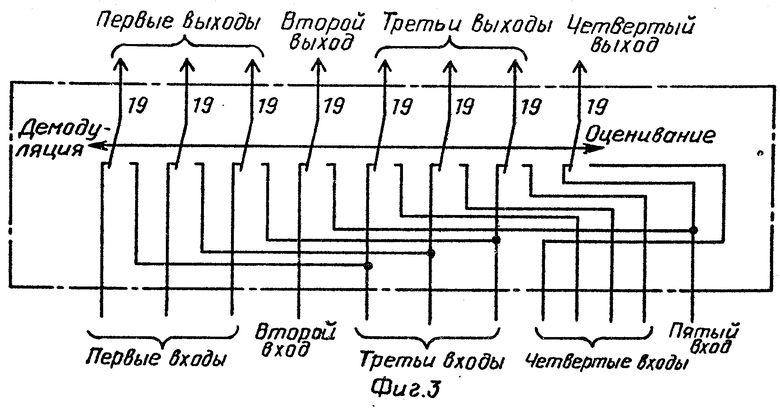

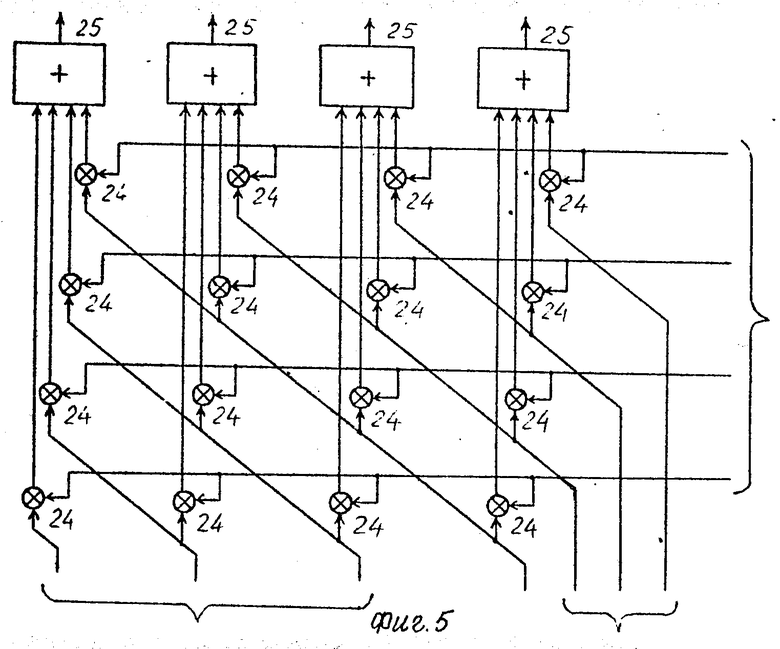

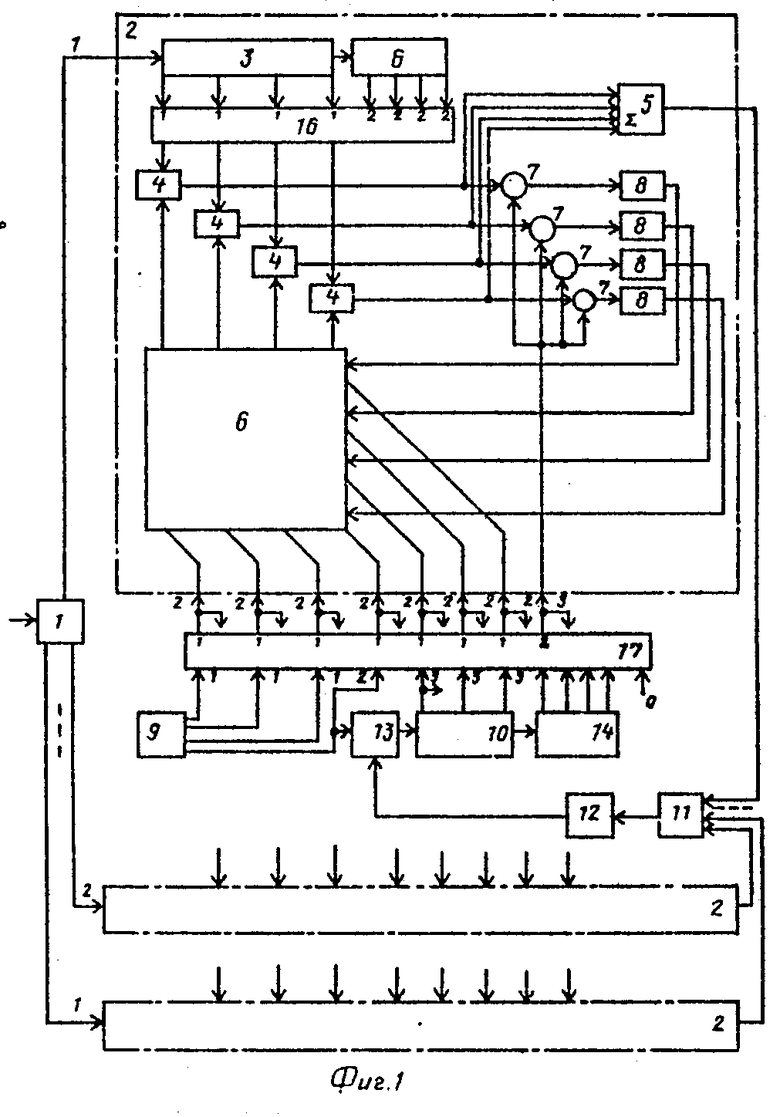

На фиг. 1 представлена структурная электрическая схема устройства; на фиг.2 схема коммутатора сигналов; на фиг.3 схема коммутатора; на фиг.4 схема блока расщепления сигналов; на фиг.5 схема матричного перемножителя.

Устройство содержит блок 1 расщепления сигнала, блоки 2 обработки сигнала, состоящие каждый из первой линии 3 задержки с N отводами, N вычитателей 4, сумматора сигналов 5, матричного перемножителя 6, N перемножителей 7, N усредняющих фильтров 8, второй линии 15 задержки с N отводами и коммутатора сигналов 16, счетчик 9, первый регистр 10 сдвига, сумматор 11, дискриминатор 12 минимума, блок памяти 13, второй регистр 14 сдвига, коммутатор 17. На фиг.1-3 число N 4.

При этом вход блока 1 расщепления сигнала является входом всего устройства, выход сумматора 11 соединен с входом дискриминатора 12 минимума, выход каждого перемножителя 7 соединен с входом соответствующего усредняющего фильтра 8, выходы которых соединены с первыми входами матричного переменожителя 6, выходы которого соединены с первыми входами N вычитателей 4, выходы блока 1 расщепления сигнала подключены к первому входу соответствующего блока 2 обработки сигналов, являющегося входом первой линии 3 задержки с N отводами, выходы N вычитателей 4 подключены к первым входам соответствующих перемножителей 7 и к соответствующим входам сумматора сигналов 5, выход которого является выходом блока 2 обработки сигналов и подключен к соответствующему входу сумматора 11, первые выходы счетчика 9 соединены с первыми входами коммутатора 17, второй выход счетчика 9 соединен с вторым входом коммутатора 17 и первым входом блока 13 памяти, выходы первого регистра 10 выхода соединены с третьими входами коммутатора 17, а последний выход первого регистра 10, кроме того, соединен с входом второго регистра 14 сдвига, выходы которого соединены с четвертыми входами коммутатора 17, первые выходы коммутатора 17 соединены с вторыми входами матричного перемножителя 6 каждого блока обработки сигналов через его первые входы, а второй выход коммутатора 17 через третий вход каждого блока обработки сигналов соединен с объединенными вторыми входами перемножителей, выход дискриминатора 12 минимума соединен с вторым входом блока памяти, выход которого соединен с входом первого регистра 10 выхода, основной выход первой линии 3 задержки соединен с входом второй линии 15 задержки, а дополнительные выходы первой линии 3 задержки (ее N отводов) с первыми входами коммутатора 16 сигналов, выходы второй линии 15 соединены с вторыми входами коммутатора 16 сигналов, выходы которого соединены с вторыми входами вычитателей 4.

Коммутатор сигналов содержит N переключателей, работающих синхронно под управлением общего сигнала: на этапе демодуляции к N выходам коммутатора 16 сигналов подключены его первые входы, а на этапе оценивания вторые входы.

Коммутатор 17 содержит 2N переключателей, работающих синхронно под управлением того же сигнала, что и коммутатор 16 сигналов: на этапе демодуляции замкнутые левые (по фиг.3) цепи, а на этапе оценивания правые.

Принципиальным отличием коммутатора 17 является то, что коммутируются дискретные сигналы, в то время как в коммутаторе 16 сигналов аналоговые.

Устройство для демодуляции двоичных сигналов работает следующим образом.

1. Этап демодуляции.

Обозначая I номер элемента сигнала в бесконечной цепи сообщения, k номер отвода линии 3 задержки (считая справа налево), I номер отсчета импульсной реакции канала во времени (взятых с интервалом Т, равным тактовому интервалу), запишем сигнал xi,k на выходе k-го отвода:

xi,k ai+k-igi+Ui+k (1)

ai+k-igi+Ui+k (1)

где аi знак i-го элемента сообщения, реакция канала, от которого в рассматриваемый момент времени целиком укладывается в линии задержки 3;

gi(I=1.N) 1-й отсчет одной компоненты импульсной реакции канала;

N целое число, характеризующее время рассеяния в канале, равное числу отводов линии задержки 3 и числу усредняющих фильтров 8;

Ui+k помеха.

В вычитателях 4 происходит вычитание из xi,k матричного произведения, полученного в матричном перемножителе 6 и повторяющего структуру (1):

ci,k= xi,k - bi+k-1

bi+k-1 (2) Здесь bi+k-1 (в двоичном случае равные ± 1) знаковые коэффициенты, поступающие на вторые входы матричного перемножителя 6 от коммутатора 17;

(2) Здесь bi+k-1 (в двоичном случае равные ± 1) знаковые коэффициенты, поступающие на вторые входы матричного перемножителя 6 от коммутатора 17; оценки отсчетов компоненты импульсной реакции канала с выходов усредняющих фильтров 8 (счет I ведется снизу вверх).

оценки отсчетов компоненты импульсной реакции канала с выходов усредняющих фильтров 8 (счет I ведется снизу вверх).

В главной диагонали k I, поэтому в ней bi+k-1=bi.

Разностные сигналы ci,k поступают на входы сумматора 5 и на первые входы перемножителей 7. На этапе демодуляции на объединенные вторые входы перемножителей 7 от коммутатора 17 поступает запирающий сигнал, и перемножители 7 заперты.

В сумматоре сигналов 5 происходит геометрическое сложение ci,k и на его выходе образуется сигнал di, пропорциональный расстоянию между вектором отсчетов входного сигнала xi,k и вектором опорного сигнала, соответствующего некоторой комбинации знаковых коэффициентов bi+k-1:

di D[{ci,k} (3) здесь D[ · некоторый нелинейный функционал, например

di (4)

(4)

При фиксированных xi,k и  различным наборам bi+k-1 соответствуют различные di. В сумматоре 11 сумма (4) дополняется аналоговыми слагаемыми от других компонент.

различным наборам bi+k-1 соответствуют различные di. В сумматоре 11 сумма (4) дополняется аналоговыми слагаемыми от других компонент.

Если  gi, U1+k=0, то минимальное di=0 образуется при bi+k-1 ai+k-1. Таким образом, если осуществить полный перебор различных комбинаций bi+k-1, а зафиксировать ту комбинацию, которой соответствовало минимальное значение bi, вычисленное по (2) и (4), то в этой комбинации с высокой вероятностью выполняется требование bi+1-1= ai+k-1, в том числе (для главной диагонали, где k I) bi=ai.

gi, U1+k=0, то минимальное di=0 образуется при bi+k-1 ai+k-1. Таким образом, если осуществить полный перебор различных комбинаций bi+k-1, а зафиксировать ту комбинацию, которой соответствовало минимальное значение bi, вычисленное по (2) и (4), то в этой комбинации с высокой вероятностью выполняется требование bi+1-1= ai+k-1, в том числе (для главной диагонали, где k I) bi=ai.

Полный перебор комбинаций bi+k-1 для k≥1 производится в счетчике 9. На этапе демодуляции эти комбинации поступают через открытые первые и второй входы коммутатора 17 на вторые входы матричного перемножителя 6 (на нижние и главную диагональ соответственно). Сигнал bi(k=1), поступающий на главную диагональ перемножителя 6, поступает также на первый (информационный) вход блока памяти 13. Значения di, вычисляемые в сумматоре 11, последовательно сравниваются между собой в дискриминаторе минимума 12. При появлении в процессе перебора нового di меньшего, чем все предыдущие, на его выходе появляется импульс. Этот импульс поступает на второй (управляющий) вход блока памяти 13 и вызывает перезапись bi с второго выхода счетчика в блок памяти 13. К концу процесса перебора комбинаций значение bi, записанное в блок памяти 13, будет принадлежать комбинации элементов, обеспечивающей наименьшее di, то есть наиболее правдоподобной комбинации.

2. Этап оценивания.

С выходов первого регистра 10 сдвига через открытые третьи входы коммутатора 17 на вторые входы матричного перемножителя 6 поступают окончательные решения bi-1, bi-2.bi-N+1 (нижние диагонали). Через открытые четвертые входы коммутатора 17 с выходов второго регистра 14 сдвига на вторые входы матричного перемножителя 6 поступают решения bi-N-1, b1-N-2.bi-2N+1 (верхние диагонали), а на объединенные вторые входы перемножителей 7 решение bi-N. Через открытый пятый вход коммутатора 17 на один из вторых входов матричного перемножителя 6 (на главную диагональ) поступает запирающий сигнал. Через открытые вторые входы коммутатора 16 сигналов с выходов второй линии 15 задержки на вторые входы вычитателей 4 поступают отсчеты входного сигнала Х, задержанные по i на величину N.

Таким образом, на первые входы перемножителей 7 вместо ci,kпоступают ci,k:

ci,k= xi-N,k - b

b (5) а на вторые объединенные входы перемножителей 7 задержанное решение bi-N. В перемножителях 7 происходит снятие манипуляции (умножение на знаковый коэффициент), в результате чего на выходе k-го перемножителя 7 получается некоторый сигнал Yi,k

(5) а на вторые объединенные входы перемножителей 7 задержанное решение bi-N. В перемножителях 7 происходит снятие манипуляции (умножение на знаковый коэффициент), в результате чего на выходе k-го перемножителя 7 получается некоторый сигнал Yi,k

Yi,k= ci,k, b xi-N,k -

xi-N,k - bi-N+k-i,

bi-N+k-i,  bi-N (6) Подставляя (1) в (6) и объединяя суммы, получим: Yi,k=

bi-N (6) Подставляя (1) в (6) и объединяя суммы, получим: Yi,k= ai-N,gk +

ai-N,gk +  (ai-N+k-i, ge-bi-N+k-i,

(ai-N+k-i, ge-bi-N+k-i, )+

)+ +U

+U , bi-N (7)

, bi-N (7)

При отсутствии помехи (U1-N+k=0) и при  ≡ gi на этапе демодуляции фиксируются bi ai, то есть bi-N+k-1=ai-N+k-1 для всех k,I и из (7) получаем Yi,k gk. Здесь учтено, что аi2 ≡ 1, aibi ≡ 1.

≡ gi на этапе демодуляции фиксируются bi ai, то есть bi-N+k-1=ai-N+k-1 для всех k,I и из (7) получаем Yi,k gk. Здесь учтено, что аi2 ≡ 1, aibi ≡ 1.

Таким образом, на входе каждого k-го усредняющего фильтра 8 будет gk. Значит, в стационарном режиме и на их выходах будут gk. Поэтому выходные сигналы фильтров 8 могут быть использованы в качестве оценок gi(k=I). Поэтому в схеме они заведены на первые входы матричного перемножителя 6.

Если есть помехи, то условия Ui-N+k ≡ 0 и gi=gi нарушаются. Поэтому не всегда aibi 1. Обозначим aibi 1+γi имея в виду, что в случае ошибки γi-2, и перепишем (7) в виде

Yi,k=gk+γi-Ngk+b (ai-N+k-i, gi-

(ai-N+k-i, gi-

-bi-N+k-i,  )+bi-N, Ui-N+k (8)

)+bi-N, Ui-N+k (8)

Лишь первое слагаемое в (8) является полезным, все прочие образуют помеху. Для ее подавления служат усредняющие фильтры 8. Остаточная погрешность εi,k gi,k gk зависит от дисперсии шума и соотношения величин постоянной времени фильтра 8 и тактового интервала Т.

Переключение коммутаторов 16, 17 происходит синхронно с тактовой частотой по командам из блока управления.

В течение тактового интервала на выходах линий задержки 3, 15 и регистров сдвига 10, 14 сигналы (аналоговые и дискретные соответственно) сохраняются неизменными.

По окончании тактового интервала значение символа bi, зафиксированное в блоке памяти 13, записывается в первую (левую по схеме) ячейку первого регистра 10 сдвига, а содержимое системы регистров 10-14 передвигается на одну позицию вправо.

Регистры 10 и 14 могут быть объединены в единый регистр с 2N-1 ячейками, тактируемыми общим тактовым импульсом.

Линии задержки 3 и 15 могут быть объединены в единую линию задержки с 2N отводами. Вместе с первым коммутатором 16 эту единую линию можно рассматривать как линию с переменной задержкой во времени. При цифровой реализации линии 3, 15 и коммутатор сигналов 16 эквивалентны одному ОЗУ с 2N ячейками.

Существенным отличием предлагаемого устройства от прототипа является защищенность тракта оценивания от шумов: в выделении отсчетов импульсной характеристики канала участвуют не предварительные, а окончательные решения демодулятора, среди которых меньше ошибочных. В каналах с медленными замираниями сигнала предлагаемое устройство сохраняет все прочие преимущества прототипа. Если за время задержки решения (единицы миллисекунд) свойства канала практически не меняются, то есть форма импульсной реакции сохраняется, то задержка оценки не приведет к увеличению вероятности ошибок демодуляции. Таким образом, предлагаемое устройство наиболее эффективно в каналах с медленными замираниями, но большим уровнем помех (малым отношением сигнал помеха).

Вместо счетчика 9 в устройстве может быть использован любой другой блок формирования двоичных комбинаций, в том числе счетчик по коду Грея (осуществляющий на каждом шаге изменение состояния только одной из диагоналей матричного перемножителя), регистр последовательных приближений (осуществляющий ускоренный поиск наиболее достоверного bi), комбинация счетчиков (при очень большом N). При этом существенные признаки устройства не изменяются.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оценки параметров многолучевого канала связи | 1991 |

|

SU1781828A1 |

| Устройство для демодуляции двоичных сигналов | 1988 |

|

SU1617656A1 |

| МОДИФИЦИРОВАННЫЙ ФИЛЬТР КАЛМАНА | 1992 |

|

RU2160496C2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ И ДЛЯ ОЦЕНКИ ПАРАМЕТРОВ КАНАЛА | 2004 |

|

RU2271070C2 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1991 |

|

RU2065668C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ | 2004 |

|

RU2267230C1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

Сущность изобретения: устройство содержит 1 блок расщепления сигнала (1), n блоков обработки сигнала (2), каждый из которых содержит 2 линии задержки (3 и 15), n вычитателей (4), 1 сумматор сигналов (5), матричный перемножитель (6), n перемножителей (7), n усредняющих фильтров (8), 1 коммутатор сигналов (16), 1 счетчик (9), 2 регистра сдвига (10 и 14), 1 сумматор (11), 1 дискриминатор минимума (12), 1 блок памяти (13), 1 коммутатор (17). 5 ил.

УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ, содержащее блок расщепления сигналов, выходы которого соединены с первыми входами блоков обработки сигналов, вторые входы которых подключены к соответствующим первым выходам коммутатора, первый и второй входы которого подключены к соответствующим выходам счетчика, первый регистр сдвига, выходы которого соединены с соответствующими третьими входами коммутатора, дискриминатор минимума, вход которого подключен к выходу сумматора, входы которого подключены к выходам блоков обработки сигналов, каждый из которых содержит вычитатель, первую линию задержки, перемножители, усредняющие фильтры, сумматор сигналов и матричный перемножитель, выходы которого соединены с первыми входами соответствующих вычитателей, выходы которых соединены с входами сумматора сигналов и с первыми входами соответствующих перемножителей, выходы которых соединены с входами соответствующих усредняющих фильтров, выходы которых подключены к первым входам матричного перемножителя, вторые входы которого являются вторыми входами блока обработки сигналов, первым входом которого является вход первой линии задержки, объединенные вторые входы перемножителей являются третьим входом блока обработки сигналов, выходом которого является выход сумматора сигналов, отличающееся тем, что, с целью повышения достоверности приема за счет увеличения точности оценки импульсной реакции канала, введены блок памяти и второй регистр сдвига, выходы которого соединены с четвертыми входами коммутатора, второй вход которого подключен к первому входу блока памяти, выход которого соединен с входом первого регистра сдвига, выход которого соединен с входом второго регистра сдвига, выход дискриминатора минимума соединен с вторым входом блока памяти, второй выход коммутатора подключен к третьему входу каждого блока обработки сигналов, а в каждый блок обработки сигналов введены коммутатор сигналов и вторая линия задержки, вход которой подключен к основному выходу первой линии задержки, дополнительные выходы которой соединены с первыми входами коммутатора сигналов, выходы которого соединены с вторыми входами соответствующих вычитателей, причем выходы второй линии задержки соединены с вторыми входами коммутатора сигналов.

| Авторское свидетельство СССР N 1588256, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-08-09—Публикация

1989-12-19—Подача