Изобретение относится к электросвязи и может использоваться в цифровых системах передачи данных.

Известны автоматические корректировки сигналов (АКС) с предварительной настройкой по тестовому сигналу, передаваемому по каналу связи до начала передачи данных. Такие АКС способны настраиваться в условиях больших начальных межсимвольных искажений и при значительном уровне шумов в канале.

В настоящее время почти исключительно реализуется АКС на основе цифровой обработки сигналов, в частности, с использованием цифровых нерекурсивных фильтров (НРФ), которые обеспечивают лучшие рабочие характеристики по сравнению с аналоговыми АКС. Известны примеры выполнения цифровых АКС в виде БИС. Однако применение в АКС обеспечивающих наибольшее быстродействие цифровых НРФ с параллельной обработкой оказывается затруднительным и дорогостоящим из-за необходимости применения в них большого количества сложных многоразрядных умножителей в отводах НРФ. Упрощение цифровой реализации АКС возможно путем исключения сложных многоразрядных умножителей, используя технику дельта-модулированных сигналов, применяя в АКС известный программируемый НРФ с двоичным сигналом на его входе и с "дельта-модулированными" коэффициентами отводов НРФ, в частности, с двоичными коэффициентами (книга: Р. Стил Принципы дельта-модуляции, 1979 г.).

В качестве прототипа взят автоматический корректор сигналов, описанный в статье Беккера, Хольцмана и Лакки "Устройство автоматической коррекции для систем связи", Труды института инженеров по электротехнике и радиоэлектронике, 1965, т. 53, N 1, с. 110 112, с предварительной настройкой по специальному тестовому сигналу, представляющему последовательность редко повторяющихся коротких импульсов, содержащей НРФ, выполненный на N + 1 перемножителях, выходы которых соединены со входами сумматора, выход которого является выходом НРФ, выделитель сигнала ошибки, N каскадный регистр сдвига (РГС) сигнала ошибки, выполненный с N + 1 отводами, N + 1 блоков управления коэффициентами усиления (БУКУ), каждый содержащий первый элемент И и разверсивный счетчик (РС), при этом отводы N-каскадного РГС сигнала ошибки подключены каждый ко входу сигнала ошибки соответствующего БУКУ, имеющих вход тактового сигнала.

Задачей, на решение которой направлено изобретение, является реализация АКС с предварительной настройкой по тестовому сигналу, выполненного на основе НРФ, практически снимающей ограничения на его создание в виде специализированной БИС, благодаря использованию техники дельта-модулированных сигналов.

Поставленная задача решается тем, что в цифровой АКС, содержащий НРФ, выполненный на N + 1 перемножителях, выходы которых соединены со входами сумматора, выход которого является выходом НРФ, выделитель сигнала ошибки, N-каркасный РГС сигнала ошибки, выполненный с N + 1 отводами, N + 1 БУКУ, каждый содержащий первый элемент И и РС, при этом отводы N каскадного РГС сигнала ошибки подключены каждый ко входу сигнала ошибки соответствующего БУКУ, имеющих вход тактового сигнала, введены линейный дельта-модулятор (ЛДМ) входного сигнала, вход которого является входом цифрового АКС, последовательно соединенные двойной интегратор и решающий блок (РБ), выход которого является выходом цифрового АКС, последовательно соединенные фильтр нижних частот (ФНЧ), ЛДМ сигнала ошибки и дельта-перемножитель на постоянный коэффициент, последовательно соединенные выключатель цепи тестового сигнала и регистр задержки, причем в НРФ введен N-каскадный РГС, выполненный с N + 1 отводами, вход которого является входом НРФ, каждый N + 1 перемножитель выполнен на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, один вход которого соединен с соответствующим отводом N-каскадного РГС, а другой вход с выходом соответствующего введенного триггера, а выход является выходом перемножителя, при этом в каждый БУКУ введены второй и третий элементы И и дельта-полный сумматор, выход которого подключен к управляющему входу РС, к счетному входу которого подключен выход третьего элемента И, выходы первого и второго элементов И подключены к первому и второму входам дельта полного сумматора, выходы РС являются выходами сигналов переполнения и обнуления БУКУ и подключены ко входам соответствующего триггера, выход которого соединен с первым входом второго элемента И соответствующего БУКУ, вторые входы первого, второго и третьего элементов И являются входом тестового сигнала, первый вход первого элемента И входом сигнала ошибки, первый вход третьего элемента И входом тактового сигнала в каждом БУКУ, при этом выход ЛДМ входного сигнала соединен со входом НРФ, выход которого подключен ко входу двойного интегратора, вход и выход РБ подключены к первому и второму входам выделителя сигнала ошибки, выход которого соединен со входом ФНЧ, выход РБ подключен ко входу выключателя цепи тестового сигнала, выход регистра задержки соединен со входами тестового сигнала Т + 1 БУКУ, входы сигналов ошибки которых подключены к соответствующим отводам N-каскадного РГС сигнала ошибки, вход тактового сигнала которого соединен с входами тактового сигнала N + 1 БУКУ, тактовыми входами ЛДМ входного сигнала, ЛДМ сигнала ошибки, НРФ и является первым тактовым входом цифрового АКС, вторым тактовым входом которого является тактовый вход РБ.

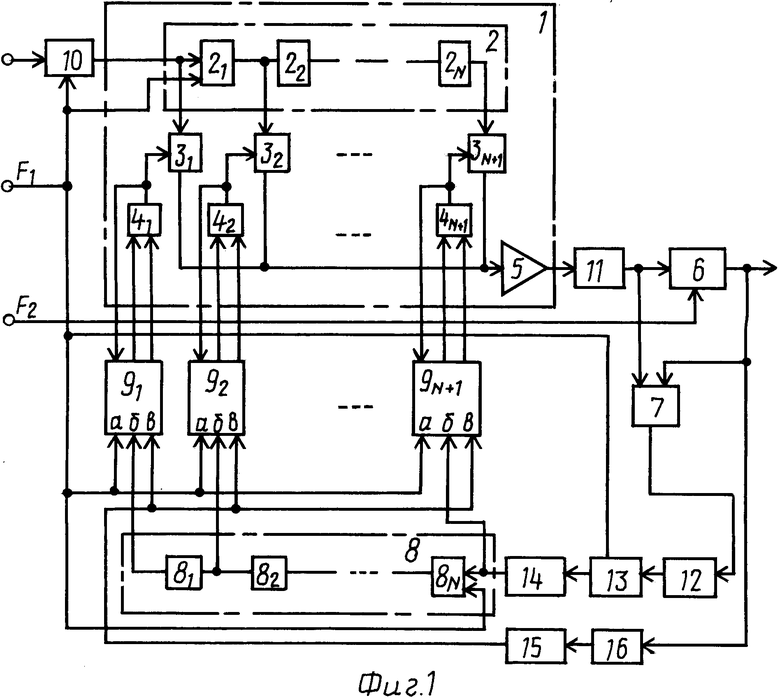

На фиг. 1 представлена структурная схема цифрового АКС; на фиг. 2 - структурная схема БУКУ.

Цифровой АКС на фиг. 1 содержит НРФ 1, выполненный на N-каскадном РГС2 с N + 1 отводами и элементами задержки 21 2N, N + 1 перемножителях на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 31 3N+1 и триггерах 41 4N+1, а также сумматоре 5, РБ6, выделитель 7 сигнала ошибки, N каскадный РГС8 сигнала ошибки с N + 1 отводами и с элементами задержки 81 8N, N + 1 БУКУ 91 9N+1, ЛДМ 10 входного сигнала, двойной интегратор 11, ФНЧ 12, ЛДМ 13 сигнала ошибки, дельта-перемножитель 14 на постоянный коэффициент, регистр 15 задержки, выключатель 16 цепи тестового сигнала.

БУКУ 9 на фиг. 2 содержит первый, второй и третий элементы И 17, 18 и 19, дельта-полный сумматор 20 и РС 21.

Цифровой АКС работает следующим образом.

Для него характерны два режима работы: режим настройкт АКС по тестовому сигналу и режим передачи данных. В режиме настройки АКС по каналу связи передается тестовый сигнал, представляющий последовательность редких коротких одиночных импульсов. Тестовый сигнал, последовательности тактовых импульсов частотой F1 и F2 поступают соответственно на информационный вход ЛДМ 10 входного сигнала, на вход тактовой частоты F1 и на вход тактовой частоты F2 устройства.

С выхода ЛДМ 10 входного сигнала дельта-модулированный входной сигнал поступает на первый вход РС 2 с отводов 21-N+1 которого сигналы поступают на первые входы элементов Исключающее ИЛИ 31-N+1, на вторые входы которых поступают сигналы с триггеров 41-N+1, перемноженные двоичные сигналы элементами Исключающее ИЛИ суммируются сумматором 5 и интегрируются двойным интегратором 11. Скорректированный сигнал с выхда двойного интегратора 11 поступает на РБ 6, выход которого является выходом устройства, и выделитель сигнала ошибки 7.

РБ 6 представляет простейшее пороговое устройство, преобразующее поступающие сигналы с двойного интегратора 11 с меняющимся уровнем в фиксированные по уровню и длительности импульсы на его выходе.

При этом в РБ 6 устанавливается порог, равный 1/2 номинальной величины принимаемого сигнала на его выходе. В выделителе сигнала ошибки 7 в моменты, определяемые стробирующими сигналами частоты F2, вычитаются сигналы, поступающие на первый и второй его входы соответственно с выхода двойного интегратора 11 и выхода РБ 6. Образовавшаяся на выходе выделителя сигнала ошибки 7 дискретная последовательность ошибок сглаживается ФНЧ 12, с выхода которого сглаженный сигнал ошибки поступает на ЛДМ 13 сигнала ошибки, с выхода которого дельта-модулированный сигнал ошибки поступает на вход дельта-перемножителя 14, в котором производится умножение на постоянный коэффициент Δ

Дельта модулированный двоичный сигнал ошибки с выхода дельта-перемножителя 14 поступает с отводов РГС 81-N+1 на входы "б" БУКУ 91-N+1, обеспечивающих обновление коэффициентов НРФ путем изменения состояния триггеров 41-N+1.

На входы "в" БУКУ 91-N+1 поступает тестовый сигнал с частотой F3 1/Tц (Tц период следования тестового сигнала). На входы "a" БУКУ 91-N+1 поступает тактовый сигнал с частотой  ( t - период следования посылок двоичного дельта-модулированного сигнала), который также подается на ЛДМ 10 входного сигнала, на ЛДМ 13 сигнала ошибки и на второй вход РГС 8. Между частотами F1, F2 и F3, как правило, должно выдерживаться следующее соотношение:

( t - период следования посылок двоичного дельта-модулированного сигнала), который также подается на ЛДМ 10 входного сигнала, на ЛДМ 13 сигнала ошибки и на второй вход РГС 8. Между частотами F1, F2 и F3, как правило, должно выдерживаться следующее соотношение:

F1≥(7oC8)•F2≥F3.

БУКУ 9 работает следующим образом.

С приходом задержанного регистром задержки 16 импульса тестового сигнала по заполнению РГС 8 на вход "b" БУКУ 9i, подключенного к первым входам первого, второго и третьего элементов И 17, 18 и 19, на выходах первого и второго элементов И 17 и 18, подключенных соответственно к первому и второму входам дельта-полного сумматора 20, возникает одно из двоичных состояний в зависимости от двоичных сигналов, поступивших в данный момент на вторые входы первого и второго элементов И 17 и 18 соответственно от дельта-перемножителя 14 на постоянный коэффициент и элемента обновляемой памяти коэффициента отвода-триггера 4i. Результат суммирования этих сигналов с выхода дельта-полного сумматора 220 поступает на управляющий вход РС 21, на счетный вход которого поступает простробированный тактовым сигналом частоты F1 тестовый сигнал с выхода третьего элемента И 19. В зависимости от управляющего сигнала ("1" или "0") содержимое РС 21 увеличивается или уменьшается на единицу. На выходах РС 21 со схемой сброса в среднее значение его шкалы по сигналам его переполнения и обнуления при его переполнении или при обнулении появляется сигнал, который поступает на соответствующий вход триггера 4i и изменяет его состояние. Измененное состояние триггера 4i подается на второй вход элемента И 18 и на второй вход двоичного перемножителя исключающее ИЛИ 3.

Для настройки корректора требуется многократное повторение описанной выше процедуры. Для перехода в режим передачи данных после его настройки цепь тестового сигнала разрывается выключателем 16. В режиме передачи данных функционирует только тракт, включающий ЛДМ 10 входного сигнала НРФ 1, двойной интегратор 11 и РБ 6. При этом триггеры 41-N+1 сохраняют неизменные значения.

В предлагаемом цифровом АКС реализуется интеративный алгоритм

где

C усредненное значение умноженной на постоянный коэффициент Δ ≪ 1 дельта-модулированной ошибки εдм.

усредненное значение умноженной на постоянный коэффициент Δ ≪ 1 дельта-модулированной ошибки εдм.

При этом  двоичные значения ∈ {1,0}.

двоичные значения ∈ {1,0}.

Используемые в цифровом АКС дельта-полные сумматоры 20 и дельта-перемножитель 14 на постоянный коэффициент представляют относительно простые элементы двоичное логики. В частности, схема дельта-полного сумматора 20 состоит из полного двоичного сумматора и D-триггера. Функциональные и электрические схемы и сведения об основных особенностях этих элементов содержатся, в частности, в статье Коувераса "Операции с дельта-модулированными сигналами" в журнале The Radio and Electronic Engineer 48, N 9, 1978.

Таким образом, исключение из структуры АКС аналоговой линии задержки и замена ее обычным двоичным регистром сдвига, а также замена многорезистивных схем аттенюаторов в нерекурсивном фильтре (а при цифровом его исполнении замена большого количества сложных многоразрядных умножителей) на простейшие перемножители элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, позволяют решить поставленную задачу и практически снять ограничения на выполнение АКС с использованием современной технологии в виде специализированной БИС.

Сущность изобретения: в цифровой автоматический корректор сигналов (АКС) с настройкой по тестовому сигналу до передачи данных с дельта-модулированным входным сигналом, что упрощает реализацию, и содержащий нерекурсивный фильтр (НРФ), выполненный на N + 1 перемножителях (П), выходы которых соединены со входами сумматора, выход которого является выходом НРФ, выделитель сигнала ошибка N-каскадный регистр сдвтга (РГС) сигнала ошибки, выполненный с N + 1 отводами, N + 1 блоков управления коэффициентами усиления (БУКУ), каждый содержащий первый элемент И и реверсивный счетчик (РС), при этом отводы N-каскадного РГС сигнала ошибки подключены каждый ко входу сигнала ошибки соответствующего БУКУ, имеющих вход тактового сигнала, введены линейный дельта-модулятор (ЛДМ) входного сигнала, вход которого является входом цирового АКС, последовательно соединенные двойной интегратор и решающий блок (РБ), выход которого является выходом цифрового АКС, последовательно соединенные фильтр нижних частот (ФНЧ), ЛДМ сигнала ошибки и дельта-перемножитель на постоянный коэффициент, последовательно соединенные выключатель цепи тестового сигнала и регистр задержки, причем в НРФ введен N-каскадный РГС, выполненный с N + 1 отводами, вход которого является входом НРФ, каждый N + 1 П выполнен на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, один вход которого соединен с соответствующим отводом N-каскадного РГС, а другой вход - с выходом соответствующего введенного триггера, а выход является выходом П, при этом в каждый БУКУ введены второй и третий элементы И и дельта-полный сумматор, выход которого подключен к управляющему входу РС, к счетному входу которого подключен выход третьего элемента И, выходы первого и второго элементов И подключены к первому и второму входам дельта-полного сумматора, выходы РС являются выходами сигналов переполнения и обнуления БУКУ и подключены ко входам соответствующего триггера, выход которого соединен с первым входом второго элемента И соответствующего БУКУ, вторые входы первого, второго и третьего элементов И являются входом тестового сигнала, первый вход первого элемента И - входом сигнала ошибки, первый вход третьего элемента И - входом тактового сигнала в каждом БУКУ, при этом выход ЛДМ входного сигнала соединен со входом НРФ, выход которого подключен ко входу двойного интегратора, вход и выход РБ подключены к первому и второму входам выделителя сигнала ошибки, выход которого соединен со входом ФНЧ, выход РБ подключен ко входу выключателя цепи тестового сигнала, выход регистра задержки соединен со входами тестового сигнала N + 1 БУКУ, входы сигналов ошибки которых подключены к соответствующим отводам N-каскадного РГС сигнала ошибки, вход тактового сигнала которого соединен с входами тактового сигнала N + 1 БУКУ, тактовыми входами ЛДМ входного сигнала, ЛДМ сигнала ошибки, НРФ и является первым тактовым входом цифрового АКС, вторым тактовым входом которого является тактовый вход РБ. 2 ил.

Цифровой автоматический корректор сигналов, содержащий нерекурсивный фильтр, выполненный на N + 1 перемножителях, выходы которых соединены с входами сумматора, выход которого является выходом нерекурсивного фильтра, выделитель сигнала ошибки, N-каскадный регистр сдвига сигнала ошибки, выполненный с N + 1 отводами, N + 1 блоков управления коэффициентами усиления, каждый содержащий первый элемент И и реверсивный счетчик, при этом отводы N-каскадного регистра сдвига сигнала ошибки подключены каждый к входу сигнала ошибки соответствующего блока управления коэффициентами усиления, имеющих вход тактового сигнала, отличающийся тем, что в него введены линейный дельта-модулятор входного сигнала, вход которого является входом цифрового автоматического корректора сигналов, последовательно соединенные двойной интегратор и решающий блок, выход которого является выходом цифрового автоматического корректора сигналов, последовательно соединенные фильтр нижних частот, линейный дельта-модулятор сигнала ошибки и дельта-перемножитель на постоянный коэффициент, последовательно соединенные выключатель цепи тестового сигнала и регистр задержки, причем в нерекурсивный фильтр введен N-каскадный регистр сдвига, выполненный с N + 1 отводами, вход которого является входом нерекурсивного фильтра, каждый N + 1 перемножитель выполнен на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, один вход которого соединен с соответствующим отводом N-каскадного регистра сдвига, а другой вход с выходом соответствующего введенного триггера, а выход является выходом перемножителя, при этом в каждый блок управления коэффициентом усиления введены второй и третий элементы И и дельта- полный сумматор, выход которого подключен к управляющему входу реверсивного счетчика, к счетному входу которого подключен выход третьего элемента И, выходы первого и второго элементов И подключены к первому и второму входам дельта-полного сумматора, выходы реверсивного счетчика являются выходами сигналов переполнения и обнуления блока управления коэффициентом усиления и подключены к входам соответствующего триггера, выход которого соединен с первым входом второго элемента И соответствующего блока управления коэффициентом усиления, вторые входы первого, второго и третьего элементов И являются входом тестового сигнала, первый вход первого элемента И входом сигнала ошибки, первый вход третьего элемента И входом тактового сигнала в каждом блоке управления коэффициентом усиления, при этом выход линейного дельта-модулятора входного сигнала соединен с входом нерекурсивного фильтра, выход которого подключен к входу двойного интегратора, вход и выход решающего блока подключены к первому и второму входам выделителя сигнала ошибки, выход которого соединен с входом фильтра нижних частот, выход решающего блока подключен к входу выключателя цепи тестового сигнала, выход регистра задержки соединен с входами тестового сигнала N + 1 блоков управления коэффициентами усиления, вход сигналов ошибки которых подключены к соответствующим отводам N-каскадного регистра сдвига сигнала ошибки, вход тактового сигнала которого соединен с входами тактового сигнала N + 1 блоков управления коэффициентами усиления, тактовыми входами линейных дельта-модулятора входного сигнала и дельта-модулятора сигнала ошибки нерекурсивного фильтра и является первым тактовым входом цифрового автоматического корректора сигналов, вторым тактовым входом которого является тактовый вход решающего блока.

| Беккер и др | |||

| Устройство автоматической коррекции для систем связи | |||

| Труды института инженеров по электротехнике и радиоэлектронике, т.53, N 1, 1965, с.110-112. |

Авторы

Даты

1998-02-27—Публикация

1992-12-18—Подача