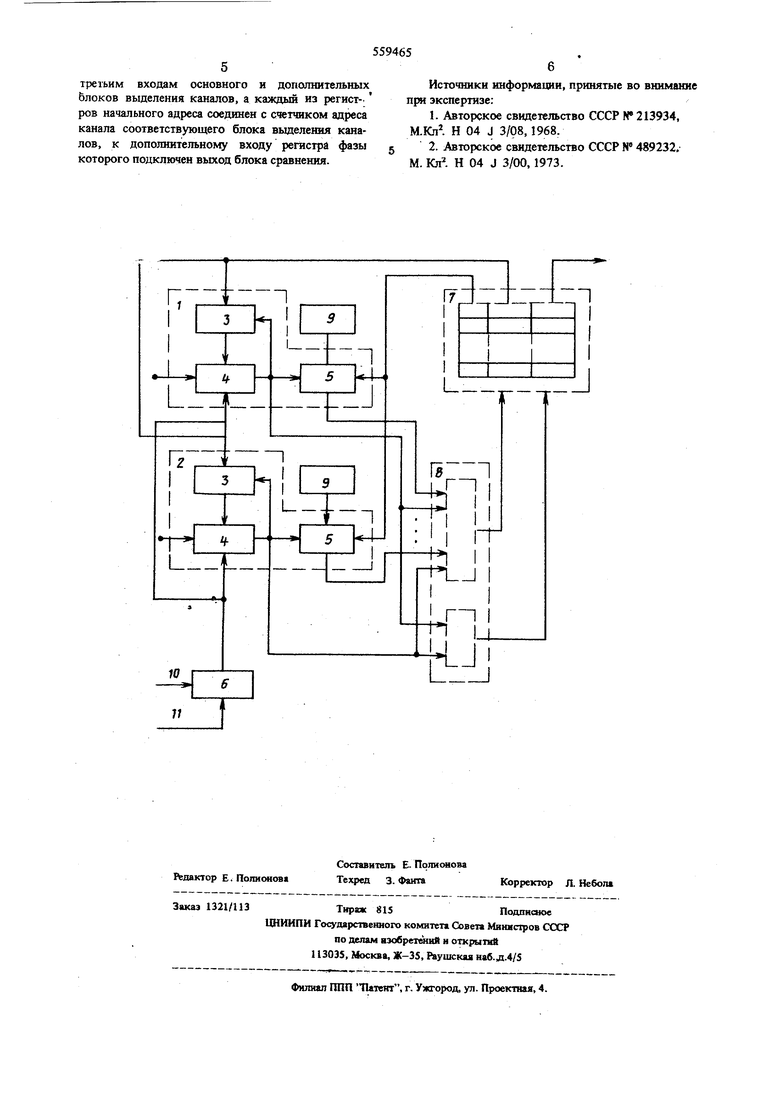

Изобретение относнтся к электросвязи и моягет использоваться для ввооа телеметрической информации в системы Обработки данных н в системах регистрации телеметрической информации. Известно устройство для селекции информационных каналов, содержащее счетчик канальных импульсов и декодирующую матрицу {1 . Оциако известное устройство обладает недостаточной информативностью. Известно также устройство для селекции ншформационных каналов, содержащее блок приема информации, соединенный с первым входом основного блока выделения каналов, вьшолненного в виде последовательно соединенных регистра фазы, блока сравнёння и счетчика адреса канала, и блок памяти, соешшенный с вторым входом основного блока выделения каналов 2J. Однако в данном устройстве для выделения информационных каналов из кадров высокой информативиости с различными частотами опроса каналов требуется большой объем блока памяти. Цель изобретения - упрощение устройства уменьшения числа ячеек блока памяти. Для этого в устройство для селекции информационных каналов, содержащее блок приема информации, соединенный с первым входом основного блока выделения каналов, выполненного в виде последовательно соединенных регистра фазы, блока сравнения и счетчика адреса канала, и блок памяти, соединенный с вторым входом основного блока вьщеления каналов, введены сумматор, регистры начального адреса и п дополнительных блоков выделения каналов, входы которых соединены с соответствующими входами основного блока выделения каналов, при этом выходы основного и дополнительных блоков вьщеления каналов через сумматор подключены к блоку памяти, дополнительный выход которого подключен к третьим входам основного и дотюлннтельных блоков выделения каналов, а каждый из регистров начального адреса соединен с адреса канала соответствующего блока вьщеления каналов, к дополнительному входу регистра фазы которого подключен выход блока сравнения. На чертеже изображена структурная электрическая схема предложенного устройства. Устройство содержит основной блок 1 выделения каналов ипдополнительных блоков 2 выде-.

ления каналов, каждый тлз которых выпозшен в виде последовательно соединенных регистра фазы 3, блока сравнения 4 и счетчика адреса 5 канала, а также содерясит блок приема информации 6, соединенный с первым входом основного блока 1 выделения каналов, и блок памяти 7, соединенный с вторым входом основного блока 1 выделения каналов, при этом входы дополнительных блоков 2 вьщеле1шя каналов соединены с соответствующими входами основного блока 1 выделения каналов, а выходы основного блока I и дополнительных блоков 2 выделения каналов через сумматор 8 подключены к блоку памяти 7, дополнительный выход которого подключен к третьим входом основного блока 1 и дополнительных блоков 2 выделения каналов. Устройство содержит также регистры 9 начального адреса, каждьш из которых соединен с счетчиком адреса 5 соответствующего блока 1,2 вьщеления каналов, к дополнительному входу регистра фазы 3 которых подключен выход блока сравнения 4.

Устройство работает следующим образом.

На вход 11 блока приема информации 6 nociyпает маркер цикла, который устанавливает его в начальное состояние и разрешает дальнейшее функщюнирование устройства. На вход 10 поступают канальные импульсы. На выходе блока приема информации 6 формируется номер канального импульса в цикле, который поступает на вход блоков сравнения 4 основного блока 1 и дополнительных блоков 2 вьщеления каналов. Число разрядов блока сравнения 4, участвующих в сравнении, задается управляющими сигналами в зависимости от частоты опроса каналов, выделяемых данным блоком вьщеле1шя каналов 1,2. При совпадении номера канального импульса с фазой, записанной в регистре фазы 3, срабатывает соответствующий блок сравнения 4, формирующий импульс сравнения, который поступает на управляющие входы регистра фазы 3 и счетчика адреса 5 канала, а также на входы сумматора 8. По переднему фронту импульса сравнения через один вход сумматора 8 на адресный вход блока памяти 7 поступает адрес со счеттака адреса 5 канала того блока выделения 1,2, в котором произощло сравнение, а через другой вход сумматора В импульс сравнения проходит на управляющий вход блока памяти 7 и осуществляется обращение к блоку памяти 7 по адресу, выбранному сумматором 8.

Из блока памяти 7 выбирается фаза, определяющая местоположение канального импульса следзтощего информационного канала данной частотной , номер информационного канала в данном такте и признак записи начального адреса. Фаза записывается в регистр фазы 3 соответствующего блока вьщеления каналов 1,2, а номер вьщеяяемого канала поступает на выход устройства. По заднему фронту импульса сравнения в зависимости от состояния признака записи начального адреса (О или Г) к содержимому счетчика

адреса 5 соответствующего блока 1, 2 вьщеления каналов добавляется единипа при нулевом признаке или в него записывается начальный адрес с регистрт 3 при единичном признаке.

Признак записи начального адреса блока памяти 7 определяет границы массивов в блоке памяти для каждого блока 1,2 вьщеления каналов. Для организации массивов каждого блока 1,2 выделения каналов в регистры 3 записываются начальные адреса массивов.

В последнем слове каждого массива оперативного запоминающего устройства содержится признак записи начального адреса, по которому начальный адрес с регистра 9 переписывается в счетчик адреса 5. В остальных словах массива признак отсутствует (равен ну.то), и к содержимому счетчика адреса 5 при выборке слов из оперативного запоминающего устройства доба ляется единица.

С каждым поступлением канального импульса осуществляется сравнение номера канального импульса с блока приема информации 6 и содержимого регистра фазы 3 всех блоков выделения каналов 1,2. При равенстве номера канального импульса и фазы, записанной в регистре фазы 3 любого блока выделения каналов, срабатывает соответствующий блок сравнения 4 и устройство производит вьщеление номера информационного канала аналогично описанному выще.

Если число градаций частот опроса будет равно

числу блоков выделения каналов, то для выделения

К информационных каналов потребуется К

ячеек оперативного запоминающего устройства, что

намного меньще, чем в известном устройстве.

Применение предлагаемого устройства значительно сокращает объем оперативного запоминающего устройства.

Формула изобретения

Устройство для селекции информационных

каналов, содержащее блок приема информации, соединенный с первым входом основного блока вьщеления каналов, вьшолненного в виде последовательно соединенных регистра фазы, блока сравнения и счетчика адреса канала, и блок памяти,

соединенный с вторым входом основного блока вьщеления каналов, отличающееся тем, что, с целью упрощения устройства путем уменьшения числа ячеек блока памяти, введены сумматор, регистры начального адреса и п дополнительных

блоков вьщеления каналов, входы которых соединены с соответствующими входами основного блока вьщеления каналов, при зтом выходы основного и дополнительных блоков выделения каналов через сумматор подключены к блоку памяти, дополнительный выход которого подключен к третьим входам основного и дополнительных блоков выделения каналов, а каждый из регист-. ров начального адреса соединен с счетчиком адреса канала соответствующего блока выделения каналов, к дополиительному входу регистра фазы которого подключен выход блока сравнения. Источники информаиии, принятые во внимание ри экспертизе: 1. Авторское свидетельство СССР N 213934, и.Кл Н 04 J 3/08,1968. 2. Авторское свидетельство СССР № 489232. М. Юе. Н 04 J 3/00,1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок выделения каналов для устройства ввода информации | 1980 |

|

SU882005A1 |

| Устройство для селекции информационных каналов | 1982 |

|

SU1062903A1 |

| Устройство для формирования адреса | 1978 |

|

SU742939A1 |

| Устройство для выбора и идентификацииизМЕРиТЕльНыХ КАНАлОВ | 1979 |

|

SU843309A1 |

| Устройство передачи и приема информации для интегрированной кольцевой сети связи | 1990 |

|

SU1734241A1 |

| Устройство избирательного вызова и передачи кодограмм | 1983 |

|

SU1136326A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1510009A1 |

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1434495A1 |

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

Авторы

Даты

1977-05-25—Публикация

1975-07-03—Подача