сл

со

Изобретение относится к вычислительной технике и может быть использовано в блоках буферной памяти для устройств приемо-передачи данных по уплотненной линии связи, а также в устройствах автоматического установления соединений в системах автоматической коммутации.

Цель изобретения - расширение области применения за счет формирования текущих адресов для заданных областей буферной памяти.

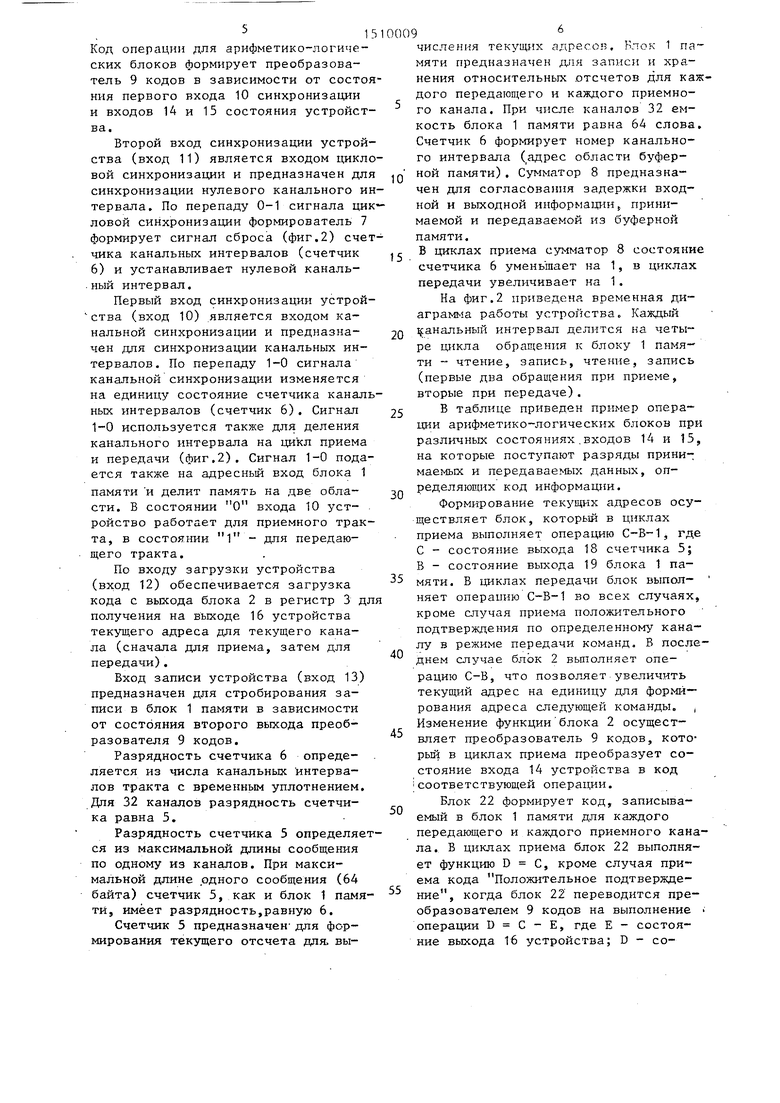

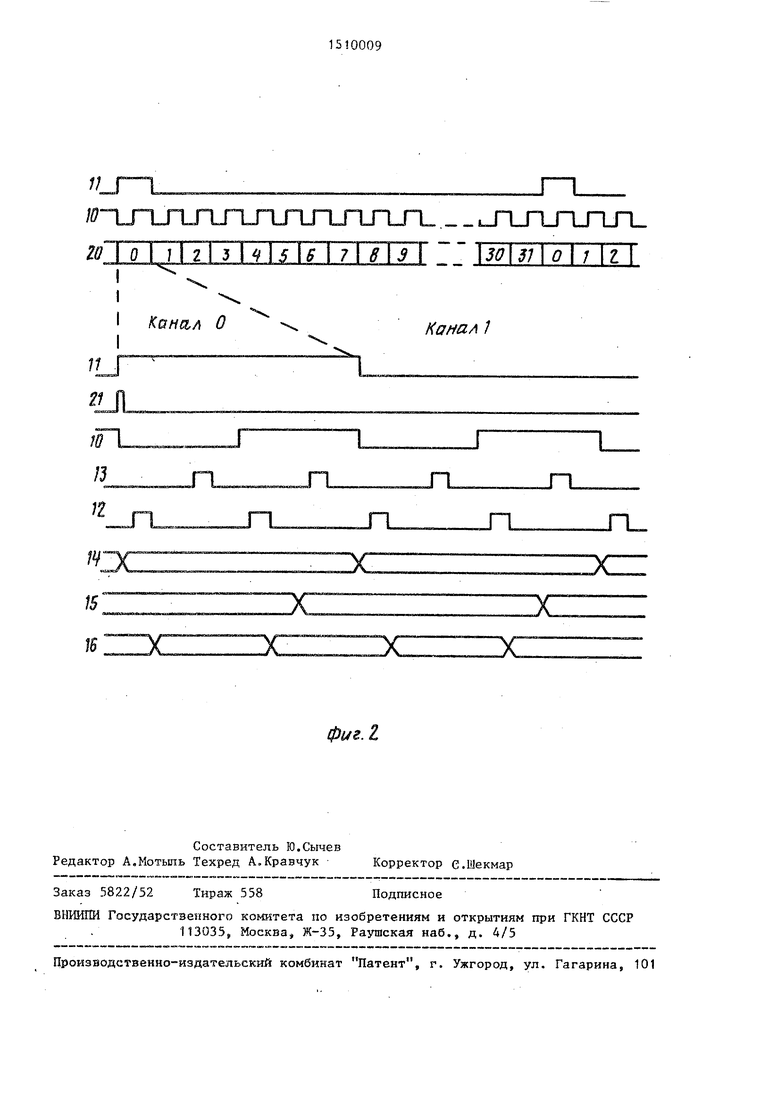

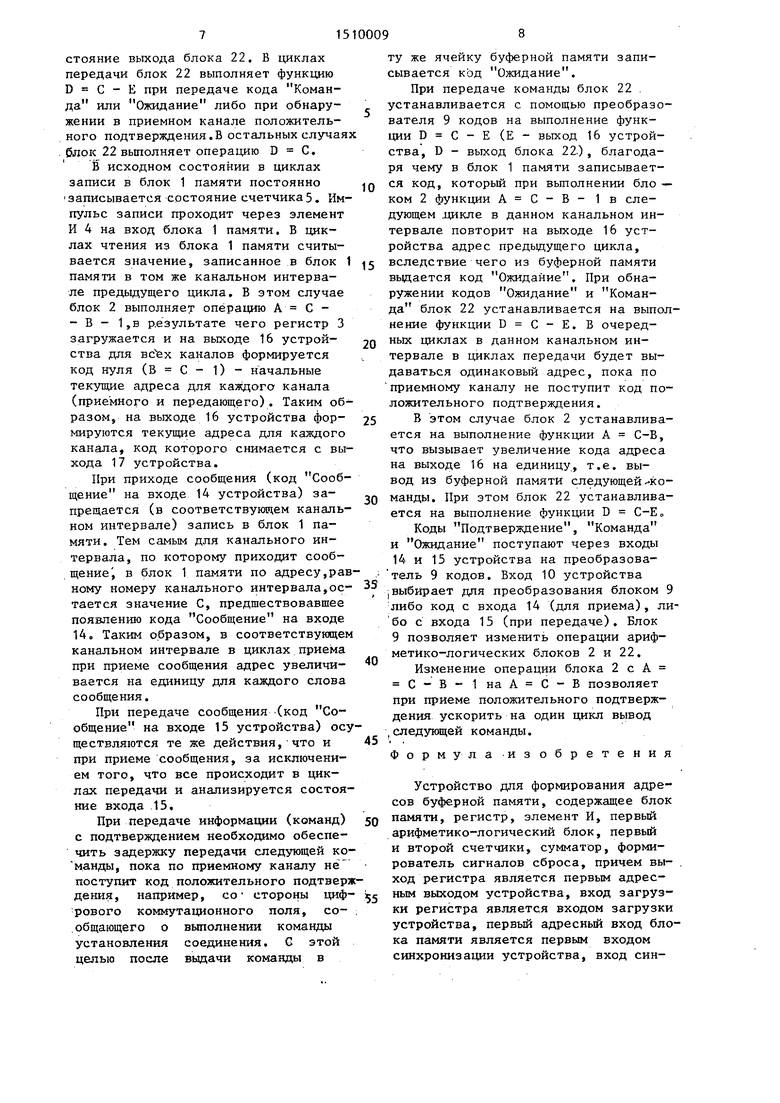

На фиг.1 изображена блок-схема устройства; на фиг.2 - временная диаграмма работы устройства.

Устройство (фиг.1) содержит блок 1 памяти, первый арифметико-логический блок 2, регистр 3, элемент И 4 первый .5 и второй 6 счетчики, фор- мирователь 7 сигналов сброса, сумматор 8, преобразователь 9 кодов,

первый 10 и второй 11 входы синхронизации, вход 12 загрузки, вход 13 записи, первый 14 и второй 15 входы состояния, первый 16 и второй 17 выходы устройства, выход 18 счетчика 5, выход 19 блока памяти, выход 20 счетчика 6, выход 21 формирователя 7, второй арифметико-логический блок 22.

Устройство предназначено для формирования адресов для буферной памяти устройств приема-передачи данных по линии,связи с временным уплотнением каналов, в частности, по ИКМ-трактам в цифровых АТС. ИКМ-трак представляет собой линию передаваемых и линию принимаемых данных, по которым соответственно передается и принимается информация по 32 каналам. В каждом канальном интервале передается (по передающему тракту) и принимается (по- приемному тракту) одно слово данных.

В каждом канале может приниматьс (по приемномз тракту) и передаваться (по передающему тракту) одно слово данных.

В каждом канале может приниматься (по приемному тракту) и передаваться (по передающему тракту) сообщение. Устройство обеспечивает уп-. равление приемом или передачей по каждому каналу пакета слов сообщени либо .без подтверждения, либо с под- тверж,цением по каждому слову сооб- щен1-1я, Последний режим может быть использован в устройствах автомати0

5

0

5

0

5

0

5

0

5

ческого установления соединений для обеспечения автоматической посылки команд для управления коммутацией через цифровое коммутационное поле с подтверждением по каждомй команде.

Прием и передача информации может осуществляться параллельно по всем каналам. Для возможности одновременного приема сообщений по каждому каналу и их записи в буферную память и .передачи сообщений из буферной памяти необходимо хранить и выдавать текущие адреса буферной памяти для каждого из 32 каналов (передающих и приемных), При этом при передаче или приеме слов сообщений без подтверждений необходимо обеспечить по соответствующим каналам последовательное увеличение адреса на единицу в каждом цикле. При переда-- че с подтверждением необходимо увеличивать адрес по соответствующему каналу лишь при обнаружении подтверждения по приемному каналу. Эти функции выполняет предлагаемое устройство.

Поскольку сообщения принимаются и передаются не одновременно, текущие адреса для областей буферной памяти, соответствующих разным канальным интервалам, будут различными. В устройстве имеется первый счетчик 5, формирующий текущие отсчеты, а начальные отсчеты для каждого канального интервала записываются и хранятся в блоке 1 памяти. Первьй арифметико-логический блок 2 обеспечивает формирование текущего адреса путем некоторой операции над состоянием первого счетчика 5 и содержи- MbiM блока 1 памяти. Номер канального интервала (адрес области буферной памяти) формируется вторым счетчиком 5.

Таким образом, устройство вы- п олняет функцию 2К счетчиков, где К - число канальных интервалов, поскольку адреса формируются как для приема, так и для передачи. Благодаря ис- пользова:нию относительных отсчетов обеспечивается периодическая самоинициализация текущих адресов, что .повышает надежность устройства.

Второй арифметико-логический блок 22 предназначен для вычисления кода, записываемого в блок 1 памяти в режиме передачи с подтверждением по каждому переданному слову сообщения.

Код операции для арифметико-логических блоков формирует преобразователь 9 кодов в зависимости от состояния первого входа 10 синхронизации и входов 14 и 15 состояния устройства.

Второй вход синхронизации устройства (вход 11) является входом цикловой синхронизации и предназначен для синхронизации нулевого канального интервала. По перепаду 0-1 сигнала цикловой синхронизации формирователь 7 формирует сигнал сброса (фиг.2) счетчика канальных интервалов (счетчик 6) и устанавливает нулевой каналь- .ный интервал.

Первый вход синхронизации устрой- ства (вход 10) является входом канальной синхронизации и предназначен для синхронизации канальных интервалов. По перепаду 1-0 сигнала канальной синхронизации изменяется на единицу состояние счетчика канальных интервалов (счетчик 6). Сигнал 1-0 используется также для деления канального интервала на цикл приема и передачи (фиг.2). Сигнал 1-0 подается также на адресньй вход блока 1 памяти и делит память на две области. В состоянии О входа 10 уст- ройство работает для приемного тракта, в состоянии 1 - для передающего тракта.

По входу загрузки устройства (вход 12) обеспечивается загрузка кода с выхода блока 2 в регистр 3 дл получения на выходе 16 устройства текущего адреса для текущего канала (сначала для приема, затем для передачи).

Вход записи устройства (вход 13) предназначен для стробирования записи в блок 1 памяти в зависимости от состояния второго выхода преобразователя 9 кодов.

Разрядность счетчика 6 определяется из числа канальных интервалов тракта с временным уплотнением. Для 32 каналов разрядность счетчика равна 5,

Разрядность счетчика 5 определяется из максимальной длины сообщения по одному из каналов. При максимальной длине одного сообщения (64 байта) счетчик 5, как и блок 1 памяти, имеет разрядность,равную 6.

Счетчик 5 предназначен- для формирования текущего отсчета для. вы5

числения текуищх адресов. Блок 1 памяти предназначен дая записи и хранения относительных отсчетов для каждого передающего и каждого приемно- го канала. При числе каналов 32 емкость блока 1 памяти равна 64 слова. Счетчик 6 формирует номер канального интервала (адрес области буферQ ной памяти) . Сумматор 8 предназначен для согласова)1ия задержки входной и выходной информаи ии принимаемой и передаваемой из буферной памяти.

В циклах приема сумматор 8 состояние счетчика 6 уменьшает на 1, в циклах передачи увеличивает на 1.

На фиг.2 приведена временная диаграмма работы устройства. Каждый

Q анальный интервал делится на четыре цикла обращения к блоку 1 памяти - чтение, запись, чтение, запись (первые два обращения при приеме, вторые при передаче).

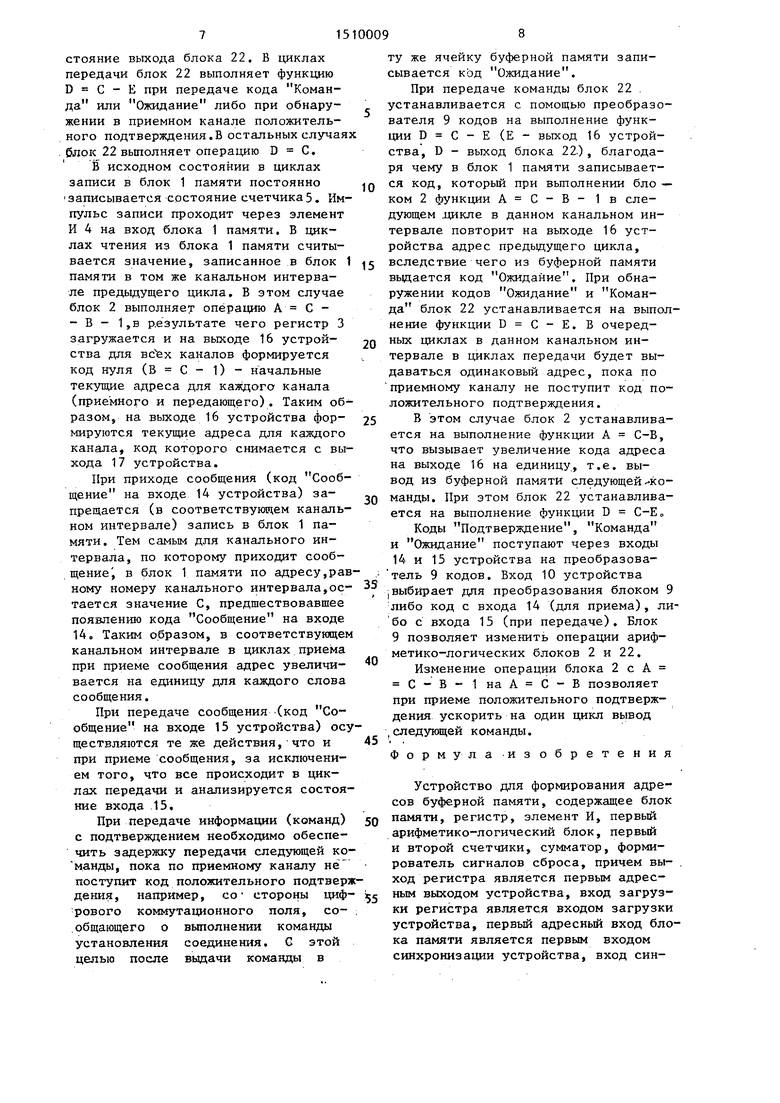

5 В таблице приведен пример операции арифметико-логических блоков при различных состояниях.входов 14 и 15, на которые постз пают разряды принимаемых и передаваемых данных, оп- ределяюпщх код информации.

Формирование текущих адресов осуществляет блок, который в циклах приема выполняет операцию С-В-1, где С - состояние выхода 18 счетчика 5; В - состояние выхода 19 блока 1 па5 мяти. В циклах передачи блок выпол- няет операцию С-В-1 во всех случаях, кроме случая приема положительного подтверждения по определенному каналу в режиме передачи команд. В последнем случае блок 2 выполняет операцию С-В, что позволяет увеличить текущий адрес на единицу для формирования адреса следующей команды. , Изменение функции блока 2 осуществляет преобразователь 9 кодов, который в циклах приема преобразует состояние входа 14 устройства в код соответствующей операции.

Блок 22 формирует код, записываемый в блок 1 памяти для каждого передающего и каждого приемного канала. В циклах приема блок 22 выполняет функцию D С, кроме случая приема кода Положительное подтвержде- ние, когда блок 22 переводится преобразователем 9 кодов на выполнение операции D С - Е, где Е - состояние выхода 16 устройства; D - со0

5

0

стояние выхода блока 22. В циклах передачи блок 22 выполняет функцию D С - Е при передаче кода Команда или Ожидание либо при обнаружении в приемном канале положительного подтверждения .В остальных случая блок 22 выполняет операцию D С. В исходном состоянии в циклах записи в блок 1 памяти постоянно записывается состояние счетчика 5. Импульс записи проходит через элемент И А на вход блока 1 памяти, В циклах чтения из блока 1 памяти считывается значение, записанное в блок 1 памяти в том же канальном интервале предьщущего цикла, В этом случае блок 2 выполняет операцию А С - - В - 1,в результате чего регистр 3 загружается и на выходе 16 устрой- ства для Bc fex каналов формируется код нуля (В С - 1) - начальные текущие адреса для каждого канала (приемного и передающего), Таким образом, на выходе 16 устройства фор- мируются текущие адреса для каждого канала, код которого снимается с выхода 17 устройства.

При приходе сообщения (код Сообщение на входе 14 устройства) за- прещается (в соответствующем канальном интервале) запись в блок 1 памяти. Тем самым для канального интервала, по которому приходит сообщение , в блок 1 памяти по адресу,рав ному номеру канального интервала,ос- тается значение С, предшествовавшее появлению кода Сообщение на входе 14. Таким образом, в соответствующем канальном интервале в циклах приема при приеме сообщения адрес увеличи- вается на единицу для каждого слова сообщения.

При передаче сообщения (код Сообщение на входе 15 устройства) осуществляются те же действия, что и при приеме сообщения, за исключением того, что все происходит в циклах передачи и анализируется состояние входа 15,

При передаче информации (команд) с подтверждением необходимо обеспечить задержку передачи следующей ко- манды, пока по приемному каналу не поступит код положительного подтверждения, например, со стороны циф- рового коммутационного поля, со- .общающего о выполнении команды установления соединения. G этой целью после выдачи команды в

0

Q 5

-. . S

5

0 j

ту же ячейку буферной памяти записывается код Ожидание.

При передаче команды блок 22 . устанавливается с помощью преобразователя 9 кодов на выполнение функции D С - Е (Е - выход 16 устройства, D - выход блока 22.) , благодаря чему в блок 1 памяти записывается код, который при вьшолнении бло - ком 2 функции А С - В - 1 в следующем .цикле в данном канальном интервале повторит на выходе 16 устройства адрес предыдущего цикла, вследствие чего из буферной памяти вьщается код Ожидание. При обнаружении кодов Ожидание и Команда блок 22 устанавливается на выполнение функции D С - Е. В очередных циклах в данном канальном интервале в циклах передачи будет выдаваться одинаковый адрес, пока по приемному каналу не поступит код положительного подтверждения.

В этом случае блок 2 устанавливается на выполнение функции А С-В, что вызывает увеличение кода адреса на выходе 16 на единицу, т.е. вывод из буферной памяти следующей ко- манды. При этом блок 22 устанавливается на выполнение функции D С-Е

Коды Подтверждение, Команда и Ожидание поступают через входы 14 и 15 устройства на преобразова- тель 9 кодов. Вход 10 устройства выбирает дпя преобразования блоком 9 либо код с входа 14 (для приема), ли- бо с входа 15 (при передаче). Блок 9 позволяет изменить операции арифметико-логических блоков 2 и 22.

Изменение операции блока 2 с А С-В-1наА С-В позволяет при приеме положительного подтверждения ускорить на один цикл вывод |Следукщей команды.

Формула -изобретения

Устройство для формирования адресов буферной памяти, содержащее блок памяти, регистр, элемент И, первый арифметико-логический блок, первый и второй счетчики, сумматор, формирователь сигналов сброса, причем выход регистра является первым адресным выходом устройства, вход загрузки регистра является входом загрузки устройства, первый адресный вход блока памяти является первым входом синхронизации устройства, вход син91510

хронизации первого счетчика соединен с входом формирователя сигналов сброса и является вторым входом синхронизации устройства, выход формирова- теля сигналов сброса соединен с входом установки второго счетчика, выходы которого соединены с входами первой группы сумматора, входы второй группы которого подключены к первому входу синхронизации устройства и входу синхронизации второго счетчика, выходы сумматора соединены с адресными входами группы блока памяти и являются вторым адресным вьпсо- дом устройства, первый вход элемента И является входом записи-чтения устройства, вькод элемента И соединен с входом записи-чтения блока памяны с информационными входами первой группы первого арифметико-логического блока, информационные входы второй группы которого подключены к выходам блока памяти, выходы первого арифметико-логического блока соединены с входами регистра, о т л и

5

0

5

10

чающееся тем, что, с целью расширения области применения устройства за счет формирования текущих адресов для заданных областей буферной памяти, в него введены второй арифметико-логи шский блок и преобразователь кодов, причем первый вход синхронизации устройства соединен с управляющим входом преобразователя кодов, входы первой и второй групп состояния которого являются соответствующими входами устройства, выходы первой группы преобразователя кодов подключены к управляющим входам первого и второго арифметико-логических блоков, второй вькод преобразователя кодов подключен к второму входу элемента И, выходы первого счетчика соединены с информационными входами первой группы второго арифметико-логического блока, выходы которого соединены с информационными входами блока памяти, выходы регистра соединены с информационными входами второй группы второго арифметико-логического б:1ока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1434495A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для формирования адресов буферной памяти | 1987 |

|

SU1587581A1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

Изобретение относится к вычислительной технике и может быть использовано в блоках буферной памяти. Цель изобретения - расширение области применения устройства за счет формирования текущих адресов для заданных областей буферной памяти. Устройство содержит блок 1 памяти, первый арифметико-логический блок 2, регистр 3, элемент И 4, счетчики 5, 6, формирователь 7 сигналов сброса, сумматор 8, преобразователь кодов 9, второй арифметико-логический блок 22. Данные устройство предназначено для формирования адресов буферной памяти в устройствах приема и передачи данных по уплотненной линии связи с временным уплотнением каналов. Тракт с временным уплотнением представляет собой две линии: линию передаваемых и линию принимаемых данных, по которым соответственно передается и принимается информация по нескольким каналам. В каждом канальном интервале передается и принимается одно слово данных. 2 ил., 1 табл.

Примечание, Х- произвольное состояние.

/ njnjTjajnjnjTTLnj Lj-Lnj-LTLTb

I Канал 0 I

фиг. I

Составитель Ю.Сычев Редактор А,Мотыль Техред А.Кравчук

Заказ 5822/52

Тираж 558

BHlffiltti Государстзенного ксьштета по изобретениям и открытиям при ГКНТ СССР 113035 Москва, К-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

гп

„ m

Канал 1

Корректор С.Шекмар

Подписное

| Устройство для формирования адреса буферной памяти | 1983 |

|

SU1126954A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1434495A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-09-23—Публикация

1986-10-27—Подача