4

СО

;о

СП

Изобретение относится к вычислительной технике и может быть использовано в блоках буферной памяти.

Цель изобретения - расширение области применения за счет формирования текущих адресов заданных областей буферной памяти.

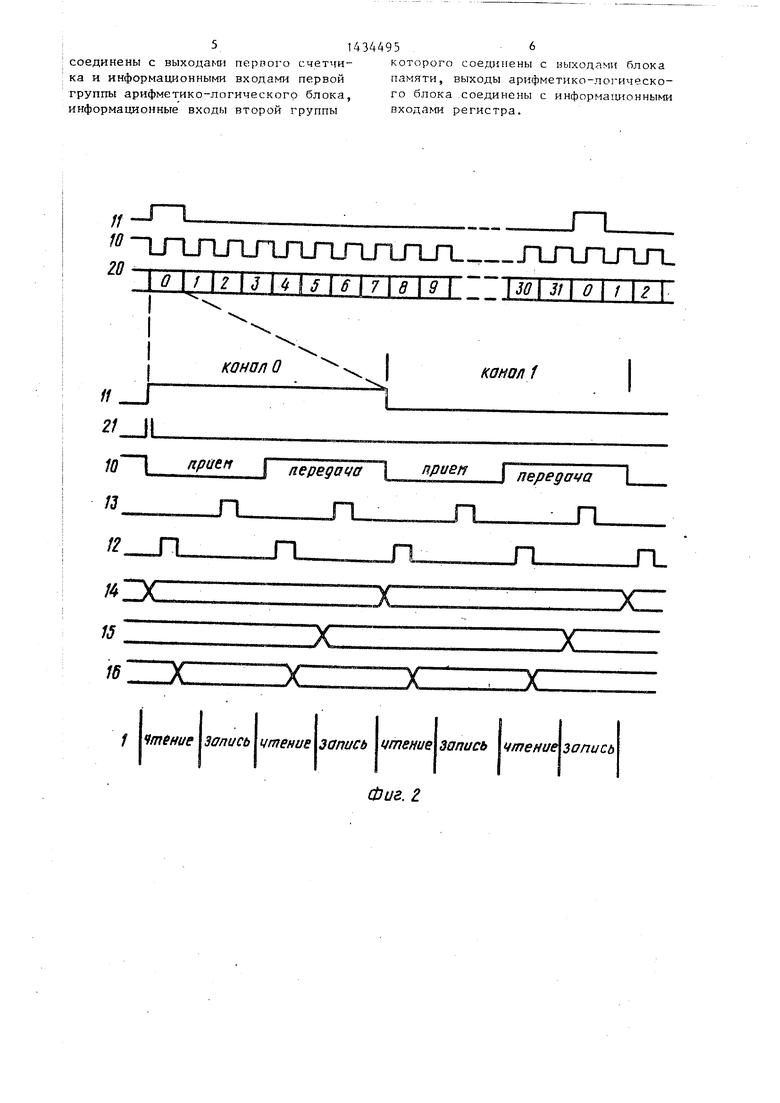

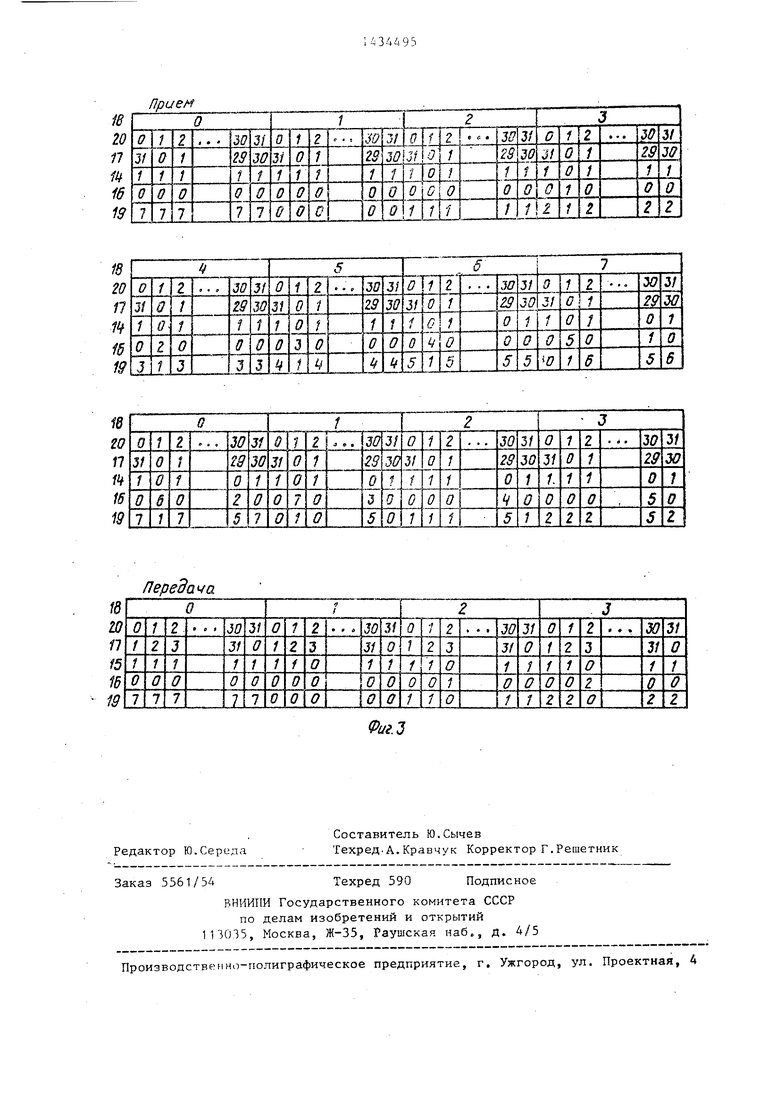

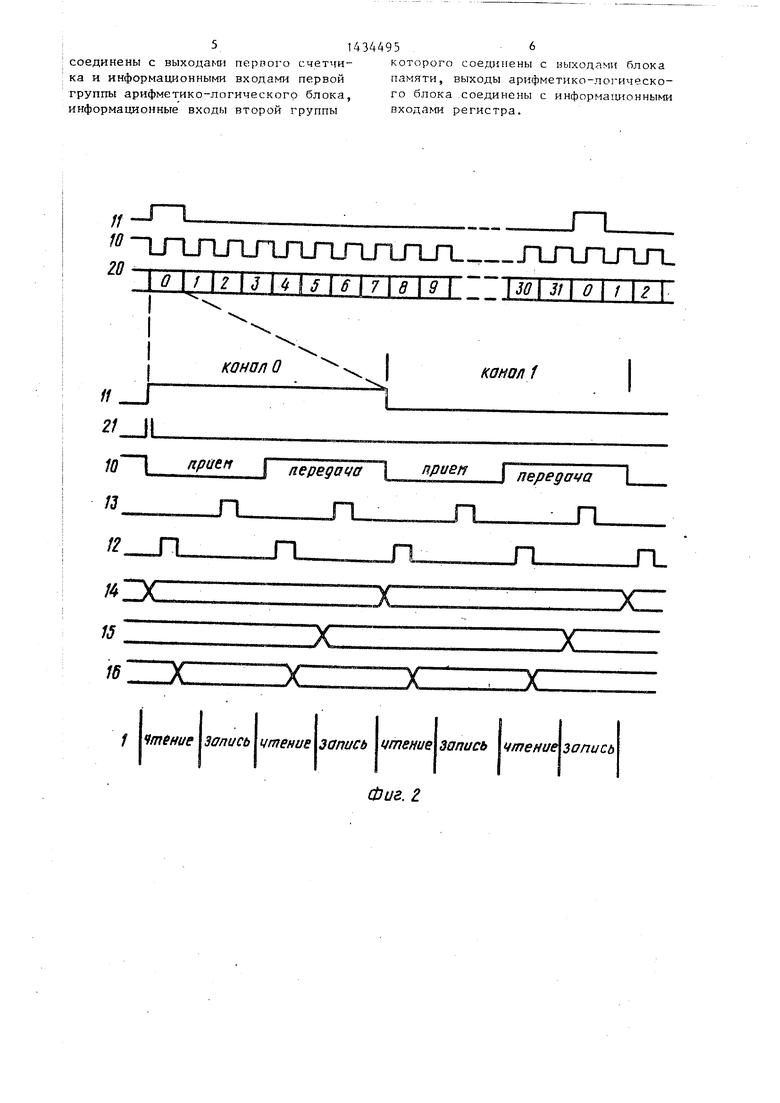

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - временная диаграмма работы устройства; на фиг. 3 - пример состояния устройства в процессе приема и передачи сообщений .

Устройство лля формирования адресов буферной памяти (фиг.1) содержит блок 1 памяти, арифметико-логический блок (АЛБ) 2,,регистр 3, элемент И 4, первый 5, второй 6 счетчики формирователь 7 сигналов сброса, сумматор 8, мультиплексор 9, первый и второй входы 10 и 1 синхронизагщи, вход 12 загрузки, вход 13 записи чтения, первый и второй нходы 14 и 15 разрешения, первый и второй адресные входы 16 и 17, выход 18 счетчика 5, выход 19 блока памяти 1, выход 20 счетчика 6, выход 21 формирователя 7.

.Первый вход синхронизации устройства (вход 10) является входом канальной синхронизации и предназначен для синхронизации канальных интервалов. По перепаду 1-0 сигнала канальной синхронизации изменяется на единицу состояние счетчика канальных интервалов (счетчик 6). ,

Второй вход синхронизации устройства (вход 11) является входом цикловой синхронизации и предназначен для синхронизации нулевого канального интервала. По перепаду 0-1 сигнала цикловой синхронизации .формирователь 7 формирует сигнал сброса (фиг. 2) счетчика канальных интерйалов (счетчик 6

По входу загрузки устройства (вход 12) обеспечивается загрузка с выхода 2 в регистр 3 для.получения на выходе 16 устройства текущего адреса для тёку1цего канала (сначала для приема, затем для передачи). Вход записи чтения устройства (вход 13) предназначен для стробиро- вания записи в блок 1 памяти в зависимости от состояния входов разрешения: от состояния первого входа разрешения (вход 14) в цикле приема и второго входа разрешения (вход 15) в цикле передачи. Выбор входного сигнала осуществляет м льтиплексор 9.

344952

Разрядность счетчика 6 определяется из цикла канальных интервалов тракта с временным уплотнением. Дпя 32 ка калов разрядность счетчика равна 3.

Разрядность счетчика 5 определяется максимальной длиной сообщения по одному из каналов. При максимальной

Q длине сообщения восьми слов счетчик 5 как и блок 1 памяти имеет разряд- ность равную трем.

Счетчик 5 предназначен для формирования текущего отсчета для вьмисле15 ния ААБ 2 текущих адресов. Блок 1 памяти предназначен для записи и хранения отсчетов Д.ЛЯ каждого передающего и каждого приемного канала. При числе каналов 32 емкость блока 1 памяти

20 равна 64 слова, причем разрядность слова зависит от максимальной длины сообщения. Формирование текущего адреса осуществляет АЛБ 2, который выполняет onepaijjiro С - В - 1 , где С 25 состояние выхода 18 счетчика 5 (текущего отсчета); В - состояние вько- да 19 блок 1 памяти. Счетчик 6 формирует номер канального интервала (адрес области буферной памяти). Сумма30 тор 8 предназначен для согласования входной и выходной информации, принимаемой и передаваемой из буферной памяти. В циклах приема состояния счетчика 6 сумматор 8 уменьшает на 1,

ос в цикле передачи увеличивает на 1.

Каждый канальный интервал делится на четыре цикла обращения к блоку 1 памяти: чтение, запись, чтение, запись. Первые два обращения при прие40 ме сообщения, вторые два - при передаче сообщения.

В исходном состоянии в циклах записи в блок 1 памяти постоянно записывается значение счетчика 5. Импульс д5 записи проходит через элемент И 4 на вход записи блока 1 памяти.

В циклах чтения из блока 1 памяти считывается значение, записанное в блок 1 памяти в том же канальнс м интервале предыдущего цикла. В результате для всех каналов на выходе АПД 2 формируется и загружается в регистр 3 код нуля - начальные текущие адреса для каждого канала как приемного, так и п.ередагацего, так как в данном случае В С - 1 .

При приходе слова сообщения,-о чем свидетельствует логический О в цикле приема на входе 14 устрпиства, за50

55

прещается (в соответствующем канальном интервале) запись в блок 1 памяти. Тем самым для данного канального интервала, по которому проходит сообщение, в блоке 1 памяти по соответствующему адресу, равному номеру канального интервала, будет записано значение С, предшествовавшее появлению сигнала на входе 14. В результате разница между текущим состоянием счетчика 5 и состоянием на выходе блока 1 памяти в соответствуюгцем канальном интервале будет увеличиваться на 1, что объясняется постоянным значение В для данного канального интервала, вследствие запрета записи и изменение значения С в начале каждого цикла. Таким образом на входе 16 устройства формируется текущий адрес для соответствующего канального интервала.

Сообщение представляет собой последовательность слов сообщений, вызывающих появление О на входе 14

ном интервале. Появление слова сообщения в нулевом канале (О на входе 14 ) вызывает запрет записи в блок 1 памяти, вследствие чего состояние выходу 19 блока 1 памлти в данном канальном интервале не изменяется, а состояние выхода 16 устройства увеличивается на 1 поскольку состояние выхода 18 продолжает увеличиваться.

В цикле передачи работа устройства отличается только тем, что о соот ношении информирует сигнал на входе 15.

Формула изобретения

Устройство для формирования адресов буферной памяти, содержащее блок памяти, мультиплексор, регистр и элемент И, причем выход регистра является первым адресным выходом устройства, вход загрузки регистра является входом загрузки устройства, первый

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов буферной памяти | 1986 |

|

SU1510009A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для формирования адресов буферной памяти | 1987 |

|

SU1587581A1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

Изобретение относится к вычислительной технике и используется в блоках буферной памяти. Цель изобретения - расширение области применения за счет формирования текущих адресов для заданных областей буферной памяти . Устройство содержит блок памяти 1, арифметико-логический блок 2, регистр 3, элемент И 4, первый 5 и второй 6 счетчики, формирователь 7, сумматор 8, мультиплексор 9. Устройство предназначено для формирования адресов для буферной памяти устройств приемопередачи данных по линии связи с временным уплотнением каналов. Тракт с временным уплотнением представляет собой две линии - линию передаваемых и линию принимаемых данных, по которым соответственно передается и принимается информация по нескольким каналам. В каждом канальном интервале передается или принимается одно слово данных. 3 ил. G (Л с

30

35

устройства для принимаемого и на вхо- pi, адресный вход блока памяти является де 15 для передаваемого сообщения в первым входом синхронизации устрой- соответствующем канальном интервале. ства, отличающееся Пропадания слова сообщения в соответ- ствунлцем канальном интервале -вызывает запись по соответствукщему адресу блока 1 памяти текущего отсчета, т.е. инициализацию текущего адреса.

При передачи сообщений в циклах передачи анализируется состояние входа 15. На фиг. 3 приведен пример состояния устройства в процессе приема и передачи сообщения. Счетчик 5 устройства не инициализируется и посто- янно каждый цикл изменяет свое состояние (выход 18). На выходе 20 счетчика 6 формируются входы канальных интервалов. На выходе 17 сумматора 8 имеем уменьшенный на 1 код канального интервала и циклах приема (с целью согласования задержки входной информации, поскольку входное слово данных будет полностью принято в конце данного канального интервала) и увеличенный на 1 код канального интервала в циклах передачи (поскольку слово данного канального интервала будет передаваться с задержкой на один канальный интервал).

При отсутствии на входе слова сообщения (1 на входе 14 устройства)

40

45

50

ства, отличающееся тем, что, с целью расширения области применения за счет формирования текущих адресов для заданных областей буферной па.мяти, в него введены арифмети- ческо-логический блок, первый и второй счетчики, сумматор, формирователь сигналов сброса, причем вход синхронизации первого счетчика соединен с входом формирователя сигналов, сброса и является вторым входом синхронизации устройства, выход формирователя сигналов сброса соединен с входом установки второго счетчика,выходы которого соединены с входами первой группы сумматора, входы второй г;руппы которого подключены к первому входу синхронизации устройства и входу синхрониза- 1ЩИ второго счетчика, выходы сумматора соединены с адресными входами груп пы блока памяти и являются вторым адресным выходом устройства, первый вход синхронизации устройства соединен с управляющим входом мультиплексора, первый и второй информационные входы которого являются первым и вторым входами разрешения работы устройства, выход мультиплексора подключен к второму входу элемента И, первый

юстоянно осуществляется запись в блок вход которого является входом записи/ 1 памяти состояния счетчика 5. Резуль- чтения устройства, выход элемента И тат операции АЛУ 2 дает на выходе 16 устройства код нуля в каждом каняльсоединен с входом записи/чтения блока памяти, информационные входы которосо

0

5

i, адресный вход блока памяти является первым входом синхронизации устрой- ства, отличающееся

0

5

0

ства, отличающееся тем, что, с целью расширения области применения за счет формирования текущих адресов для заданных областей буферной па.мяти, в него введены арифмети- ческо-логический блок, первый и второй счетчики, сумматор, формирователь сигналов сброса, причем вход синхронизации первого счетчика соединен с входом формирователя сигналов, сброса и является вторым входом синхронизации устройства, выход формирователя сигналов сброса соединен с входом установки второго счетчика,выходы которого соединены с входами первой группы сумматора, входы второй г;руппы которого подключены к первому входу синхронизации устройства и входу синхрониза- 1ЩИ второго счетчика, выходы сумматора соединены с адресными входами группы блока памяти и являются вторым адресным выходом устройства, первый вход синхронизации устройства соединен с управляющим входом мультиплексора, первый и второй информационные входы которого являются первым и вторым входами разрешения работы устройства, выход мультиплексора подключен к второму входу элемента И, первый

вход которого является входом записи/ чтения устройства, выход элемента И

соединен с входом записи/чтения блока памяти, информационные входы которосо

514344956

соединены с выходами перпого счетчи- которого соединены с выходами блока ка и информационными входами первой группы арифметико-логического блока, информационные входы второй группы

памяти, выходы арифметико-логическо го блока .соединены с информационным входами регистра.

//

10

го

-J-L

ГП

njHJlJlJlJlJ JTnJlJT.„JlJTrLTLTL

ШIIlIПIL lmJL JJLLIII

канал О

11 21

JI

fiepeQQf/ff npueff nepeggt/a - П П, ПП

П

Чтение

зачлись

i msHus

запись

которого соединены с выходами блока

памяти, выходы арифметико-логического блока .соединены с информационными входами регистра.

ГП

каноп 1

гт

Л.

чтение

запись

чтение

запись

Фиг. Z

18 20 11

ik 16

19

Передача

| Устройство для выборки адресовиз блОКОВ пАМяТи | 1974 |

|

SU813504A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адреса буферной памяти | 1983 |

|

SU1126954A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-30—Публикация

1986-10-02—Подача