1

Изобретение относится к вычислительной технике и может быть использовано для ввода телеметрической информации в ЭВМ.

Известны устройства для формирования адреса информационного канала, содержащие память, регистры и коммутаторы, выполняющие функции выбора канала и формирования его адреса fl3.

Недостатком этих устройств является низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности является устройство для селекции информационных каналов и сопряжения канала с ЭВМ, содержащее блок оперативной памяти, выход которого соединен со входом регистра числа, счетчик канальных импульсов, соединенный с канальным и маркерным входами устройства, и декодирующую матрицу, в котором в качестве декодирующей матрицы использовано ОЗУ, первый выход которого через регистр фазы подключен к элементу сравнения, а второй является выходом устройства, причем маркерный вход устройства дополнительно соединен с установочными входами регистра фазы и счетчика

адреса выбираемого канала, выход которого соединен с -адресным входом ОЗУ, к второму входу элемента сравнения подключен выход счетчика канальных импульсов, а выход элента сравнения соединен с управляющим входом ОЗУ и счетным входом счетчика адреса выбираемого канала 2 j .

Недостаток этого устройства заклю10чается в низком быстродействии и большом объеме памяти при обслуг.ивании информационных каналов адресной структуры.

Цель изобретения - повышение бы15стродействия .

Поставленная цель достигается тем, что в устройство, содержащее блок памяти, соединенный управляющим входом с управляющим входом устрой20ства, а информационным выходом со входом регистра числа, введены регистр адреса, два дешифратора, сумматор, две группы элементов И и коммутатор, причем информационный и управляющий

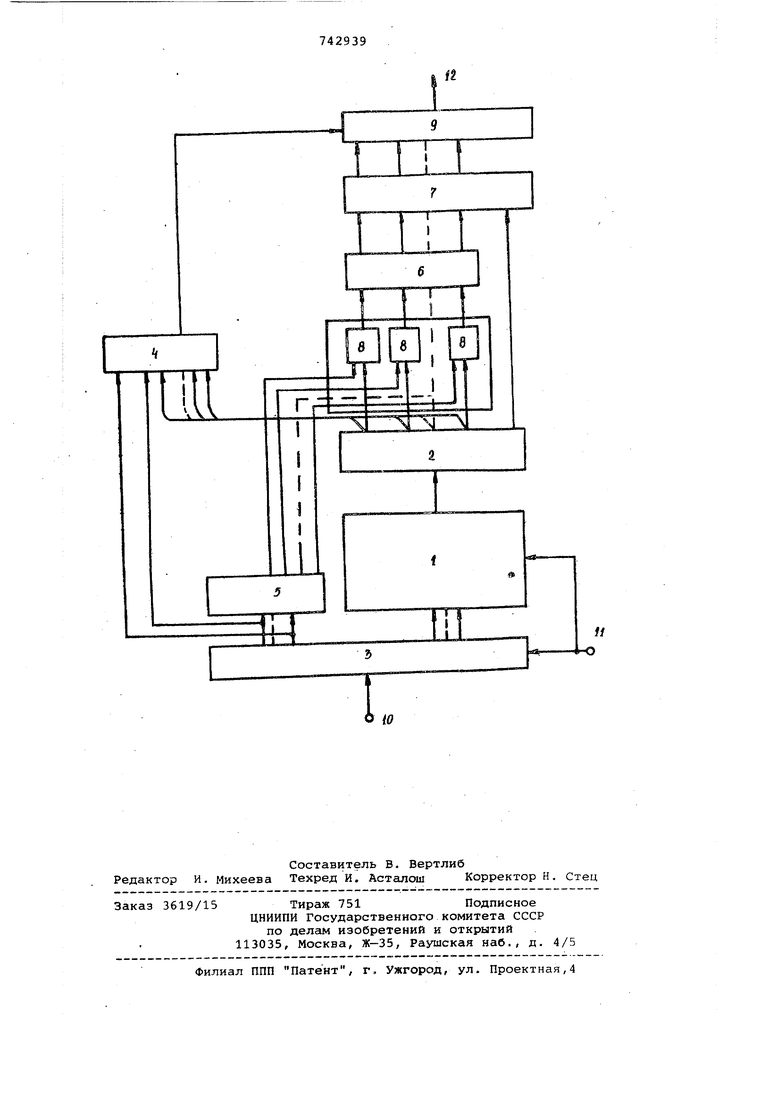

25 входы регистра числа подключены соответственно к адресному и управляющему входам устройства, выходы группы старших разрядов - к адресному входу блока памяти, а выходы группы млад30ших разрядов - к соответствуквдим Входам первой группы коммутатора и соответствующим входам первого дешиф ратора, выходы которого соединены с первыми входами соответствующих элементов И первой группы, вторые вхо4ы которых подключены к соответствующим выходам группы младших раэ|рядОв регистра числа, а выходы - чеТрез второй дешифратор к соответствуюощм разрядам первого входа сумматора, ;разряды второго входа которого соед|инены с соответствующими выходами ijpynrai старших разрядов регистра , а выходы - с первыми входами соофветствующих элементов И второй группы, выходы которых являются соответствующими выходами устройства а в|горые входы подключены к -соответствующим выходам коммутатора, входы Btdpoti группы которого соединены с соответствующими выходами группы мла;дших разрядов регистра числа. На чертеже представлена блок-схема устройства.Устройство содержит блок 1 памяти регистр 2 числа, регистр 3 адреса, кофлутатор 4 , дешифраторы 5 и б, сумма- ор 7, элементы 8 и 9 И первой и йторой групп, сщресный вход 10 уст ройства, управлякяций вход 11 устройства и выход 12 устройства. :Устройство работает следующим образом. .; Предположим, что требуется выбрать и сформировать адрес канала с номером 45 (101101) . При составлени программы общее количество инфо)мационных каналов 64 разбивается на 4 группы по 16 каналов. КаЗДая группа информационных каналов записы вается в одну строку блока 1 (16 яч1еек под номер канала и 6 ячеек под вт|о()ичный гщрес). Все 64 канала раз меадаются в 4 строках блока 1: в пер вdй строке каналы 0-15, во второй - 16-31, в третьей - 32-47, в четвертой - 48-63. Пусть, например, необходимо прои водить селекцию и формирование гщре сфв следующих информационных канало 2,5,6,7,10,12,13,14,33,36,37,42,43, 44,45,46, причем адресом второго кднала является число 1, пятого -f 2, шестого - 3,..., четырнадцатого 8, тридцать третьего - 9,..., сорок пятого - 15, сорок шестого - 16. Пр этом выбор и посылка адресов в кана лЫ, номера которых не указаны, запр щается. Признаком их селекции являете единица, записанная в ячейки блока 1, которые соответствуют пере численным каналам. Начальный вторич ный адрес в первой строке присваива ется каналу 2. Формирование вторичНых адресов для других каналов, нах 4ящихся в этой строке, происходит йутем суммирования начального адрес G количеством единиц, расположенных в левой части строки, от признака и елекции. Например, если 2-му каналу рисвоить вторичный адрес 000000 (все нули), то 5-му каналу будет рисвоен адрес 100000, а 14-му каалу - 111000 (здесь и ниже ладшие разряды слева). При аписи программы для формиования вторичных адресов каналов, предназначенных для селекции и расположенных во 2-ой, 3-ей или 4-ой строках блока 1, необходимо учитывать количество вторичных адресов, присвоенных в предыдущих строках. Для информационных каналов первой строки, подлежащих селекции, формируется восемь вторичных адресов 000000 111000, следовательно в третьей строке начальный вторичный адрес должен быть больше, чем восемь вторичных адресов первой строки (000100). Этот начальный вторичный адрес присввивается 33-му информационному каналу. Вторичные адреса следующих информационных каналов, подлежащих селекции, формируются аналогично каналам первой строки блока 1. Шестиразрядное адресное слово поступает на регистр 3. Выходная информация регистра 3 делится на четы- ре. млалших разряда (1011) и два старших (01) , последние являются гщресом чтения блока 1. По этому адресу считывается информация 3-ей строки, переписывается в регистр 2. Младшие разряды поступают на дешифратор 5, на выходе которого формируется унитарный код, с количеством-единиц, равный числу, представленному младшими разрядами в двоичном коде. В данном случае это число равно 13 и, соответственно, на выходе дешифратора 5 формируется унитарный код из 13 единиц, который управляет работой элементов 8 И, на другие входы которых поступает информация с регистра 2. Так как унитарный код имеет 13 единиц, что разрешает работу только 13 элементам 8 И, то на вход дешифратора 6 поступает только. 13 младших разрядов (левых) регистра 2, содержащих 6 единиц. Дешифратор 6 приводит эту информацию к двоичному коду (ОНО) . Для формирования вторичного ёодреса информ1ация, полученная с выхода дешифратора 6, складывается на сумматоре 7 с начальным вторичным адресом, находящимся в регистре 2. Сформированный на сумматоре 7 вторичный адрес поступает на входы элементов 9 И, на другие входы которых поступает признак выбора данного канала. Коммутатор 4 устанавливается в позицию, указанную младшими разряда1ми регистра 3 (в данном случае 13-я позиция) и коммутирует соответствующий этой позиции разряд числа, содержащегося в регистре 2, на свой выход. Если состояние разряда на этой позиции - единица, то открываются элементы 9 И и число, содержащееся в сумматоре 7, поступает на выход 12 устройства. Если жр на данной позиции числа стоит нуль, то элементы И блокируются вплоть до поступления в регистр 3 нового адреса. В рассматриваемом примере в триНсщцатом разряде числа регистра 2 стоит единичный символ, следовательно на выход 12 поступает код числа 15 (01110) .

Таким образом, устройство обеспечивает выбор кансша и формирование его с1дреса при сравнительно мал объемах памяти и высоком быстродействии ..

Формула изобретения

Устройство для формирования адреса, содержащее блох памяти,соединенный управляющим входом с управляющим входом устройства, а информационным выходом со входом регистра числа, отличающееся тем,что, с целью повышения быстродействия, в него введены регистр адреса, два дешифратора, сумматор, две группы элементов И и коммутатор, причем ин{формационный и управлякхдий входы регистра числа подключены соответветственно к адресному и управляющему входс1м устройства, выходы группы

старших разрядов - к адресному входу блока памяти, а выходы группы младших разрядов - к соответствующим входам первой группы коммутатора и соответствующим входгш первого дешиф5 ратора выходы которого соединены с первыми входами .соответствующих элементов И первой группы, вторые входы которых подключены к соответствующим выходам группы младших 0 разрядов регистра числа, а выходы - через второй дешифратор к соответствукхцим разрядам первого входа сумматора, разряды второго входа которого соединены с соответствуюе пими выходами группы старших разрядов регистра числа, а выходы - с первыми входаАШ соответствующих элеl eHTOB И второй группы, выходы когорых являются соответствующими выхоцами устройства, а вторые входы

0 подключены к соответствующим выхоЙс1м ком йутатора, входы второй, груп|1ы которого соединены с соответствуюУШМИ выходё1ми группы младших разряioB регистра числа.

Источники информации, финятые во внимание при экспертизу1. Авторское свидетельство СССР №463968, кл. G06 F 9/20 1973. 0 2. Авторское свидетельство СССР 489232, кл. Н 04 J 3/00, 1974 прототипУ

т

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для селекции информацион-НыХ КАНАлОВ | 1978 |

|

SU809607A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

М

11

Авторы

Даты

1980-06-25—Публикация

1978-01-23—Подача