BOM, лноо во втором такте машины, чем обеспечивается гибкость микропрограмм.

Вместе с тем существуют алгоритмы, микрооперации в которых, в силу осевой симметрии самих задач, обладают симметрией в том смысле, что в одних и тех лее тактах машины выполняются нри работе ио одному алгоритму четные, а но другому- нечетные микрооперации, и наоборот, и качестве примера можно привести алгоритмы геометрической интерпретации при управлении двухкоордииатными объектами, иаиример, графопостроительными устройствами типа координатограф, электроннолучевыми установками и трубками, фотонаборными установками; задачи топологического проектирования фотошаблонов БИС, операции над матрицами, тригонометрическими фуикциями -и т. п.

Б этих случаях для каждого алгоритма или его фрагмента необходимо отводить свой массив памяти, в то время как один алгоритм может быть достаточно просто преобразован в другой путем замены в нем четных микроопераций на нечетные или наоборот. Отсутствие возможиости выполнять такие иреобразоваиия в ходе выполнения микропрограммы приводит к увеличению -оборудования и усложнению микропрограммного устройства управления.

Целью предлагаемого микропрограммного устройства управления является упрош,ение устройства. Для этого в иредлагаемое устройство введеиы триггер признака симметрии, элемент И, п элементов неравнозначности, информационный регистр дополнительно содержит разряд признака симметрии, причем выход разряда признака симметрии информационного регистра соединен с иервым входом элемента И, второй вход которого подключен к третьему выходу генератора тактовых импульсов, выход элемента И подключен к счетному входу триггера признака симметрии, входы установки в «1 н «О которого соединены соответственно с первым и вторым входами устройства, выход триггера признака симметрии подключен к второму входу каждого управляющего элемента И, выход каждого управляющего элемента И подключен к первому входу одноименного элемента неравнозначности, второй вход каждого элемента неравнозначности соединен с выходом младшего разряда соответствующего поля информационного регистра, выход каждого элемента неравнозначности соединен с соответствующим входом одноименного дешифратора кода операции.

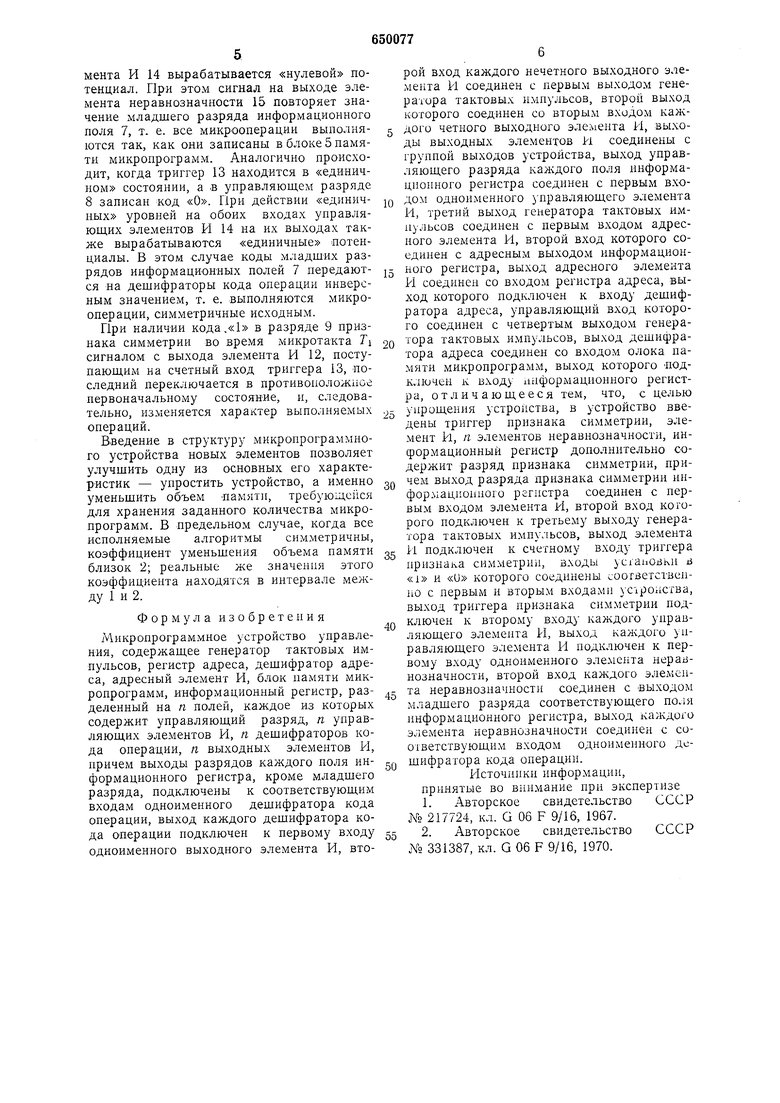

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит генератор 1 тактовых импульсов, адресный элемент И 2, регистр адреса 3, дешифратор адреса 4, блок 5 памяти микропрограммы, информационный регистр 6, разделенный на п полей 7

с управляющим разрядом 8, разряд 9 признака симметрии, дешифраторы 10 кода операции, выходные элемеиты И И, элемент И 12, триггер 13 признака симметрии, управляющие элементы И 14, элементы неравнозначности 15, первый вход 16 устройства, второй вход Г/ устройства, группа выходов 18 устройства.

При составлении микропрограмм симметричные микрооперации кодируются таким образом, что коды их отличаются лишь в одном, например, младшем разряде. Так, четные микрооперации кодируются «нулем в младшем разряде, а нечетные - . «единицей. В управляющие разряды я полей информационного регистра для симметричных микроопераций записывается код «1, для несимметричных - «О. Наконец, в разряд признака симметрии 9 информационного регистра записывается код «1, когда в процессе выполнения микропрограммы требуется осуществить переход от нечетных микроонераций к четным (или наоборот). Таким образом, каждая микропрограмма

5 составляется и реализуется в блоке 5 памяти микропрограмм для одного из двух симметричных алгоритмов или их фрагментов. Предлагаемое устройство работает следующим образом.

0 Генератор 1 вырабатывает четыре правильные (непересекающиеся во времени) последовательности сигнала, так что четыре следующих друг за другом сигнала /1-7 из каждой серии составляют один

5 такт устройства. Во время микротакта TI код адреса из информационного регистра 6 через адресные элементы И 2 переписывается в регистр адреса 3. Во время микротакта Га происходят опрос дешифратора

0 адреса 4 и чтение из блока 5 памяти микропрограмм соответствующего слова, которое заносится в информационный регистр 6. Коды с выхода информационного регистра поступают на соответствующие дешифраторы кода операции 10, сигналы с выхода которых передаются на один из входов выходных элементов 11. На другие входы выходных элементов И поступают тактирующие сигналы Гз и Т, причем каждым из

0 этих сигналов объединяются группы вентилей тех полей, микрооперации которых совместимы и могут выполняться в одном микротакте. Младший разряд кода каждого информационного поля 7 поступает на дешифратор 10 через элемент неравнозначности 15, на другой вход которого подается сигнал с выхода управляющего элемента И 14, реализующего совпадение «единичных уровней на выходах триггера 13 и соответствующего управляющего разряда 8.

Допустим, что триггер 13 сигналом на Шине 17 был установлен в «нулевое состояние, тогда на выходе управляющего элемента И 14 вырабатывается «нулевой потенциал. При этом сигнал на выходе элемента неравнозначности 15 повторяет значение младшего разряда информационного поля 7, т. е. все микрооперации выполняются так, как они записаны в блоке 5 памяти микропрограмм. Аналогично происходит, когда триггер 13 находится в «единичном состоянии, а в управляющем разряде 8 записан код «О. При действии «единичных уровней на обоих входах управляющих элементов И 14 на их выходах также вырабатываются «единичные потенциалы. В этом случае коды младших разрядов информационных полей 7 передаются на дещифраторы кода операции инверсным значением, т. е. выполняются микрооперации, симметричные исходным.

При наличии кода.«1 в разряде 9 признака симметрии во время микротакта TI сигналом с выхода элемента И 12, поступающим на счетный вход триггера 13, последний переключается в противоиоложиое первоначальному состояние, и, следовательно, изменяется характер выполняемых операций.

Введение в структуру микропрограммного устройства новых элемептов позволяет улучшить одну из основных его характеристик - упростить устройство, а именно уменьшить объем ламятп, требующейся для хранения заданного количества микропрограмм. В предельном случае, когда все исполняемые алгоритмы симметричны, коэффициент уменьшения объема памяти близок 2; реальные же значения этого коэффициента находятся в интервале между 1 п 2.

Формула изобретения

jvlnKponporpaMMHoe устройство управления, содержащее генератор тактовых импульсов, регистр адреса, дешифратор адреса, адресный элемент И, блок памяти микропрограмм, информационный регистр, разделенный на п полей, каждое из которых содержит управляющий разряд, я управляющих элементов И, я дешифраторов кода операции, п выходных элементов И, нричем выходы разрядов каждого поля информационного регистра, кроме младщего разряда, подключены к соответствующим входам одноименного дещифратора кода операции, выход каждого дешифратора кода операции подключен к первому входу одноименного выходного элемента И, второй вход каждого нечетного выходного элемента И соединен с первым выходом генератора тактовых нмнульсов, второй выход которого соединен со вторым входом кал дого четного выходного элел1ента И, выходы выходных элементов И соединены с группой выходов устройства, выход управляющего разряда каждого поля информационного регистра соединен с первым входом одноименного управляющего элемента И, третий выход генератора тактовых импульсов соединен с первым входом адресного элемента И, второй вход которого соединен с адресным выходом информационкого регистра, выход адресного элемента И соединен со входом регистра адреса, выход которого подключен к входу дешифратора адреса, управляющий вход которого соедипен с четвертым выходом генератора тактовых импульсов, выход дещифратора адреса соединен со входом олока памяти микропрограмм, выход которого подключен к входу 11нформацпопного регистра, отличающееся тем, что, с целью

упрощения устройства, в устройство введены триггер прпзнака симметрии, элемент И, я элементов неравнозначности, информационный регистр дополнительно содержит разряд признака симметрии, причем выход разряда признака спхмметрин информационного регистра соединен с первым входом элемента И, второй вход когорого подключен к третьему выходу генератора тактовых импульсов, выход элемента

И подключен к счетному входу триггера признака симметрии, входы усхааовкп в «1 и «и которого соединены соответственно с первым и вторым входами ycipo.icTBa, выход триггера признака симметрии подключен к второму входу каждого унравляющего элемента И, выход управляющего элемента И подключен к первому входу одноименного элемента неравнозначности, второй вход каждого элемепта неравнозначности соединен с выходом младщего разряда соответствующего поля информационного регистра, выход кал-сдого элемента неравнозначности соединен с соответствующим входом одноименного дешифратора кода операции.

Источпикп информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 217724, кл. G 06 F 9/16, 1967.

2. Авторское свидетельство СССР 331387, кл. G 06 F 9/16, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267413A1 |

Авторы

Даты

1979-02-28—Публикация

1976-08-01—Подача