1

Изобретение относится к автоматике.

Известны распределители на га каналов, содержащие в каждом канале триггер с раздельными входами и схему управления, а также шины начальной установки и импульсов тактирования 1.

Известен также распределитель на п каналов, содержащий в каждом канале триггер с раздельными входами и элемент НЕТ, шину начальной установки распределителя, которая подключена к еди-ничному входу триггера первого канала и к первым нулевым входам триггеров последующих каналов, шину входных импульсов, которая подключена к входам запрета элементов НЕТ, первый вход разрешения каждого из которых соединен с единичным выходом триггера своего канала, а выход - с единичным входом триггера последующего канала, дополнительный триггер с раздельными входами и первый дополнительный элемент НЕТ,, вход запрета которого соединен с шиной входных импульсов, а первый вход разрешения - с единичным выходом дополнительного триггера, единичный вход которого подключен к выходу элемента НЕТ последнего канала, а нервый нулевой вход - к шине начальной установки распределителя, причем выходы распределителя соединены с единичными выходами канальных триггеров, шину такто15ЫХ импульсов 2.

Целью изобретения является повышение помехозащищенности распределителя на п каналов.

Это достигается тем, что в распределителе на га каналов, содержащем в каждом канале триггеры с раздельными входами и элемент НЕТ, шину начальной установки распределителя, которая подключена к единичному входу триггера первого канала и к первым нулевым входам триггеров последующих каналов, шину входных импульсов, которая подключена к входам запрета элементов НЕТ. первый вход разрешения каждого из которых соединен с единичным выходом триггера своего канала, а выход - с единичным входом триггера носледующего канала, дополнительный триггер с раздельными входами и первый дополнительный элемент НЕТ, вход запрета которого соединен с шиной входных имнульсов, а первый вход разрещения - с единичным выходом дополнительного триггера, единичный вход которого нодключен к выходу элемента НЕТ последнего канала, а первый нулевой вход - к шине начальной установкп распределителя,

причем выходы распределителя соединены с единичны.ми выходами канальных триггеров, а также второй ii третий дополнительные элементы НЕТ, управляющнй триггер, («+)разрядный делитель частоты, элемент И, нпшу тактовых импульсов и шину синхронизации.

единичный выход дополнительного триггера подключен к входу разрешения второго дополнительного элемента НЕТ, вход запрета которого Соединен с шиной синхронизации, а выход-с шиной начальной установки распределителя, с входом начальной установки делителя частоты и единичным входом управляюшего триггера, счетный вход которого соединен С шиной тактовых импульсов, нулевой вход - с выходом элемента НЕТ последнего канала, а единичный выход - со счетным входом делителя частоты и с входом запрета третьего дополнительного элемента НЕТ, вход разрешения которого подключен к выходу элемента И, а выход к шине входных импульсов, единичные выходы делителя частоты соединены с с входами элемента И, выход которого соединен с вторыми входами, разрешения канальных и первого дополнительного элементов НЕТ, выход элемента НЕТ первого канала подключен к нулевому входу триггера этого канала, выход каждого из элементов НЕТ последующих каналов соединен с вторым нулевым входом триггера своего канала, а выход первого дополнительного элемента НЕТ подключен к второму нулевому входу дополнительного триггера.

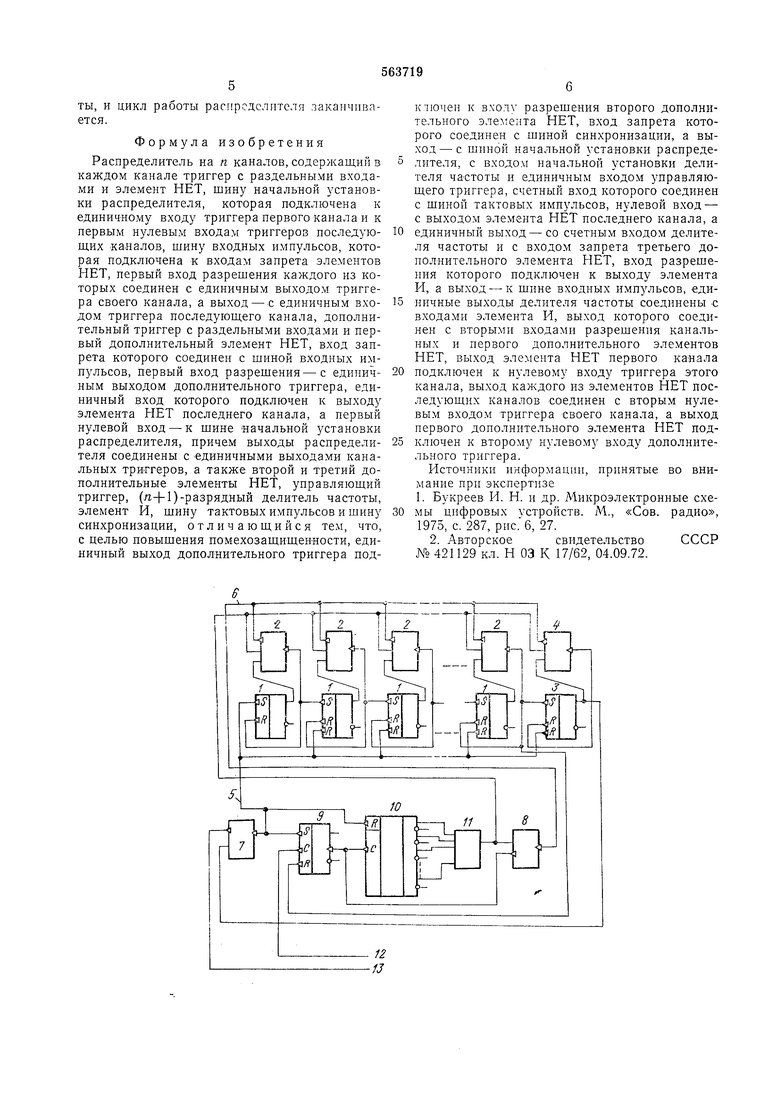

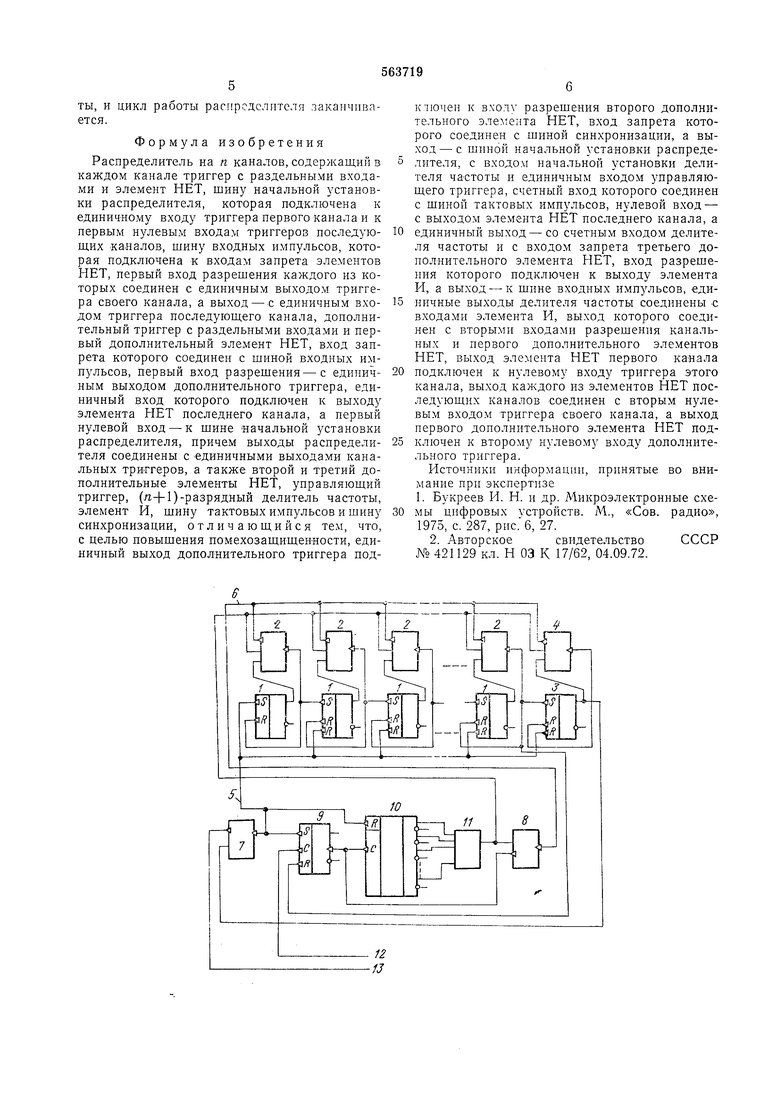

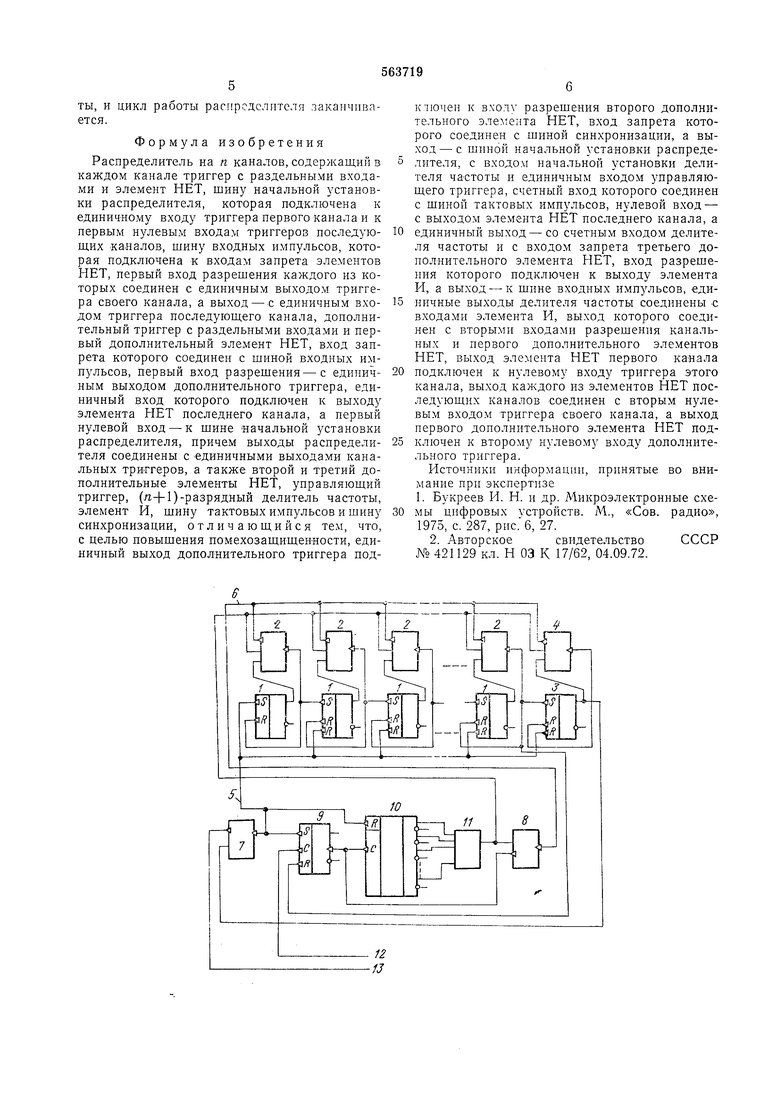

На чертеже представлена функциональная схема предлагаемого распределителя на п каналов.

Схема содержит капальный триггер 1 с раздельными входами, канальный элемент НЕТ 2, дополнительный триггер 3, первый дополнительный элемент НЕТ 4, шину 5 начальной установки распределителя, шину 6 входных импульсов, второй 7 и третий 8 дополнительные элементы НЕТ, управляюш,ий триггер 9, (n-fl)-разрядный делитель 10 частоты, элемент И И, шину 12 тактовых импульсов, шину 13 синхронизации.

Шина 5 начальной установки распределителя подключена к единичному входу триггера 1 первого канала и к первым нулевым входам триггеров 1 последуюпл.их каналов и дополнительного триггера 3. Шина 6 входных импульсов соединена с входами запрета канальных эле.ментов НЕТ 2 и входом запрета первого дополнительного элемента НЕТ 4. Первый вход разрешения каждого из канальных элементов НЕТ 2 подключен к единичному выходу триггера 1 своего канала, второй вход разрешения - к выходу элемента И II, а выход соединен с вторым нулевым входом триггера 1 своего канала и единичным входом триггера 1 последующего канала. Нервый вход разрешения первого дополнительного элемента НЕТ 4 соединен с единичным выходом дополнительного триггера 3, второй вход разрешения - с выходом элемента PI 11, а выход подключен к второму нулевому входу дополнительного триггера 3, единичный вход которого соединен с выходом элемента НЕТ 2 последнего канала. Выходы распределителя на п каналов соединены с единичными выходами ка-нальных триггеров I. Единичный выход дополнительного триггера 3 подключен к входу разрешения второго дополнительного элемента НЕТ 7, вход запрета которого соединен с шиной 13 синхронизации, а выход - с шиной 5 начальной установки распределителя, с единичным входом управляющего триггера 9 и с входом начальной установки делителя 10 частоты. Счетный вход управляющего триггера 9 соединен с

шиной 12 тактовых имульсов, нулевой вход- с выходом элемента НЕТ 2 последнего канала, а единичный выход - со счетным входом делителя 10 частоты и с входом запрета третьего дополнительного элемента НЕТ 8,

вход разрешения которого подключен к выходу элемента И 11, а выход - к шине 6 входных импульсов. Единичные выходы делителя 10 частоты соединены с входами элемента Н 11.

Распределитель на п каналов работает следующим образом.

На счетный вход управляющего триггера 9 по шине 12 тактовых импульсов непрерывно

поступают тактовые импульсы. Нри подаче сигнала по шине 13 синхронизации управляющий триггер 9 через второй дополнительный элемент НЕТ 7 переходит в единичное состояние, в результате чего тактовые импульсы начинают поступать на счетный вход делителя 10 частоты и на вход запрета третьего дополнительного элемента НЕТ 8. Одновременно по шине 5 начальной установки распределителя осуществляется установка канальных триггеров 1 в исходное состояние, а также установка делителя 10 частоты в исходное состояние. Вследствие этого триггер 1 первого канала переходит в единичное состояние, а триггеры 1 остальных каналов и дополнительный триггер 3 переходят в нулевое состояние. Нрп одновременном поступлении с единичных выходов делителя частоты единичных логических уровней на входы элемента И И на его выходе формируется единичный логический уровень, который подается на вход разрешения третьего донолнительного элемента НЕТ 8. В период наличия единичного логического уровня на входе разрешения третьего дополнительного элемента НЕТ 8 на шину 6 входных импульсов поступает тактовый импульс. Последний устанавливает триггер 1 второго канала в единичное состояние и переводит триггер 1 первого канала в нулевое состояние. С приходом очередного тактового импульса с выхода третьего дополнительного элемента НЕТ 8 в единичное состояние переходит триггер 1 третьего канала, а триггер 1 второго канала - в нулевое состояние и т. д. Единичный логический уровень с выхода элемента НЕТ 2 последнего канала устанавливает триггер 1 этого канала в нулевое состояние, а дополнительный триггер 3 - в единичное состояние. В результате прекращается поступление тактовых

импульсов на счетный вход делителя 10 часто

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления диаграммой направленности двумерных антенных решеток | 1990 |

|

SU1748215A1 |

| -Канальный кольцевой распределитель | 1976 |

|

SU604154A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Распределитель импульсов | 1978 |

|

SU809632A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДИАГРАММОЙ НАПРАВЛЕННОСТИ ДВУМЕРНЫХ АНТЕННЫХ РЕШЕТОК | 1991 |

|

RU2020670C1 |

| Распределитель сигналов на 10 каналов | 1977 |

|

SU660257A1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1444736A1 |

| Устройство для вычисления временных интервалов микропроцессорных систем | 1980 |

|

SU960781A1 |

Авторы

Даты

1977-06-30—Публикация

1976-02-20—Подача