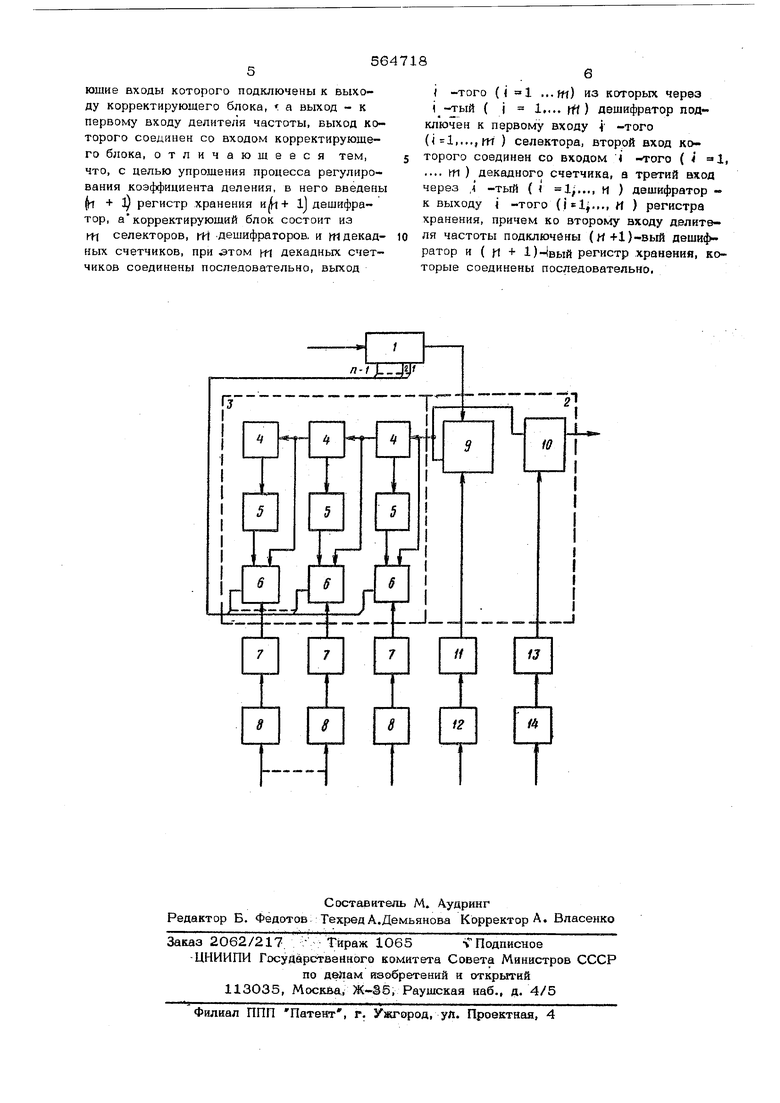

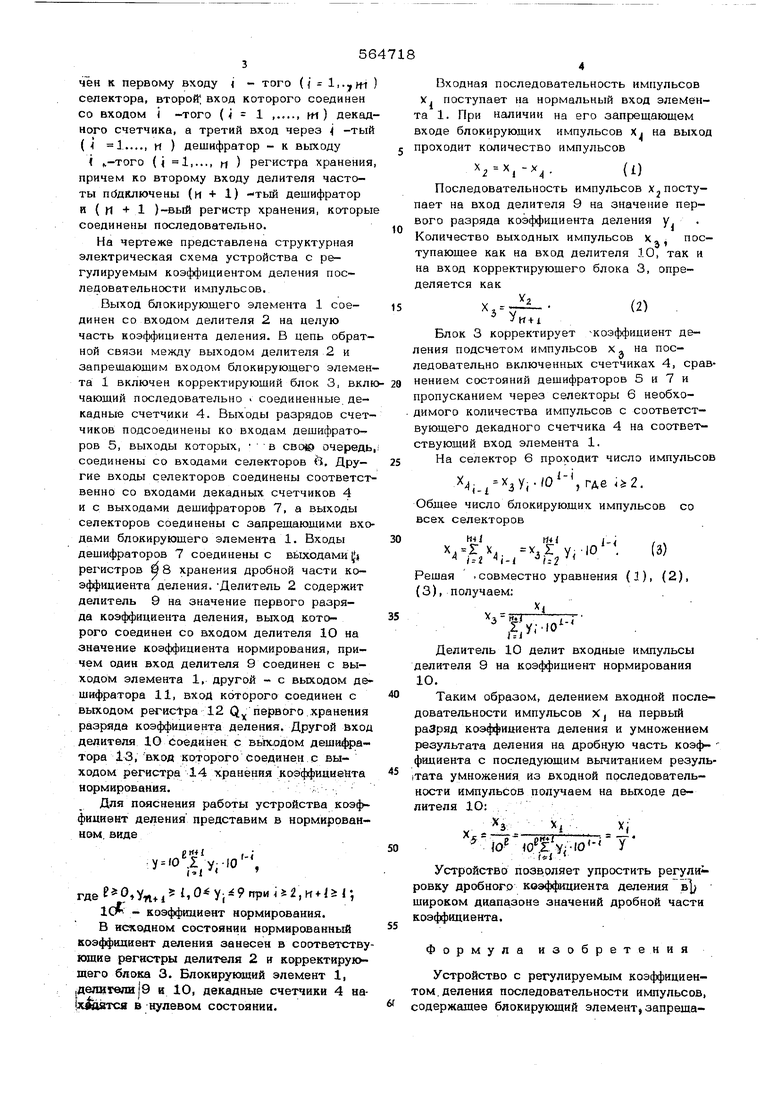

Изобретение относится к автоматике и цифровой вычислительной технике, может быть использовано в системах обработки информации и управления. Известно устройство с регулируемым коэффициентом деления последовательности импульсов, даюшее возможность получить дробный коэффициент деления. Оно содержит счетчик, элементы сравнения, управляемый регистр, элемент задержки и элемент запрета. Недостаток этого устройства - отсутствие возможности независимого регулирования целой и дробной частей коэффициента деления в широком диапазоне. Наиболее близко к предлагаемому устройство с регулируемым коэффициентом де ления последовательности импульсов, содержащее блокирующий элемент,, запрещающие входы которого подключены к выходу корректирующего блока, а выход - к первому входу делителя частоты, выход которого соединен со входом корректирующего блока. Это устройство позволяет устанавливать различные значения дробной части коэффициента деления. Однако такое регулирование в широком диапазоне значений дробной части коэффицие.1та очень сложно паза необходимсюти большого количества переключений селектора корректирующего блока. Цель изобретения - упрощение процесса регулирования коэффициента деления в широком диапазоне - достигается тем, что в устройство с регулируемым коэффициентом деления последовательности импульсов, содержащее блокирующий элемент, делитель на целую часть коэффициента деления и кор ректирующий блок в цепи обратной связи между выходом делителя и запрещающим входом блокирующего элемента, введены (и + 1) регистр хранения и(ц + 1)дешнфратор, а корректирующий блок состоит из /tt селекторов, ,ц дешифраторов и т декадных счетчиков; при этом w декадных счетчиков соединены последовательно, выход -того ( 1...., Ж ) из которых через t -{ыЯ ( 1 ..., и-1 ) дешифратор подклкьчен к первому входу i - того ({ l. селектора, второй вход которого соединен со входом i -того ( 1 ,.,.., ifi) декад ного счетчика, а третий вход через -тый ( 4 1 п ) дешифратор - к выходу ( -тoгo (i 1 rt ) регистра хранения причем ко второму входу делителя частоты подключены (и + 1) --тый дешифратор и {и + 1 )-вый регистр хранения, которы соединены последовательно. На чертеже представлена структурная электрическая схема устройства с регулируемым коэффициентом деления последовательности импульсов. Выход блокирующего элемента 1 соединен со входом делителя 2 на целую часть коэффициента деления. В цепь обратной связи между выходом делителя 2 и запрещающим входом блокирующего элемен та 1 включен корректирующий блок 3, вкл чающии последовательно соединенные декадные счетчики 4. Выходы разрядов счет чиков подсоединены ко входам дешифраторов 5, выходы которых, В CBCNS очередь соединены со входами селекторов И, Другие входы селекторов соединены соответст венно со входами декадных счетчиков 4 и с выходами дещифраторов 7, а выходы селекторов соединены с запрещающими вхо дами блокирующего элемента 1. Входы дешифраторов 7 соединены с вь1ходами| } регистров d 8 хранения дробной части коэффициента деления. -Делитель 2 содержит делитель 9 на значение первого разряда коэффициента деления, выход которого соединен со входом делителя 1О на значение коэффициента нормирования, причем один вход делителя 9 соединен с выходом элемента 1, другой - с выходом дешифратора 11, вход которого соединен с выходом регистра 12 Q первого.хранения разряда коэффициента деления. Другой вход делителя Ю Соединен с вьпс,адом дещифратора 13, вход которого соединен с выходом регистра 14 хранения коэффиаиейта нормирования. Для пояснения работы устройства коэф фициент деления представим в нормированном, виде РК41. ; .У Ю.,.10-, ,15г,О У1 9при; 2,, IG - коэффициент нормирования. В исходном состоянии нормированный коэффициент деления занесен в соответству ющие регистры делителя 2 и корректирукхщего блока 3. Блокирующий элемент 1, де,/вдгвлй|9 и 10, декадные счетчики 4 наix iSTCfl в нулевом состоянии. Входная последовательность импульсов X. поступает на нормальный вход элемента 1. При наличии на его запрещающем входе блокирующих импульсов Xi на выход проходит количество импульсов (i) Последовательность импульсов х поступает на вход делителя 9 на значение первого разряда коэффициента деления у Количество выходных импульсов х,, поступающее как на вход делителя 10, так и на вход корректирующего блока 3, определяется как Блок 3 корректирует - коэффициент деления подсчетом импульсов Х- на последовательно включенных счетчиках 4, сравнением состояний дешифраторов 5 и 7 и пропусканием через селекторы 6 необходимого количества импульсов с соответствующего декадного счетчика 4 на соответствующий вход элемента 1. На селектор 6 проходит число импульсов 1-i ;.ГзУг0 , где . л , V. (U Общее число блокирующих импульсов со всех селекторов t ttuii.j X.r Х. v,i: y.jO . hi i-t h2 Решая .совместно уравнения (J), (2), (3), получаем; ,i,y;.io Делитель 10 делит входные импульсы делителя 9 на коэффициент нормирования 10. Таким образом, делением входной последовательности импульсов Xj на первый разряд коэффициента деления и умножением результата деления на дробную часть коэф- фициента с последующим вычитанием резуль|тата умножения из входной последовательности импульсов получаем на выходе делителя 10: . Ху- . V, 5-к У;-10 10 Устройство позволяет упростить регулировку дробного коэффициента деления в) широком диапазоне значений дробной части коэффициента. Формула изобретения Устройство с регулируемым коэффициентом, деления последовательности импульсов, содержащее блокирующий элемент, запрещаюшие входы которого подключены к вычоду корректирующего блока, а выход - к первому входу делителя частоты, выход которого соединен со входом корректирующего блока, отличающееся тем, что, с целью упрощения процесса регулирования коэффициента деления, в него введены + З) регистр хранения к1п+ 1J дешифратор, акорректирующий блок состоит из щ селекторов. Hi -дешифрагоров, и m декадных счетчиков, при атом К1 декадных счетчиков соединены последовательно, выход

i -того (i 1 ...fft) из которых череэ ( j 1..., (ft) дешифратор подключен к первому входу | -того (-l,,..,ni ) селектора, второй вход которого соединен со входом -того ( i , .... m ) декадного счетчйка, а третий вход через ,4 -тый ( 1;..,, И ) дешифратор к выходу t -того (jelj.,,, Ц ) рЭГИСТрЭ

хранения, причем ко второму входу делителя частоты подключены (И+1)-вый дешифратор и ( }1 + 1)-цвый регистр хранения, которые соединены последовательно,

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с дробнымпЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU849493A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Цифровой частотомер | 1973 |

|

SU447637A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| ИЗМЕРИТЕЛЬ ОТНОСИТЕЛЬНЫХ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2001 |

|

RU2291452C2 |

| Делитель частоты с регулируемым коэффициентом деления | 1977 |

|

SU677108A1 |

| Множительное устройство | 1977 |

|

SU696453A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU786010A1 |

| ИЗМЕРИТЕЛЬ ОТНОСИТЕЛЬНЫХ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2017 |

|

RU2668951C1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

Авторы

Даты

1977-07-05—Публикация

1975-04-18—Подача