(54) ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый компаратор | 1979 |

|

SU773907A1 |

| Частотно-фазовый компаратор | 1974 |

|

SU484621A1 |

| ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР | 2011 |

|

RU2469461C1 |

| Частотно-фазовый компаратор | 1978 |

|

SU758478A2 |

| ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР | 2017 |

|

RU2647678C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 2010 |

|

RU2428785C1 |

| СПОСОБ НАПРАВЛЕННОЙ ЗАЩИТЫ ОТ ОДНОФАЗНОГО ЗАМЫКАНИЯ НА ЗЕМЛЮ В РАСПРЕДЕЛИТЕЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СЕТИ ПЕРЕМЕННОГО ТОКА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2303323C1 |

| Устройство для контроля качества материалов и изделий | 1988 |

|

SU1642367A1 |

| Устройство противоаварийной автоматики для восстановления частоты в энергосистеме | 1980 |

|

SU866646A1 |

| Фазовый компаратор | 1979 |

|

SU809483A1 |

1

Изобретение относится к радиотехнике и может использоваться в устройствах автоподстройки частоты и фазы, а также в устройствах для стабилизации и синхронизации скорости.

Известен частотно-фазовый компаратор п авторскому свидетельству N 484621, содержащий схемы И-НЕ, фазовый и два бло1шрующих тригг-эра, , причем входы фазового триггера подключены к источникам контролируемой и эталонной частоты, а также соединены с первыми входами двух схем И-НЕ, к вторым входам которых погн ключены соответственно единичный и нуле- вой выходы фазового триггера, а к выходам - первые входы блокировочг1ых триггеров, нулевые выходы которых соединены с их вторыми входами через схему И-НЕ, а единичные выходы - с первыми входами четвертой и пятой схем И-НЕ соответственно, при этом второй вход четвертой схемы соедшген с выходом пятойсхемы , второй вход которой подключен к нулевому выходу фазового триггера IJ.

Недостаток компаратора в отсутствии блокировки срабатывания третьей схемы И-НЕ, вследствие чего возможны повторные ложные срабатывания блокирующего триггера.

Цель изобретения - исключение ложных срабатываний блокирующего триггера.

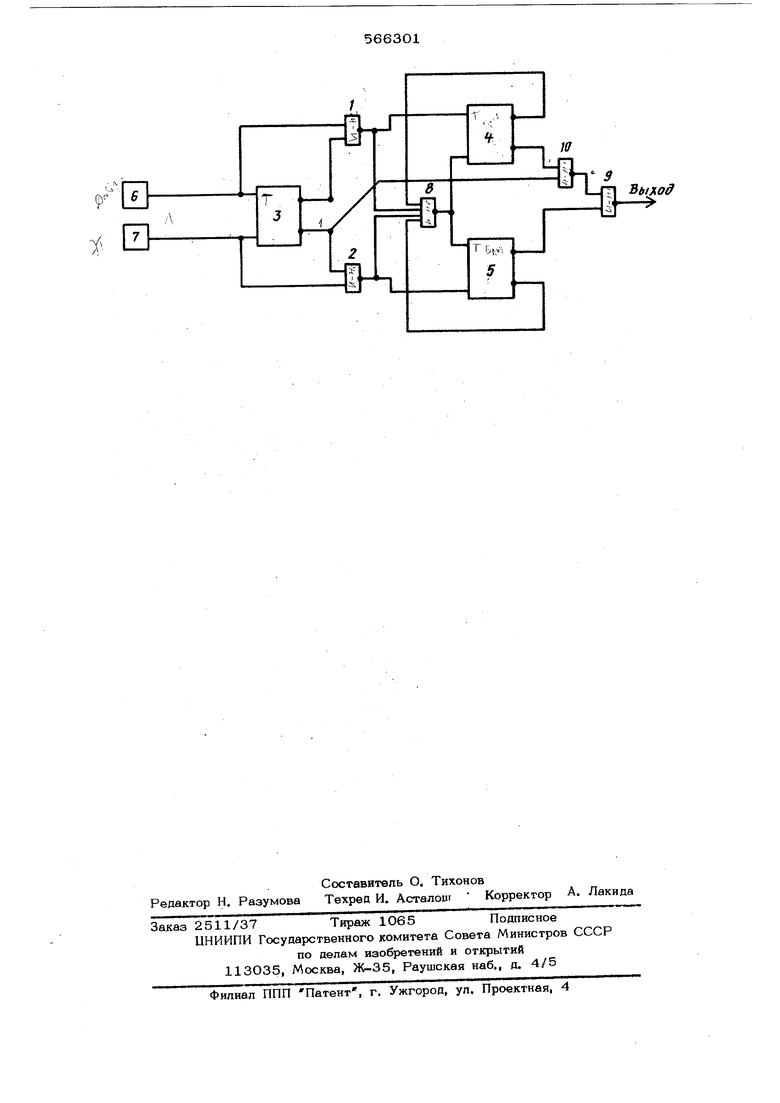

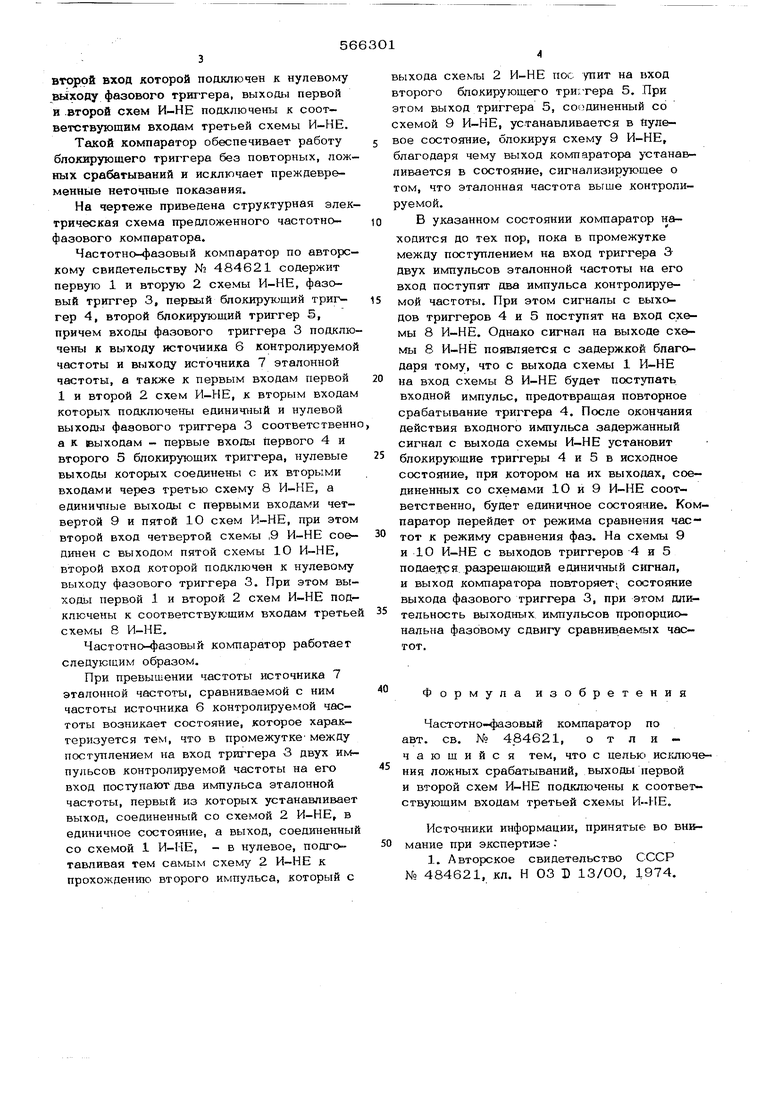

Для ЭТОГО в частотно-фазовом компараторе по авторскому свидетельству №484621 содержащем схемы И-НЕ, фазовый и два блокирующих триггера, в котором входы фазового триггера подключены к клеммам источников контролируемой и эталонной частоты, а также соединены с первыми входами двух схем И-НЕ, к вторым входам которых подключены соответственно еничный и нулевой выходы упомянутого фазового триггера, а к выходам - первые входы блокировочных триггеров, нулевые выходы которых соединены с их вторыми входами через схему И-НЕ, а единичные выходы соответственно - с первыми входами четвертой и пятой схем И/НЕ, при этом второй вход четвертой схемы И-НЕ соединен с выходом пятой схемы И-НЕ, второй вход которой подключен к нулевому ылходу фазового триггера, выходы первой и .второй схем И-НЕ подключены к соответствующим входам третьей схемы . TajKOfl компаратор обеспечивает работу блокирующего триггера без повторных, лож ных срабатываний и исключает преждевременные неточные показания. На чертеже приведена структурная элек трическая схема предложенного частотнофазового компаратора. Частотно-фазовый компаратор по авторскому свидетельству Na 484621 содержит первую 1 и вторую 2 схемы И-НЕ, фазовый триггер 3, первый блокирующий триг- гер 4, второй блокирующий триггер S, причем входы фазового триггера 3 подклю чены к выходу источника 6 контролируемой частоты и выходу источника 7 эталонной частоты, а также к первым входам первой 1 и второй 2 схем И-НЕ, к вторым входам которых подключены единичный и нулевой выходы фазового триггера 3 соответственн а к Выходам - первые входы первого 4 и второго 5 блокирующих триггера, нулевые выходы которых соединены с их вторыми входами через третью схему 8 И-НЕ, а единичные выходы с первыми входами четвертой 9 и пятой 10 схем И-НЕ, при этом второй вход четвертой схемы ,9 И-НЕ сое- динен с выходом пятой схемы 10 И-НЕ, второй вход которой подключен к нулевому выходу фазового триггера 3. При этом выходы первой 1 и второй 2 схем И-НЕ подключены к соответствующим входам третье схемы 8 И-НЕ. Частотно-фазовый компаратор работает следующим образом. При превышении частоты источника 7 эталонной частоты, сравниваемой с ним частоты 6 контролируемой частоты возникает состояние, которое характеризуется тем, что в промежутке между поступлением на вход триггера 3 двух импульсов контролируемой частоты на его вход поступают два импульса эталонной частоты, первый из которых устанавливает выход, соединенный со схемой 2 И-НЕ, в единичное состояние, а выход, соединенный со схемой 1 И-НЕ, - в нулевое, подготавливая тем самым схему 2 И-НЕ к прохождению второго импульса, который с ыхода схемы 2 И-НЕ пос упит на вход торого блокирующего три;-гера 5. При том выход триггера 5, соединенный со хемой 9 И-НЕ, устанавливается в liyne- ое состояние, блокируя схему 9 И-НЕ, благодаря чему выход компаратора устанавивается в состояние, сигнализирующее о том, что эталонная частота выше контролиуемой. В указанном состоянии компаратор находится до тех пор, пока в промежутке между поступлением на вход триггера 3 двух импульсов эталонной частоты на его вход поступят два импульса контролируемой частоты. При этом сигналы с выходов триггеров 4 и 5 поступят на вход схемы 8 И-НЕ. Однако сигнал на выходе схемы 8 И-НЁ появляется с задержкой благодаря тому, что с выхода схемы 1 И-НЕ на вход схемы 8 И-НЕ будет пост гаать входной импульс, предотвращая повторное срабатывание триггера 4. После окончания действия входного импульса задержанный сигнал с выхода схемы И-НЕ установит блокирующие триггеры 4 и 5 в исходное состояние, при котором на их выходах, соединенных со схемами 10 и 9 И-НЕ соответственно, будет единичное состояние. Компаратор перейдет от режима сравнения частот к режиму сравнения фаз. На схемы 9 и 10 И-НЕ с выходов триггеров 4 и 5 подается, разрещающий единичный сигнал, и выход компаратора повторяет сазтояние выхода фазового триггера 3, при этом длительность выходных импульсов пропорциональна фазовому сдвигу сравниваем ых частот. Формула изобретения Частотно-ч})азовый компаратор по авт. св. № 484621, отличающийся тем, что с целью исключения ложных срабатываний, выходы первой и второй схем И-НЕ подключены к соответствующим входам третьей схемы И--НЕ. Источники информации, принятые: во внимание при экспертизе. 1. Авторское свидетельство СССР № 484621, кл. Н 03 Б 13/00, 1974.

Выход

Авторы

Даты

1977-07-25—Публикация

1975-07-03—Подача