Изобретение относится к области автоматики и вычислительной техники и может быть использовано в качестве логического элемента сравнения частоты следования импульсов задающего генератора, определяющего частоту вращения двигателя в дискретных астатических электроприводах, и частоты следования импульсов датчика обратной связи, расположенного на валу двигателя, а также в других системах фазовой синхронизации.

Известен частотно-фазовый компаратор (а.с. СССР №484621, МКИ4 Н03D 13/00, 1975 г.), содержащий блок фазового сравнения, два блокирующих триггера, три элемента И-НЕ и схему логической блокировки, причем входы блока фазового сравнения подключены к клеммам источников контролируемой и эталонной частоты и к входам двух элементов И-НЕ, ко вторым входам которых подключены соответственно единичный и нулевой выходы блока фазового сравнения, а к выходам - первые входы блокирующих триггеров, нулевые выходы которых соединены с их вторыми входами через третий элемент И-НЕ, а единичные выходы - с первым и третьим входами схемы логической блокировки, второй вход которой подключен к нулевому выходу блока фазового сравнения.

Недостатком данного устройства является ненадежная работа при совпадении во времени входных импульсов, что обуславливает сбои блока фазового сравнения и блокирующих триггеров при одновременном приходе импульсов эталонной и контролируемой частот. Работоспособность компаратора в значительной степени зависит от длительности входных импульсов, что определяет необходимость использования на входе компаратора дополнительных формирователей коротких импульсов, усложняющих компаратор.

Наиболее близким техническим решением к заявляемому устройству является частотно-фазовый дискриминатор (а.с. СССР №1589373, МКИ5 Н03D 13/00, 1990 г.), содержащий блок фазового сравнения, первый и второй блокирующие триггеры, дешифратор и блок логической блокировки, причем первый и второй входы блока фазового сравнения являются соответственно первым и вторым входами частотно-фазового дискриминатора, а первый и второй выходы блока фазового сравнения являются соответственно первым и вторым входами дешифратора, первый и второй выходы которого соединены с информационными входами соответственно первого и второго блокирующих триггеров, тактовые входы которых соединены со вторым входом блока фазового сравнения, при этом выходы первого и второго блокирующих триггеров соединены соответственно с третьим и четвертым входами дешифратора, а также соответственно с первым и третьим входами блока логической блокировки, второй и четвертый входы которого соединены соответственно с первым и вторым выходами блока фазового сравнения, при этом выход блока логической блокировки является выходом частотно-фазового дискриминатора.

Недостатком такого устройства можно считать узкие функциональные возможности, не позволяющие комплексно его использовать в синхронно-синфазном электроприводе для определения как фазовой ошибки импульсов сравниваемых частот, так и угловой ошибки электропривода.

Задачей изобретения являлось расширение функциональных возможностей частотно-фазового дискриминатора (определение как фазовой ошибки импульсов сравниваемых частот, так и угловой ошибки электропривода).

Поставленная задача решена за счет того, что в известный частотно-фазовый дискриминатор, содержащий блок фазового сравнения, первый и второй входы которого являются соответственно первым и вторым входами частотно-фазового дискриминатора, а первый и второй выходы подключены соответственно ко второму и четвертому входам блока логической блокировки, выход которого является первым выходом частотно-фазового дискриминатора, а также первый и второй блокирующие триггеры, выходы которых соединены соответственно с первым и третьим входами блока логической блокировки, при этом информационные входы первого и второго блокирующих триггеров подсоединены соответственно к первому и второму выходам логического устройства, а тактовые входы - ко второму входу блока фазового сравнения, первый и второй входы логического устройства соединены соответственно с первым и вторым выходами блока фазового сравнения, а третий и четвертый входы - с выходами соответственно первого и второго блокирующих триггеров, согласно заявляемому техническому решению, введены первый и второй счетчики импульсов, дешифратор, третий триггер, первый и второй цифровые ключи, тактовый вход первого счетчика импульсов подключен ко второму входу блока фазового сравнения, а вход сброса является третьим входом частотно-фазового дискриминатора, выходы первого счетчика импульсов подключены к информационным входам второго счетчика импульсов, тактовый вход которого является четвертым входом частотно-фазового дискриминатора, а выход - вторым выходом дискриминатора, кроме того первый и второй входы дешифратора подключены соответственно к первому и второму выходам блока фазового сравнения, первый выход дешифратора подключен к информационному входу третьего триггера, тактовый вход которого соединен со вторым входом блока фазового сравнения, выход третьего триггера подключен к первому входу первого цифрового ключа, второй вход которого соединен со вторым входом блока фазового сравнения, выход первого цифрового ключа подключен к входу суммирования импульсов второго счетчика импульсов, вход вычитания импульсов которого подключен к выходу второго цифрового ключа, первый вход которого подключен к третьему выходу дешифратора, а второй вход - к первому входу блока фазового сравнения.

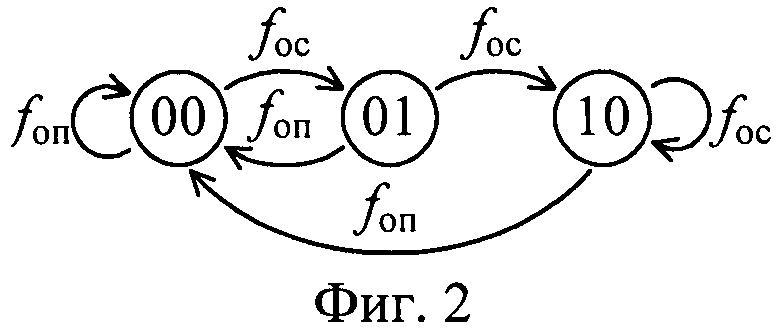

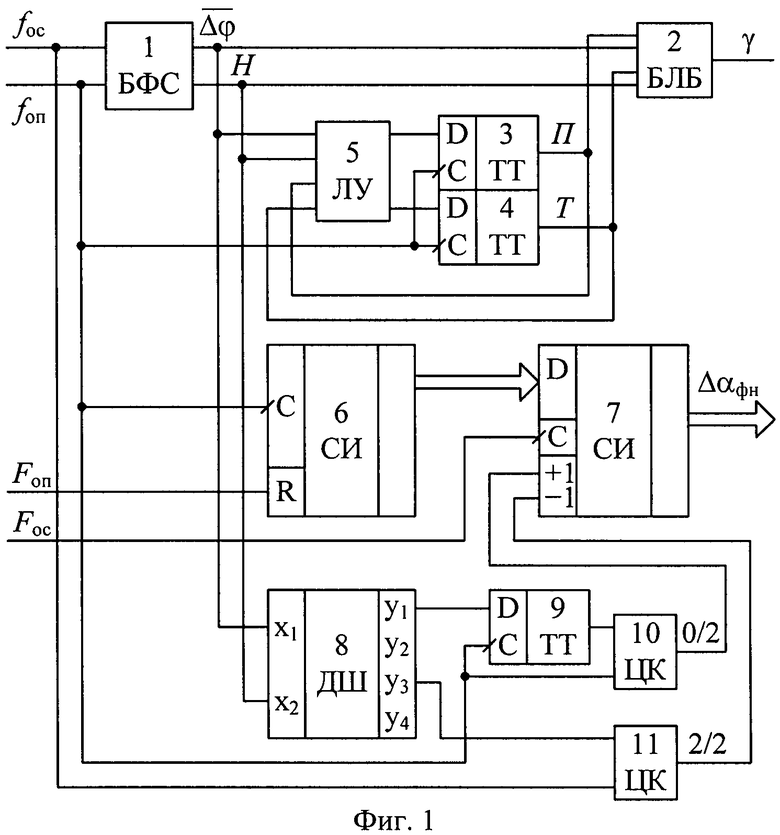

Сущность технического решения пояснена чертежами, где на фиг.1 приведена функциональная электрическая схема предлагаемого устройства; на фиг.2 приведен граф работы блока фазового сравнения предлагаемого устройства.

Частотно-фазовый дискриминатор содержит блок фазового сравнения 1, блок логической блокировки 2, блокирующие триггеры 3 и 4, логическое устройство 5, счетчики импульсов 6 и 7, дешифратор 8, триггер 9, цифровые ключи 10 и 11.

Первый и второй входы блока фазового сравнения 1 подключены соответственно к источникам контролируемой fос и опорной fоп частот (являются соответственно первым и вторым входами частотно-фазового дискриминатора), а первый и второй выходы подключены соответственно ко второму и четвертому входам блока логической блокировки 2, выход которого является первым выходом частотно-фазового дискриминатора, а первый и третий входы подсоединены соответственно к выходам блокирующих триггеров 3 и 4. Информационные входы блокирующих триггеров 3 и 4 подключены соответственно к первому и второму выходам логического устройства 5, а их тактовые входы - к источнику опорной частоты fоп (ко второму входу блока фазового сравнения 1). Первый и второй входы логического устройства 5 соединены соответственно с первым и вторым выходами блока фазового сравнения 1, а третий и четвертый входы - соответственно с выходами блокирующих триггеров 3 и 4.

Тактовый вход С счетчика импульсов 6 подключен к источнику опорной частоты foп (ко второму входу блока фазового сравнения 1), вход сброса R подключен к источнику частоты следования импульсов угловой привязки Fоп (является третьим входом частотно-фазового дискриминатора), а выходы подключены к информационным входам D счетчика импульсов 7. Первый и второй входы дешифратора 8 соединены соответственно с первым и вторым выходами блока фазового сравнения 1, а первый и третий выходы подключены соответственно к информационному входу триггера 9 и первому входу цифрового ключа 11. Тактовый вход триггера 9, объединенный со вторым входом цифрового ключа 10, подключен к источнику опорной частоты foп (ко второму входу блока фазового сравнения 1), а выход - к первому входу цифрового ключа 10. Второй вход цифрового ключа 11 подсоединен к источнику частоты обратной связи fос (к первому входу блока фазового сравнения 1), а выход - к входу вычитания импульсов счетчика импульсов 7. Вход суммирования импульсов счетчика импульсов 7 подключен к выходу цифрового ключа 10, а выход является вторым выходом частотно-фазового дискриминатора.

Частотно-фазовый дискриминатор работает следующим образом.

Импульсы опорной fоп и контролируемой fос частот поступают на вход блока фазового сравнения 1, осуществляющего подсчет числа импульсов частоты fос между двумя импульсами частоты fоп от начального значения 00 с насыщением в состоянии 10. Работа блока фазового сравнения 1 поясняется с помощью графа переходов. При приходе импульса частоты fоп при любом предыдущем состоянии выходов блока фазового сравнения 1 появляются низкие уровни сигналов (логические 0) на первом  и на втором Н его выходах. При последующем приходе импульса частоты fос на первом выходе блока фазового сравнения 1 появляется высокий уровень сигнала

и на втором Н его выходах. При последующем приходе импульса частоты fос на первом выходе блока фазового сравнения 1 появляется высокий уровень сигнала  (состояние 01 на графе переходов блока фазового сравнения 1). При приходе еще одного импульса частоты fос на втором выходе блока фазового сравнения 1 появляется высокий уровень сигнала Н (состояние 10 на графе переходов блока фазового сравнения 1).

(состояние 01 на графе переходов блока фазового сравнения 1). При приходе еще одного импульса частоты fос на втором выходе блока фазового сравнения 1 появляется высокий уровень сигнала Н (состояние 10 на графе переходов блока фазового сравнения 1).

Блокирующие триггеры 3 и 4 служат для формирования сигналов индикации режимов работы частотно-фазового дискриминатора. Эти сигналы используются для работы логического устройства 5 и блокировки выходного сигнала блока фазового сравнения 1 с помощью блока логической блокировки 2. При этом высокий уровень сигнала П на выходе блокирующего триггера 3 соответствует режиму фазового сравнения частотно-фазового дискриминатора при fос≈fоп, высокий уровень сигнала Т на выходе блокирующего триггера 4 - режиму насыщения при fос>fоп, а низкие уровни сигналов П и Т - режиму насыщения при fос<fоп. В момент прихода импульса частоты fоп в блокирующие триггеры 3 и 4 записывается информация о текущем режиме работы частотно-фазового дискриминатора, формируемая на выходах логического устройства 5 в зависимости от текущих значений выходных сигналов блока фазового сравнения 1 и блокирующих триггеров 3 и 4.

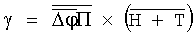

Блок логической блокировки 2 служит для формирования выходного сигнала в соответствии с логической функцией  , где

, где  - выходной сигнал с первого выхода блока фазового сравнения 1; Н - выходной сигнал со второго выхода блока фазового сравнения 1, соответствующий приходу двух или более импульсов контролируемой частоты fос между двумя импульсами опорной частоты fоп; П - выходной сигнал блокирующего триггера 3; Т - выходной сигнал блокирующего триггера 4.

- выходной сигнал с первого выхода блока фазового сравнения 1; Н - выходной сигнал со второго выхода блока фазового сравнения 1, соответствующий приходу двух или более импульсов контролируемой частоты fос между двумя импульсами опорной частоты fоп; П - выходной сигнал блокирующего триггера 3; Т - выходной сигнал блокирующего триггера 4.

Режиму фазового сравнения частотно-фазового дискриминатора соответствует наличие низких уровней сигналов Н и Т и высокого уровня сигнала П, который с выхода блокирующего триггера 3 проходит на блок логической блокировки 2, разрешая прохождение сигнала  с выхода блока фазового сравнения 1 на выход устройства. В режиме фазового сравнения сигнал

с выхода блока фазового сравнения 1 на выход устройства. В режиме фазового сравнения сигнал  представляет собой последовательность импульсов, период следования которых равен периоду опорной частоты fоп, а длительность пропорциональна величине фазового рассогласования импульсов сравниваемых частот fоп и fос.

представляет собой последовательность импульсов, период следования которых равен периоду опорной частоты fоп, а длительность пропорциональна величине фазового рассогласования импульсов сравниваемых частот fоп и fос.

В режимах насыщения частотно-фазового дискриминатора на первый вход блока логической блокировки 2 поступает низкоуровневый сигнал П с выхода блокирующего триггера 3. В этом случае на выходе блока логической блокировки 2 появляется высокий уровень сигнала γ в режиме насыщения при fос<fоп или низкий уровень сигнала γ в режиме насыщения при foс>fоп.

Логическое устройство 5 в зависимости от состояния выходов блока фазового сравнения 1 и блокирующих триггеров 3 и 4 формирует сигналы текущего режима работы, поступающие на информационные входы этих триггеров и записываемые в них в момент прихода импульса частоты fоп.

Работа логического устройства 5 поясняется с помощью таблицы 1.

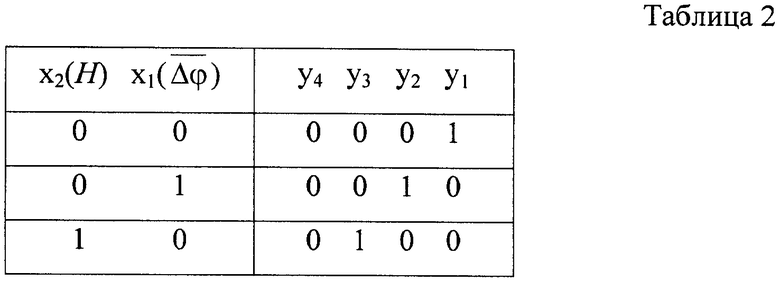

Дешифратор 8 предназначен для выделения состояний блока фазового сравнения 1, соответствующих приходу 0 или 2 и более импульсов частоты fос между двумя соседними импульсами частоты foп. Работа дешифратора 8 поясняется таблицей 2.

Второй у2 и четвертый у4 выходы дешифратора 8 в работе частотно-фазового дискриминатора не используются.

При приходе импульса частоты fоп на выходах блока фазового сравнения 1 формируется код 00 (соответствующий низким уровням сигналов  и Н), поступающий на входы х1 и х2 дешифратора 8. В результате на первом выходе дешифратора 8 появляется сигнал логической 1, поступающий на информационный вход D D-триггера 9. Если в этот момент повторно приходит импульс частоты fоп, то в D-триггер 9 записывается логическая 1, несущая информацию о том, что между двумя соседними импульсами частоты fоп не прошло ни одного импульса частоты fос.

и Н), поступающий на входы х1 и х2 дешифратора 8. В результате на первом выходе дешифратора 8 появляется сигнал логической 1, поступающий на информационный вход D D-триггера 9. Если в этот момент повторно приходит импульс частоты fоп, то в D-триггер 9 записывается логическая 1, несущая информацию о том, что между двумя соседними импульсами частоты fоп не прошло ни одного импульса частоты fос.

Если после прихода на второй вход блока фазового сравнения 1 импульса частоты foп на первый его вход пришли два или более импульсов частоты fоc, то на его выходе формируется код 10 (соответствующий низкому уровню сигнала  и высокому уровню сигнала H), поступающий на входы x1 и x2 дешифратора 8. В результате на третьем выходе дешифратора 8 появляется сигнал логической 1, несущий информацию о том, что между двумя соседними импульсами частоты fоп прошло два или более импульсов частоты fос.

и высокому уровню сигнала H), поступающий на входы x1 и x2 дешифратора 8. В результате на третьем выходе дешифратора 8 появляется сигнал логической 1, несущий информацию о том, что между двумя соседними импульсами частоты fоп прошло два или более импульсов частоты fос.

Выходной сигнал D-триггера 9 и сигнал с третьего выхода дешифратора 8 используются для управления цифровыми ключами 10 и 11 соответственно, выполненными на основе двухходовых элементов И. На информационные входы цифровых ключей 10 и 11 поступают импульсы частот foп и fос соответственно, которые при высоком уровне управляющего сигнала проходят на выходы цифровых ключей 10 и 11. Далее эти импульсы проходят на суммирующий (+1) и вычитающий (-1) входы счетчика импульсов 7, обеспечивая корректировку сигнала угловой ошибки на его выходе на интервале времени между двумя соседними импульсами Foс. При этом записанный в счетчик импульсов 7 двоичный код увеличивается или уменьшается на 1, что соответствует изменению угловой ошибки электропривода на величину углового расстояния между соседними метками импульсного датчика частоты вращения электропривода  , где z - количество меток импульсного датчика частоты вращения.

, где z - количество меток импульсного датчика частоты вращения.

Счетчик импульсов 6 предназначен для определения сигнала угловой ошибки электропривода путем подсчета импульсов опорной частоты fоп между импульсом угловой привязки Foп и импульсом Fос с выхода датчика положения электропривода. Счетчик импульсов 6 сбрасывается в ноль при приходе импульса угловой привязки Fоп на вход сброса R. Далее при приходе каждого импульса частоты fоп на тактовый вход С значение двоичного кода на выходах счетчика импульсов 6 увеличивается на единицу. Двоичный код с выходов счетчика импульсов 6, пропорциональный угловой ошибке, поступает на информационные входы D счетчика импульсов 7 и записывается в него при приходе импульса Fос с выхода датчика положения электропривода. На интервале времени между двумя соседними импульсами Fос корректировка записанного в счетчик импульсов 7 по импульсу Fос сигнала угловой ошибки осуществляется с помощью импульсов с выходов цифровых ключей 10 и 11.

Частотно-фазовый дискриминатор может находиться в трех основных режимах работы: насыщения при fос<fоп (соответствует работе электропривода в режиме разгона), фазового сравнения при fос≈fоп (соответствует работе электропривода в синхронном режиме) и насыщения при fос>fоп (соответствует работе электропривода в режиме торможения). Переход из режима в режим синхронизирован по импульсам опорной частоты fоп. В каждом режиме работы осуществляется подсчет числа импульсов контролируемой частоты fос между двумя импульсами опорной частоты fоп.

При приходе двух подряд импульсов частоты fос между двумя соседними импульсами частоты fоп происходят следующие изменения в работе частотно-фазового дискриминатора:

а) из режима насыщения при fос<fоп (разгон электропривода) происходит переход в режим фазового сравнения при fос≈fоп (синхронный режим работы электропривода);

б) из режима фазового сравнения происходит переход в режим насыщения при fос>fоп (торможение электропривода);

в) режим насыщения при fос>fоп сохраняется.

При отсутствии импульсов частоты fос между двумя соседними импульсами частоты fоп изменение режима работы происходит в обратном порядке.

В любом режиме работы частотно-фазовый дискриминатор позволяет непрерывно определять угловую ошибку электропривода. С этой целью определяется начальное значение угловой ошибки путем подсчета количества импульсов частоты fоп между импульсом угловой привязки Fоп и импульсом Fос с выхода датчика положения электропривода. Полученное значение сохраняется в выходном реверсивном счетчике импульсов. Далее это значение корректируется в моменты прихода двух импульсов одной частоты между двумя соседними импульсами другой частоты на величину углового расстояния между соседними метками импульсного датчика частоты вращения электропривода. В результате на выходе реверсивного счетчика импульсов непрерывно формируется текущее значение угловой ошибки электропривода.

Таким образом, предлагаемое техническое решение позволяет расширить функциональные возможности частотно-фазового дискриминатора за счет введения в него двух счетчиков импульсов, дешифратора, триггера и двух цифровых ключей, что позволяет наряду с определением ошибки фазового рассогласования импульсов сравниваемых частот определять угловую ошибку синхронно-синфазного электропривода.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФАЗИРОВАНИЯ ВРАЩАЮЩЕГОСЯ ВАЛА ЭЛЕКТРОДВИГАТЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2015 |

|

RU2608177C2 |

| Частотно-фазовый дискриминатор | 2018 |

|

RU2695986C1 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2010 |

|

RU2422978C1 |

| СПОСОБ ФАЗИРОВАНИЯ ВРАЩАЮЩЕГОСЯ ВАЛА ЭЛЕКТРОДВИГАТЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2016 |

|

RU2649307C1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2462809C1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2467465C1 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2485665C1 |

| СПОСОБ ФАЗИРОВАНИЯ ВРАЩАЮЩЕГОСЯ ВАЛА ЭЛЕКТРОДВИГАТЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2475932C1 |

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2016 |

|

RU2621288C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах фазовой синхронизации. Достигаемый технический результат - расширение функциональных возможностей частотно-фазового дискриминатора путем определения как фазовой ошибки импульсов сравниваемых частот, так и угловой ошибки синхронно-синфазного электропривода. Частотно-фазовый дискриминатор содержит блок фазового сравнения (1), блок логической блокировки (2), блокирующие триггеры (3), (4), логическое устройство (5), два счетчика импульсов (6, 7), дешифратор (8), триггер (9) и два цифровых ключа (10, 11). 2 ил., 2 табл.

Частотно-фазовый дискриминатор, содержащий блок фазового сравнения, первый и второй входы которого являются соответственно первым и вторым входами частотно-фазового дискриминатора, а первый и второй выходы подключены соответственно ко второму и четвертому входам блока логической блокировки, выход которого является первым выходом частотно-фазового дискриминатора, а также первый и второй блокирующие триггеры, выходы которых соединены соответственно с первым и третьим входами блока логической блокировки, при этом информационные входы первого и второго блокирующих триггеров подсоединены соответственно к первому и второму выходам логического устройства, а тактовые входы - ко второму входу блока фазового сравнения, первый и второй входы логического устройства соединены соответственно с первым и вторым выходами блока фазового сравнения, а третий и четвертый входы - с выходами соответственно первого и второго блокирующих триггеров, отличающийся тем, что в него введены первый и второй счетчики импульсов, дешифратор, третий триггер, первый и второй цифровые ключи, тактовый вход первого счетчика импульсов подключен ко второму входу блока фазового сравнения, а вход сброса является третьим входом частотно-фазового дискриминатора, выходы первого счетчика импульсов подключены к информационным входам второго счетчика импульсов, тактовый вход которого является четвертым входом частотно-фазового дискриминатора, а выход - вторым выходом дискриминатора, кроме того, первый и второй входы дешифратора подключены соответственно к первому и второму выходам блока фазового сравнения, первый выход дешифратора подключен к информационному входу третьего триггера, тактовый вход которого соединен со вторым входом блока фазового сравнения, выход третьего триггера подключен к первому входу первого цифрового ключа, второй вход которого соединен со вторым входом блока фазового сравнения, выход первого цифрового ключа подключен к входу суммирования импульсов второго счетчика импульсов, вход вычитания импульсов которого подключен к выходу второго цифрового ключа, первый вход которого подключен к третьему выходу дешифратора, а второй вход - к первому входу блока фазового сравнения.

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ | 1995 |

|

RU2090902C1 |

| US 6567482 B1, 20.05.2003. | |||

Авторы

Даты

2011-09-10—Публикация

2010-06-11—Подача