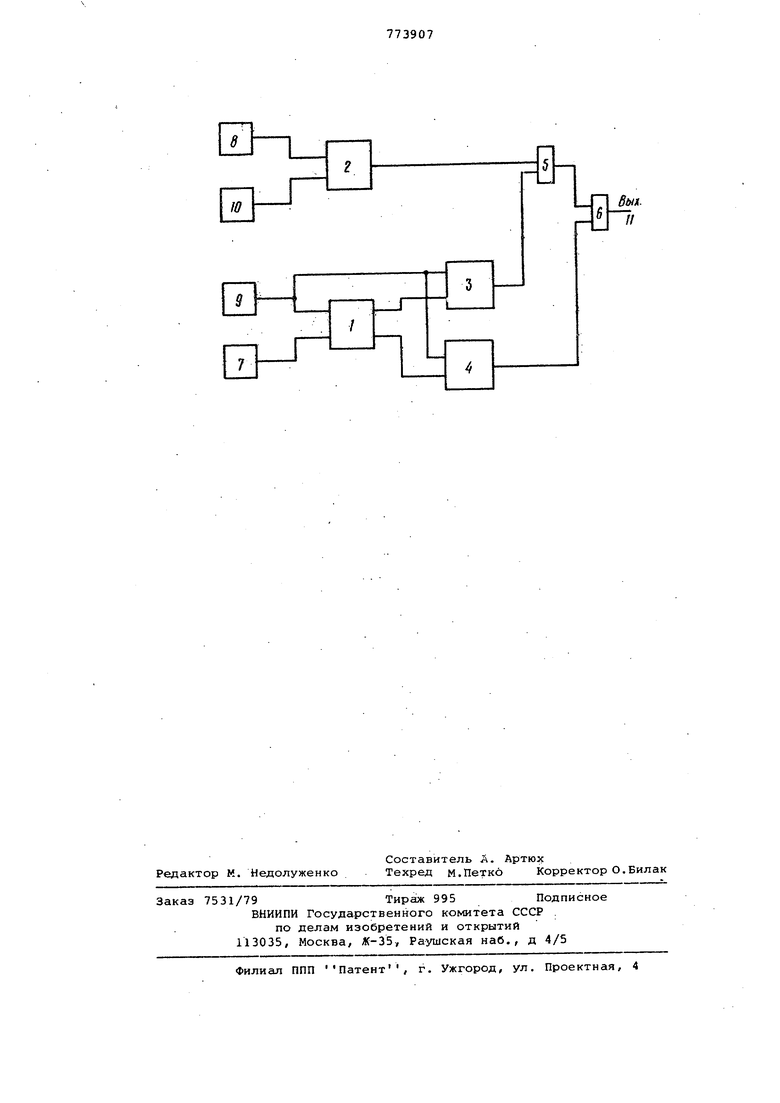

Изобретение относится к импульсно технике. Известен частотно-фазовый компаратор, содержгиций ява триггера, два формирующих триггера, логический элемент, два логических элемента ИЛИ RS-триггер, два логических элемента И, два разностных элемента и два элемента задержки 1. Недостатком данного устройства яв ляется его сложность. Наиболее близким по технической сущности к предлагаемому является частотно-фазовый компаратор, содержащий фазовый триггер, один вход ко торого соединен с источником эталонной частоты, другой вход - с источни ком сравниваемой частоты, выход кото рого подключен к одному входу первог элемента И-НЕ, второй вход которого соединен с выходом первого блокирующего триггера, первый вход которого соединен с источником контролируемой частоты и с первым входом второго блокирующего триггера, выход которо подключен к п рвому входу второго элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ (21. Однако компаратор не обеспечивает остаточного быстродействия. Цель иэобретения - повышение быстродействия , Поставленная цель достигается тем, что в частотно-Фазовый компаратор, содержащий фазовый триггер, один вход которого соединен с источником эталонной частоты, другой вход - с источником сравниваемой частоты, а выход подключен к одному входу первого элемента И-НЕ, второй вход которого соединен с выходом первого блокирующего триггера, первый вход которого соединен с источником контролируемой частоты и с nepBEjM входом второго блокирующего триггера, выход которого подключен к первому второго элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, введены блок формирования импульсов эталфнных длительностей и источник опорной частоты, выход которого соединен с первым входом блока формирования импульсов эталонных длительностей, второй вход которого соединен с источником контролируемой частоты, а выходы подключены ко вторым входам блокирующих триггеров . На чертеже приведена структурная электрическая схема компаратора. Компаратор содержит блок 1 формирования импульсов эталонных:длительностей, фазовый триггер 2, блокирующее триггеры 3 и 4, элементы И-НЕ 5 W 6, источники опорной 7 и -эталонной 8 частот, источники контролируемой 9 и сравниваемой 10 частот. Выход но1 сигнал снимается с выхода 11. Устройство работает следующим образом. Под действием импульса от источника контролируемой частрты 9 блок 1 формирования импульсов эталонных длительностей устанавливается в исходное состояние. Поступающий на его второй вход импульс от источника опорной частоты 7 формирует эталонны длительности. На выходе блока 1 формирования импульсов ,эталонных длительностей вырабатывается сигнал до момента времени где f - опорная частота; flT- величина времени, на котору может отличаться период кон тролируемой частоты от опор ной . ria другом выходе блока формирова импульсов эталонных длительностей вырабатывается сигнал с момента вре мени Если импульс источника контролир емой частоты 9 поступит на вторые ъходы триггеров 3 и 4 в момент нали чия сигнала на одном выходе блока 1 под действием этого импульса сработает триггер 4, первый вход которог соединен с первым входом блока 1. В результате срабатывания триггера 4 блокируется работа элемента И-НЕ 6. При этом с выхода компаратора вьщается сигнал о том, что контролируемая частота больше опорной частоты. Если импульс контролируемой част ты поступит на вторые входы триггеров 3 и 4 а момент наличия сигнала втором выходе блока 1,то под действ этого импульса сработает триггер 3, оторый блокирует работу элемента -НЕ 5- При этом с выхода компаратоа вьщается сигнал о том, что конролируемая частота меньше опорной. Если импульс контролируемой частоы поступает на вторые; входы триггеов 3 и 4 в момент отсутствия сигнаа на выходах блока 1, то триггеры и 4 под действием этого импульса станавливаются в исходное состояние ри этом с фазового триггера 2 сигал поступает на выход компаратора. Таким образом, частотно-фазовый омпаратор переводится в режим сравения фаз не после превышения онтролируемой частоты над опорной,а момент попадания контролируемой астоты в заданный диапазон частот, асположенный симметрично опорной астоты, что позволит уменьшить врея переходных процессов, т.е. повысить ыстродействие. Формула изобретения Частотно-фазовый компаратор,содержащий фазовый триггер один вход которого соединен с источником эталонной частоты, другой вход - с источником сравниваемой частоты, а выход подключен к одному входу первого эле мента И-НЕ, второй вход которого соединен с выходом первого блокирующего триггера, первый вход которого соединен с источником контролируемой частоты и с первым входом второго блокирующего триггера, выход которого подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, отличающийся тем, что, с целью повышения быстродействия, в него введены блок формирования импульсов эталонных длительностей и источник опорной частоты, выход которого соединен с первым входом блока формирования импульсов эталонных длительностей, второй вход которого соединен с источником контролируемой частоты, а выходы подклЕдчены . ко вторым входам блокирующих триггеров . Источники информации принятые во внимание при экспертизе 1.Авторское свидетельство СССР 540347, кл. И 03 D 1.3/00, 18.12.75. 2.Авторское свидетельство СССР 484621,кл. Н 03 D 13/00,04.03.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый компаратор | 1975 |

|

SU566301A2 |

| Частотно-фазовый компаратор | 1974 |

|

SU484621A1 |

| ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР | 2011 |

|

RU2469461C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 2010 |

|

RU2428785C1 |

| ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР | 2017 |

|

RU2647678C1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| Устройство для измерения параметров колебательных контуров | 1984 |

|

SU1265650A1 |

| Преобразователь частоты в код | 1988 |

|

SU1607078A1 |

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

| Устройство для измерения частотных характеристик канала связи | 1986 |

|

SU1381723A1 |

Авторы

Даты

1980-10-23—Публикация

1979-04-03—Подача