1

.. Изобретение относитея к дискретным сис темам связи и может использоваться для синхронизации аппаратуры передачи дискрет ных сигналов.

Известно устройство тактовой синхронигзаций, содержащее объединенные по входу импульсно-фазовый дискриминатор и обнаружитель перерывов связи, интегратор, выходы которого через блок управления, ко второму входу которого подключен выход задающего генератора, подключены к делителю частоты, выход которого подключен к соответствующим входам импульсно-фазового дискриминатора и датчика циклов lii.

Однако в известном устройстве имеет место,рассинхронизация аппаратуры передачи дискретных сигналов за счет отклонения частот задающих генераторов от номиналов, вследствие чего i время удержания синхронизма аппаратуры невелико.

Цель изобретения - увеличение времени удержания синхронизма при перерывах связи

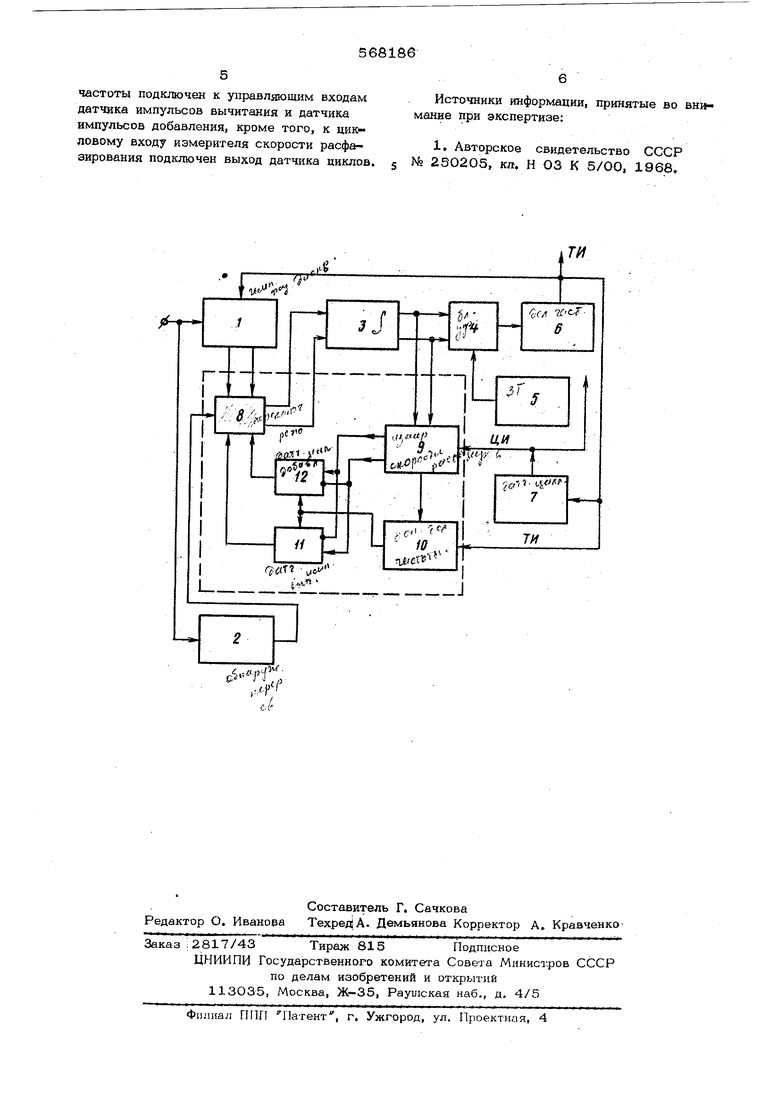

Для ЭТОГО в устройство тактовой синхронизации, содержащее объединенные по входу импульсно-фазовый дискриминатор и обнаружитель перерывов свази, интегратор, выхо ды которого через блок управления, ко вто- рому входу которого подключен выход задающего генератора, подключены к делителю частоты, выход которого подключен к соот ветствующим входам импульсно-фазового дискриминатора и датчика циклов, введены переключатель режимов, измврите.;ь скороо ти расфааирования, дополнительный делитель частоты, датчик импульсов вычитания и дат чик импульсов добавления, при этом выходы интегратора через измеритель скорости расфазировшшя подключены к одному из входов дополнительного делителя частоты и ко входам датчика импульсов вычитания и дит«-. чика импульсов добавления, i выходы которых одновременно с выходами импульсно-фазового дискриминатора и выходом обнаружителя перерывов связи подключены к соответствующим входам переключателя режимов, вых1 ды которого подключены к соответствующим входам интегратора, причем к управляющему входу дoпoлнитeJlЬнoгo делителя частоты подключен выход делителя частоты, а выход дополнительного делителя частоты подклк « чён к управляющим входам датчика импульсоввычитания и датчика импульсов добавления кроме того, к цикловому входу измерителя скорости расфазирования подключен вьц(од| датчика циклов. Н чертеже изображена структурная элек тричЕе1ская схема устройства тактовой си хронизашв. устройство тактовой синхронизации содержит объединенные по входу импульснофааовый дискриминатор Д. и обнаружитель перерывов связи 2 интегратор 3, выходы которого через блок управления 4, ко второ му,входу которого подключен выход задающего генератора 5, подключены к делителю частоты в, выход которого подключен к со ответствующим входам импульсно-фазового дискриминатора 1 и датчика циклов 7, пере ключатель режимов S, измеритель скорости расфазирования 9, дополните}1ьный делитель частоты 10, датчик импульсов вычитания 1 и датчик импульсов добавления 12, при это выходы интегратора 3 через измеритель скорости расфазирования 9 подключены к одному из входов дополнительного делителя частоты 10 и ко входам датчика импульсов вычитания 11 и датчика импульсов добавления 12, выходы которых одновременно с выходами импульсно зового дискриминатора 1 и выходом обнаружителя перерывов связи 2 подключены к соответствующим входам переключателя режимов 8, выходы которого подключены к соответствующим входам интегратора 3, причем к управляющему входу дополнительного делителя частоты 1О подключен выход делителя частоты 6, а выход дополнительного делителя частоты 10 подключен к управляющим входам датчика импульсов вычитания 11 и датчика импульсов добавления 12, кроме того, к цикловому входу измерителя скорости расфазирования 9 подключен выход датчика циклов 7, . Устройство работает следующим образом Во время приема дискретного сигнала с выходов интегратора 3 импульсы опереже- ние или отставание поступают на соответствующие входы измерителя скорости расфазирования 9 и на блок управления 4, делитель частоты 6. Импульсы добавление с выхода измерителя скорости расфааирования 9 вкшэчают датчик импульсов до бавления 12 и выключают датчик импульсов вычитания 11, а импульсы вычитание Бюточают датчик импульсов вычитания 11 и выключают датчик импульсов добавления 12. При этом осуществляется запоминание знака расфааирования. Кроме того, импульсами с соответствующих выходов измерителя скорости расфазирования 9 с помощью ключей устанавливается : коэффициент деления дополнительного делителя частоты 10 в соответствии с величиной ск ррости рас азнрования принимаемых сигналов и тактовых импульсов приемника. При исчезновении Сигнала или резком ухудшении его качест ва импульсом с выхода обнаружителя пер&рыврв связи 2, поступающим на переключатель режимов 8, от входов интегратора 3 отключаются выходы импульсно-фазового дискриминатора 1 и подключаются выходы датчика импульсов добавления 12 и датчика импульсов вычитания 11, При этдм на вход интегратора 3 поступают импульсы, которые осуществляют коррекцию фазы тактовых импульсов приемника в том же напрев лении, как это осуществлялось по принимаем мым,- посылками сигнала доЪерерыва связи. Интервалы времени, за которые производят ся измерения скорости расфаЗирования, ortределяются периодом следования импульсов с датчика циклов 7,. Предлагаемое устройство тактовой синхро низации позволяет увеличить время удержиНИИ синхронизма в 20-25 раз по сравн&нию с известными устройствами. Формула изобретения .... о.. , Устройство тактовой синхронизации, содержащее объединенные по входу импульс- но-фазовый дискриминатор и обнаружитель перерывов связи, интегратор, выходы которого через блок управления, ко -второму входу которого подключен выход задающего генератора, подключены к дeлитeJЖ) частоты, выход которого подключен к соответ ствующим входам импульсно-фазового диокриминатора и датчика циклов, от л №-. чающееся тем, что, с целью увеличения времени удержания синхронизма при перерывах связи, введены переключатель режимов, измеритель скорости расфазирования, дополнительный делитель частоты, датчик импульсов вычитания и датчик импульсов добавления, при этом выходы интегратора через измеритель скорости расфазирования подключены к одному из входов дополнительного делителя частоты и ко входам датчика импульсов вычитания и датчика импульсов добавления, выходы которых одновременно с йыходами импульсно- фазового дискриминатора и выходом обнаружителя перерывов связи подключены к йоответствуюшим входам переключателя режимов, выходы которого подключены к соответствующим входам интегратора, причем к управляющему входу дополнительного делителя частоты подключен выход делителя частоты, а выход допол1штельно10 делителя частоты подключен к управляющим входам датчика импульсов вычитания и датчика импульсов добавления, кроме того, к цикловому входу измерителя скорости расфаV r-ll г----J- -- v.« «. .,|/V« зирования подключен выход датчика циклов. 5 Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР - f-r Л JT-JU tJA t JlOL 1 OUV N-JV-Ji 250205, кл. Н 03 К 5/00, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации с фазовой автоподстройкой частоты | 1976 |

|

SU636812A1 |

| Двухступенчатый регенератор | 1978 |

|

SU726668A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство синхронизации | 1979 |

|

SU924890A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU938420A1 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

| Устройство групповой тактовой синхронизации | 1982 |

|

SU1022325A2 |

| Устройство групповой тактовой синхронизации | 1980 |

|

SU921107A1 |

| Устройство для измерения преобладаний двоичных сигналов | 1986 |

|

SU1338102A2 |

Авторы

Даты

1977-08-05—Публикация

1975-02-13—Подача