XI

ю

оо

со

Изобретение относится к области электросвязи и может быть использовано в системах передачи дискретной информации для тактовой синхронизации.

Целью изобретения является повышение помехоустойчивости.

На фиг.1 представлена структурная электрическая схема устройства фазовой автоподстройки тактовой частоты; на фиг.2- 5 - соответственно структурные электрические схемы частотного дискриминатора, формирователя управляющих сигналов частотной автоподстройки, корректора частотного рассогласования и блока запуска частотного дискриминатора.

Устройство фазовой автоподстройки тактовой частоты содержит задающий генератор 1, блок 2 оценки фазового рассогласования, усредняющий блок 3, коммутатор 4, первый блок 5 добавления и исключения импульсов, первый делитель 6 частоты, формирователь 7 фазовой зоны, обнаружитель 8 синхронизма, второй блок 9 добавления и исключения импульсов, второй делитель 10 частоты, пороговый блок 11, частотный дискриминатор 12. блок 13 запуска частотного дискриминатора, формирователь 14 управляющих сигналов частотной автоподстройки, корректор 15 частотного рассогласования.

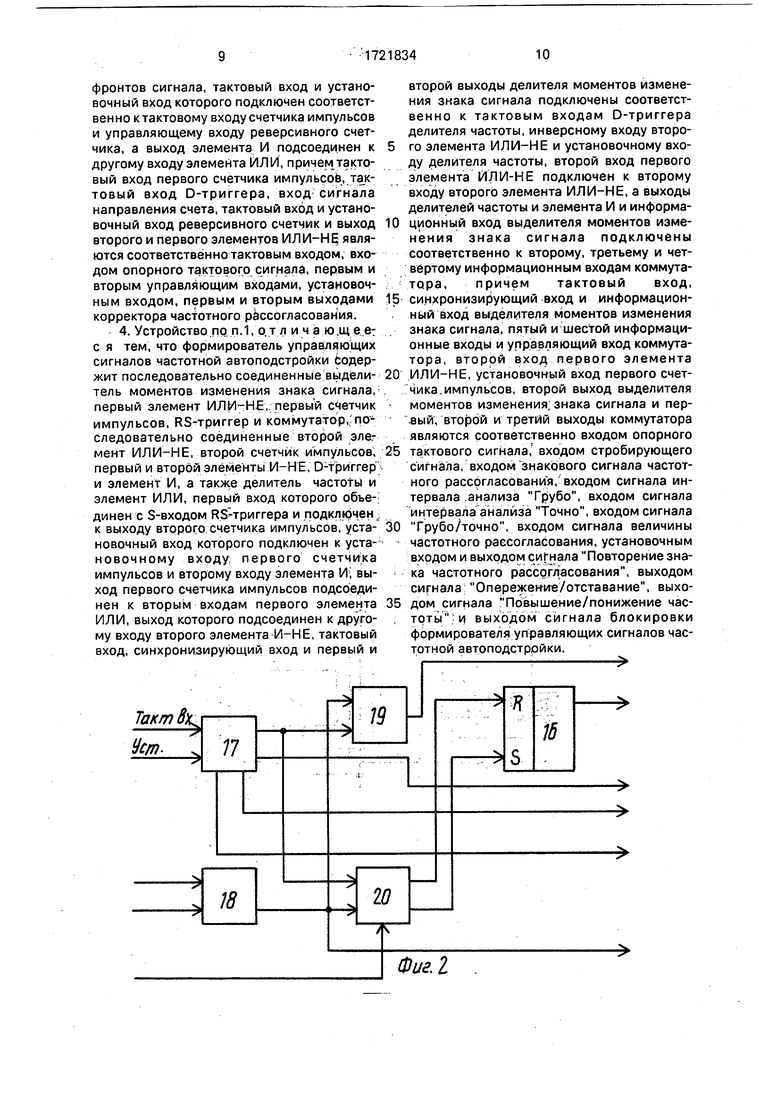

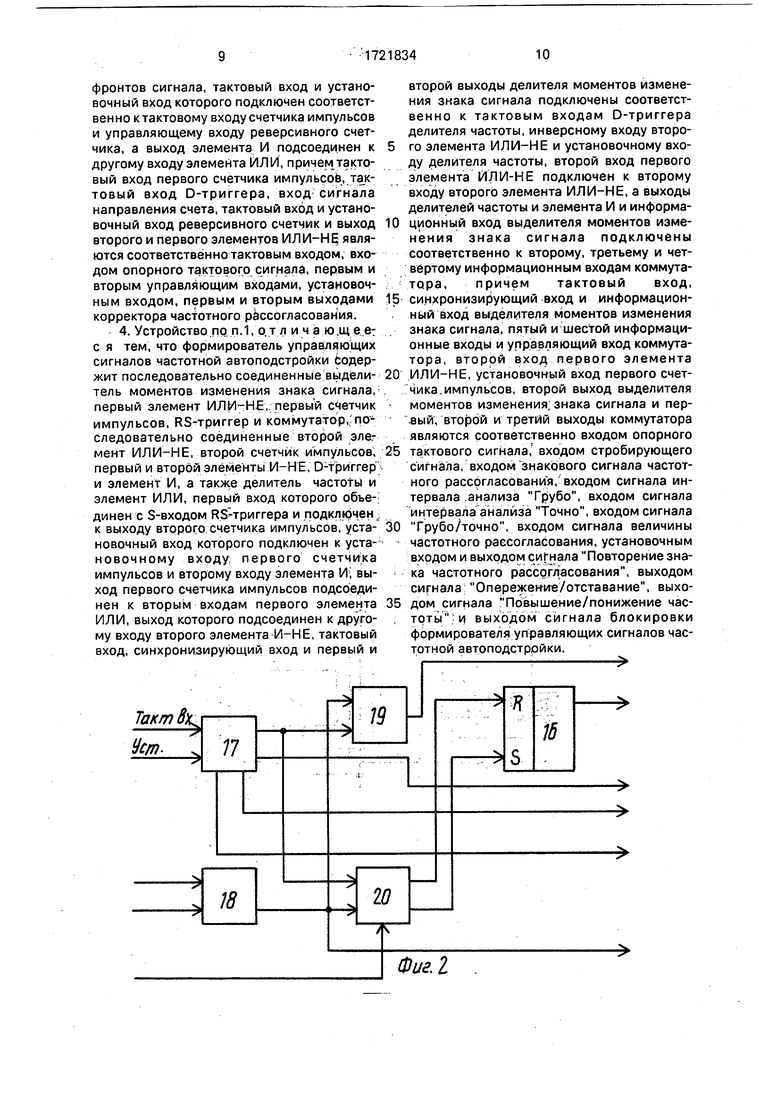

Частотный дискриминатор 12 содержит RS-триггер 16, первый 1.7 и второй 18 делители частоты, сумматор 19 по модулю два, выделитель 20 фронтов сигнала.

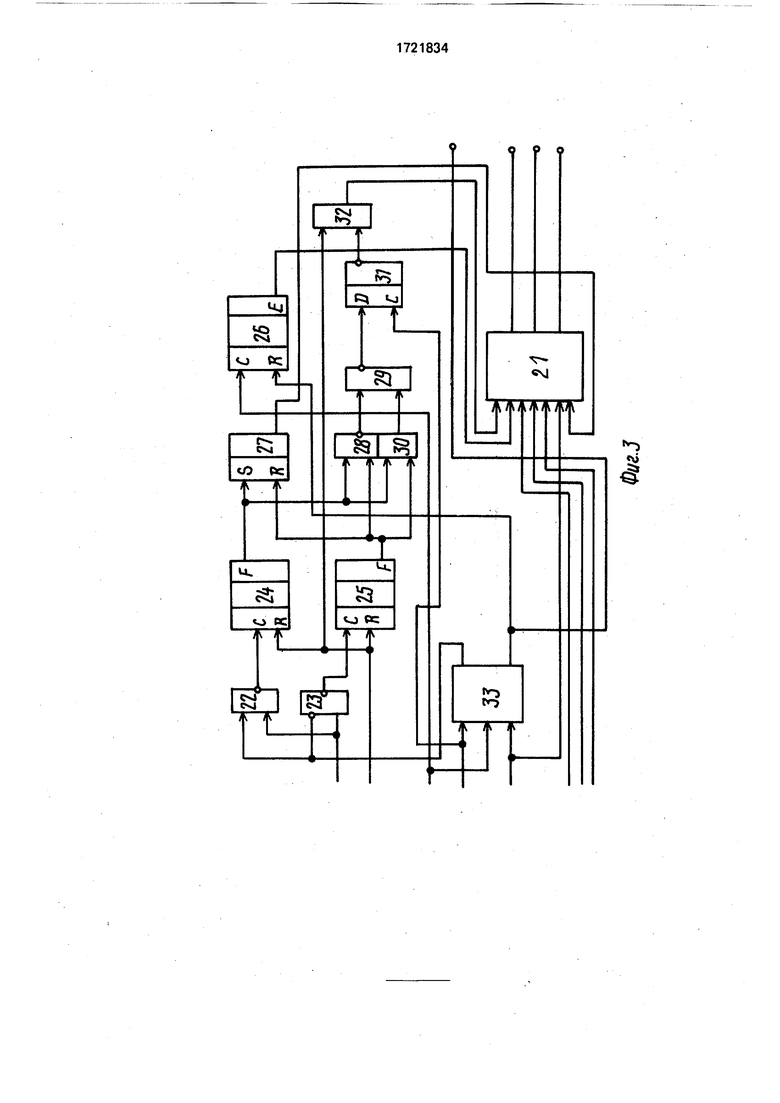

Формирователь 14 управляющих сигна- лов частотной автоподстройки содержит коммутатор 21, первый 22 и второй 23 элементы ИЛЙ-НЕ, первый 24 и второй 25 счетчики импульсов, делитель 26 частоты, RS-триггер 27, первый и второй элементы И-НЕ 28 и 29, элемент ИЛИ 30, D-триггер 31, элемент И 32, выделитель 33 моментов изменения знаков сигнала.

Корректор 15 частотного рассогласования содержит элемент ИЛИ 34, реверсивный счетчик 35, регистр 36 сдвига, компаратор 37, D-триггер 38, второй и первый счетчики 39 и 40 импульсов, элемент И 41, первый и второй элементы ИЛ И-НЕ 42 и 43, выделитель 44 передних фронтов сигнала.

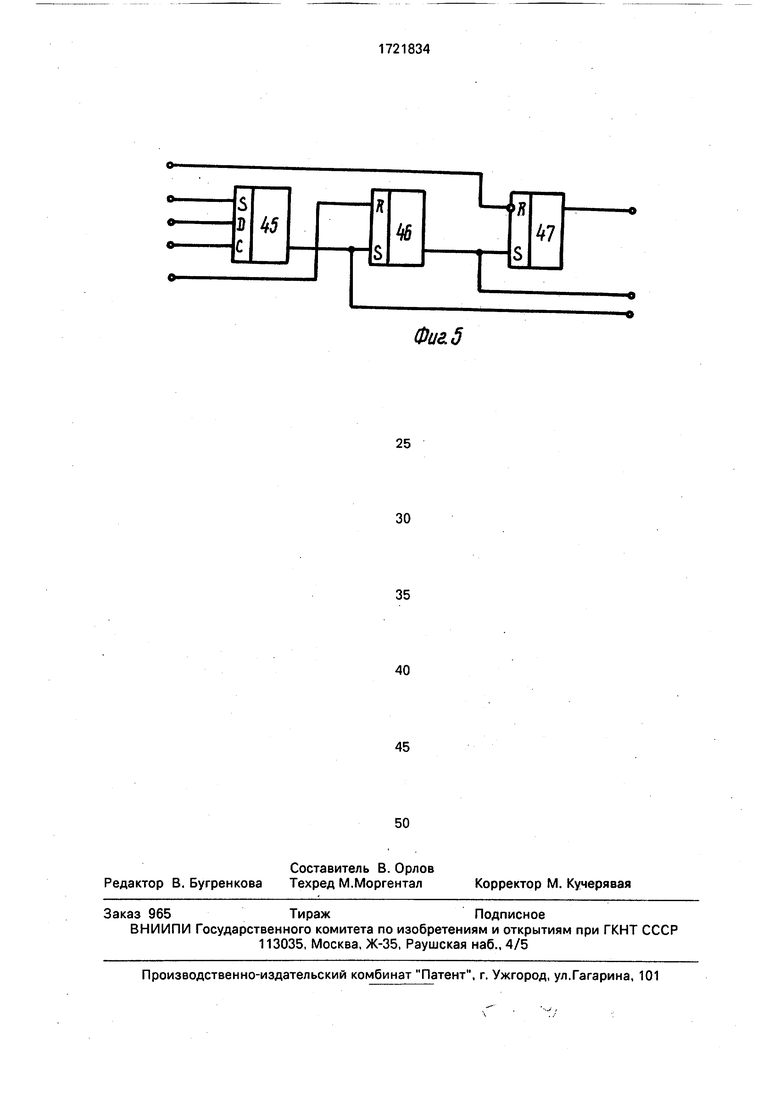

Блок 13 запуска частотного дискриминатора содержит D-триггер 45, RS-триггёры 46 и 47.

Устройство фазовой автоподстройки тактовой частоты работает следующим образом.

При появлении импульса начальной установки первый блок 5 добавления и исклю- чения и корректор 15 приводятся в

исходное состояние, а работа второго блока 9 добавления и исключения, второго делителя 10 и частотного дискриминатора 12 запрещается.

При отсутствии информации на информационном входе блока 2 тактовый сигнал, получаемый делением частоты задающего генератора 1, поступает с выхода первого делителя 6 без коррекции фазы.

0 При поступлении информации приводится в действие первая петля фазовой автоподстройки, работа которой направлена на устранение начального фазового и частотного рассогласования тактового сигнала

5 на выходе первого делителя 6 и принимаемого импульсного (информационного сигнала).

При этом в зависимости от знака рассогласования в блоке 2 формируются и выдают0 ся на его соответствующие выходы последовательности импульсов, соответствующие значащим моментам информацион- ного сигнала. Импульсы коррекции с выходов блока 2 усредняются в усредняю5 щем блоке 3 и подаются далее через коммутатор 4 на первый блок 5 добавления и исключения. При обеспечении тактовой синхронизации, когда выходной тактовый сигнал и информационный сигнал сфазиро0 ваны, а их частотное расхождение скомпенсировано, срабатывает обнаружитель 8, выходной сигнал которого осуществляет запуск через блок 13 запуска частотного дискриминатора 12 и второго делителя 10. При

5 этом осуществляется следующая последовательность срабатывания узлов. При поступлении импульса запуска на разрешающий вход блока 13 запуска на одном из его выходов формируется сигнал,

0 разрешающий работу второго делителя 18 частотного дискриминатора 12, Через время, равное периоду сигнала на выходе второго делителя 18, на соответствующем выходе блока запуска устанавливается сиг5 нал, фазирующий первый 17 и второй 10 делители по выходному сигналу второго делителя 18.

При этом вследствие работы первой фазовой автоподстройки период тактового

0 сигнала на выходе первого делителя 6 равен длительности элементарного импульса информационного сигнала с точностью до одного шага коррекции, а частота выходного тактового сигнала второго делителя 10 оп5 ределяется лишь собственной частотой задающего генератора 1. Вследствие разницы частот передающей и приемной сторон образуется фазовое рассогласование указанных выходных сигналов первого и второго делителей 6 и 10. Между выходными сигналами первого 17 и второго 18 делителей также образуется фазовое рассогласование, которое увеличивается с каждым тактом и знак которого, определяемый частотным дискриминатором 12 и формирователем 14, практически не зависит от помех в канале связи. При этом с формирователя 14 поступают импульсный сигнал и сигнал Опережение/отставание на корректор 15, в котором осуществляется прямой или обратный просчет импульсов указанного импульсного сигнала.

В зависимости от режима Опережение или Отставание на одном из выходов корректора 15 появляется тактовая последовательность, частота которой пропорциональна количеству поступивших из формирователя 14 импульсов, каждый из которых изменяет частоту выходной тактовой последовательности корректора 15 на один шаг дискретизации в сторону ее увеличения. Данная тактовая последовательность поступает на второй блок 9 добавления и вычитания, замыкая обратную связь по второй петле автоподстройки, и на первый блок 5 добавления и исключения, улучшая условия работы первой петли фазовой автоподстройки.

Работа частотного дискриминатора 12 и формирователя 14 осуществляется циклически, при периодической установке его в исходное состояние и повторном запуске при условиях подтверждения синхронизма обнаружителем 8. При этом с частотного дискриминатора 12 поступает в блок 13 запуска сигнал, свидетельствующий об окончании цикла его работы. Блок 13 запуска вырабатывает сигналы, запрещающие работу частотного дискриминатора 12, формирователя 14 и второго делителя 10. При условии подтверждения синхронизма обнаружителем 8 осуществляется повторный запуск указанных узлов и фазирование первого и второго делителей 17 и 18. При этом частота сигнала на выходе второго делителя 10 определяется разностью (суммой) частоты задающего генератора 1 и частоты импульсов на выходе корректора 15. Описанный процесс набора данных продолжается до тех пор, пока при заданной длительности цикла частотного дискриминатора 12 становится затруднительным достоверное определение знака фазового рассогласования сигналов на выходах первого и второго делителей 6 и 10 и влияния помех в канале связи, т.е. в режиме Грубо не обеспечивается уверенное определение знака фазового рассогласования.

При этом значение сигнала, считываемое в формирователь 14с частотного дискриминатора 12, не определено и происходит его постоянное изменение в времени. При этом с формирователя 14 поступает импульсный сигнал, число импульсов которого фиксируется пороговым блоком 11, состояние которого изменится, если число указанных импульсов превысит заданное пороговое значение. В этом случае происходит переход в режим работы Точно, в котором динамически осуществляется точное определение разности частот генераторов и ее компенсация с использованием дополнительных ресурсов усредняющего блока 3 путем подключения первого блока 5

добавления и исключения к первому и второму дополнительным выходам усредняющего блока 3. Одновременно увеличивается длительность цикла работы частотного дискриминатора 12 и степень точности о пред еления знака частотного рассогласования тактовых сигналов первого и второго делителей 6 и 10.

Формула изобретения

1. Устройство фазовой автоподстройки тактовой частоты, содержащее последовательно соединенные задающий генератор, блок оценки фазового рассогласования, усредняющий блок, коммутатор, первый блок

добавления и исключения импульсов, первый делитель частоты, формирователь фазовой зоны, обнаружитель синхронизма, тактовый вход которого объединен с тактовым входом первого блока добавления и исключения импульсов и подключен к выходу задающего генератора, последовательно соединенные второй блок добавления и исключения импульсов и второй делитель частоты, вход добавления и вход исключения

второго блока добавления и исключения импульсов подключены соответственно к дополнительному входу добавления и входу исключения первого блока добавления и исключения импульсов, выход первого делителя частоты подсоединен к входу опорного тактового сигнала блока оценки фазового рассогласования, тактовыйвход второго блока добавления и исключения импульсов - к выходу задающего генератора, а установочный вход первого блока добавления и исключения импульсов - к устанавливающему входу второго блока добавления и исключения импульсов, причем информационный вход блока оценки фазового рассогласования, установочный вход дополнительного блока добавления и исключения импульсов и выход первого делителя частоты являются соответственно информационным входом, управляющим входом и выходом устройства,о тличающееся тем, что, с целью

повышения помехоустойчивости, введены последовательно соединенные блок запуска частотного дискриминатора, частотный дискриминатор, формирователь управляющих сигналов частотной автоподстройки и пороговый блок, а также корректор частотного рассогласования, при этом первый и второй дополнительные выходы усредняющего блока подсоединены соответственно к первому и второму дополнительным информационным входам коммутатора, управляющий вход которого объединен с входом сигнала Грубо/точно формирователя управляющих сигналов частотной автоподстройки и подключен к выходу порогового блока, информационный вход которого объединен с установочным входом формирователя управляющих сигналов частотной автоподстройки и подключен к выходу циклов сигналов блока запуска частотного дискриминатора, разрешающий вход, вход синхронизирующего сигнала которого подключены соответственно к выходу обнаружителя синхронизма и первому выходу синхронизирующего сигнала частотного дискриминатора, второй выход синхронизирующего сигнала которого подсоединен к входу стробирующего сигнала формирователя управляющих сигналов частотной автоподстройки, выход первого делителя частоты подсоединен к входам опорного тактового колебания частотного дискриминатора и корректора частотного рассогласования, первый и второй выходы которого подсоединены соответственно к входу добавления и входу исключения второго блока добавления и исключения импульсов, выход задающего генератора подсоединен к тактовым входам блока запуска частотного дискриминатора, частотного дискриминатора и корректора частотного рассогласования, первый и второй управляющие входы которого подключены соответственно к выходу сигнала Опережение/отставание и выходу сигнала Повышение/понижение частоты формирователя управляющих сигналов частотной автоподстройки, выход сигнала блокировки и вход знакового сигнала частотного рассогласования которого подсоединены соответственно к входу сигнала блокировки блока запуска частотного дискриминатора и выходу знакового сигнала частотного рассогласования частотного дискриминатора дополнительный вход опорного тактового сигнала которого объединен с входом опорного тактового сигнала формирователя управляющих сигналов частотной автоподстройки и подключен к выходу второго делителя частоты, управляющий вход которого подключен к выходу сигнала

синхронного запуска, первый и второй выходы усредняющего блока подсоединены соответственно к первому и второму информационным входам обнаружителя синхро- низма, а установочные входы блока запуска частотного дискриминатора и корректора частотного рассогласования подключены к установочному входу второго блока добавления и исключения импульсов.

0 2. Устройство по п. 1, от л и чаю ще е- с я тем, что частотный дискриминатор содержит последовательно соединенные первый делитель частоты и сумматор по модулю два, последовательно соединенные второй

5 делитель частоты, выделитель фронтов сигнала и RS-триггер, первый выход первого делителя частоты подсоединен к второму входу выделителя фронтов, первый вход которого подключен к второму входу суммато0 ра по модулю два, причем тактовый вход и установочный вход первого делителя частоты, тактовый вход и установочный вход второго делителя частоты, тактовый вход выделителя фронтов, второй, третий и чёт5 вертый выходы первого делителя частоты, выход сумматора по модулю два и выход второго делителя частоты являются соответственно дополнительным входом опорного тактового сигнала, входом синхронизирую0 щего сигнала, входом опорного тактового сигнала, разрешающим входом, тактовым входом, выходом стробирующего сигнала Знак частотного рассогласования, выходом сигнала интервала анализа Грубо, вы5 ходом сигнала интервала анализа в режиме Точно, выходом синхронизирующего сигнала.

3. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что корректор частотного рассогла0 сования содержит последовательно соединенные реверсивный счетчик, регистр сдвига, компаратор, элемент ИЛИ, выделитель передних фронтов сигнала, первый счетчик импульсов, второй счетчик импуль5 сов, выходы которого подключены к соответствующим входам компаратора, последовательно соединенные D-триггер и первый элемент ИЛИ-НЕ, а также второй элемент ИЛИ-НЕ и элемент И, входы кото0 рого подключены к выходам регистра сдвига, тактовый вход которого подключен к тактовому входу D-триггера, управляющий вход регистра сдвига объединен с первым входом второго элемента ИЛИ-НЕ и под5 ключей к выходу D -триггера, D -вход которого подключен к выходу старшего разряда реверсивного счетчика, установочный вход второго счетчика импульсов и вторые входы первого и второго элементов ИЛИ-НЕ подключены к выходу выделителя передних

фронтов сигнала, тактовый вход и установочный вход которого подключен соответственно ктактовому входу счетчика импульсов и управляющему входу реверсивного счетчика, а выход элемента И подсоединен к другому входу элемента ИЛИ, причем тактовый вход первого счетчика импульсов, тактовый вход D-триггера, вход- сигнала направления счета, тактовый вход и установочный вход реверсивного счетчик и выход второго и первого элементов ИЛИ-НЕ; являются соответственно тактовым входом, входом опорного тактового сигнала, первым и вторым управляющим входами, установочным входом, первым и вторым выходами корректора частотного рассогласования.

4. Устройство .по. п.1, Р.Т л и ч а ю.щее: с я тем, что формирователь управляющих сигналов частотной автоподстройки Содержит последовательно соединенные выделитель моментов изменения знака сигнала/ первый элемент ИЛИ-НВ,. первый счетчик импульсов, RS-триггер и коммутатор,;последовательно соединенные второй элег мент ИЛИ-НЕ, второй счетчик импульсов, первый и второй элементы И-НЕ, D-f риггер и элемент И, а таюце делитель частоть и элемент ИЛИ, первый вход которого объединен с S-входом триггера и подключен к выходу второго;счетчика импульсов, установочный вход которого подключен к установочному входу; первого счетчика импульсов и второму входу элемента 1/Г, выход первого счетчика импульсов подсоединен к вторым входам первого элемента ИЛИ, выход которого подсоединен к другому входу второго элемента И-НЕ, тактовый вход, синхронизирующий вход и первый и

второй выходы делителя моментов изменения знака сигнала подключены соответственно к тактовым входам D-триггера делителя частоты, инверсному входу второго элемента ИЛИ-НЕ и установочному входу делителя частоты, второй вход первого элемента ИЛИ-НЕ подключен к второму входу второго элемента ИЛИ-НЕ, а выходы делителей частоты и элемента И и информационный вход выделителя моментов изменения знака сигнала подключены соответственно к второму, третьему и четвёртому информационным входам коммутатора, причем тактовый вход,

синхронизирующий вход и информацион- ный вход выделителя моментов изменения знака сигнала, пятый и шестой информационные входы и управляющий вход коммутатора, второй вход первого элемента

ИЛИ-НЕ, установочный вход первого счетчика,импульсов, второй выход выделителя моментов изменения; знака сигнала и пер- -выи, второй и третий выходы коммутатора являются соответственно входом опорного

тактового сигнала, входом стробирующего сигнала, входом знакового сигнала частотного рассогласования,-входом сигнала интервала .анализа Грубо, входом сигнала интервала анализа Точно, входом сигнала

Грубо/точно, входом сигнала величины

частотного рассогласования, установочным

входом и выходом сигнала Повторение знака частотного рассогласования, выходом

сигнала; Опережение/отставание, выходом сигнала Повышение/понижение час- выходом сигнала блокировки формирователя управляющих сигналов час- тртной автоподстррйки.

I

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮаНАЯ i | 1973 |

|

SU372717A1 |

| Устройство автоподстройки фазы тактовых импульсов | 1983 |

|

SU1113893A1 |

| Устройство тактовой синхронизации регенератора | 1985 |

|

SU1283992A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СЛУЧАЙНОЙ СОСТАВЛЯЮЩЕЙ НЕРАВНОМЕРНОСТИ ФАЗО-ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ | 1973 |

|

SU372716A1 |

| Устройство для измерения преобладаний двоичных сигналов | 1985 |

|

SU1246396A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство приема зондирующего сигнала | 1987 |

|

SU1566495A1 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ | 1973 |

|

SU375772A1 |

Изобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации для тактовой синхронизации. Целью изобретения является повышение помехоустойчивости. Устройство фазовой автоподстройки тактовой частоты содержит задающий генератор 1, блок 2 оценки фазового рассогласования, усредняющий блок 3, коммутатор 4, первый блок добавления и исключения импульсов 5, первый делитель 6 частоты, формирователь 7 фазовой зоны, обнаружитель 8 синхронизма, второй блок добавления и исключения 9 импульсов, второй делитель 10 частоты, пороговый блок 11, частотный дискриминатор 12, блок запуска 13 частотного дискриминатора, формирователь 14 управляющих сигналов частотной автоподстройки и корректор 15 частотного рассогласования. При полном устранении фазового и частотного рассогласования, принимаемого из канала связи импульсного сигнала и выходного тактового сигнала устройства, обнаружитель 8 выдает сигнал, по которому степень усреднения информации в устройстве увеличивается. 3 з.п. ф-лы, 5 ил.

| Устройство тактовой синхронизации | 1980 |

|

SU869074A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР Мг 1438585, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-03-23—Публикация

1989-03-23—Подача