1

Изобретение относится к вычиспитепьной технике,в частности к устройствам для контроля импульсных схем, преимущественнорегистров сдвига, кольцевых и двончны.х счетчиков, цепей логических преобрааователей и другах схем, работающих на жесткой временной основе, на; отсутствие перемещающихся и устойчивых отказов с индикацией Отказавшего элемента.

Известно такого типа устройство - оно многоэлементно, и кроме того, схема его существенно усложняется при увеличении длины контролируемых импульсных схем 1 .

Наиболее близким техническим решением к изобретению является устройство для контроля импульсных схем, содержащее группу триггеров, индикатор и генератор импульсов первый вьрсод которого соединен с первым входом элемента запрета, а второй выход, с первыми входами контролируемой и эталонной импульсных схем 2j .

Цель изобретения - упрощение локализации неисправного элемента.

Достигается это благодаря тому, что устройство содержит группу элеменюв ИЛИ,

элемент ИЛИ, Элемент задержки, интвгрирующий и пороговый блоки, причем выходы контролируемой и эталонной импульсиыт схем через группу элементов ИЛИ соедяяекы с аходами группы триггеров, выходы котоpbtx соединены с индикатором и с аходамк элемента ИЛИ, выход злемента ИЛИ черев интегрируюпшй и пороговый блоки соадинея с вторым входом элемента запрета, быход которого соединен с вторым оходом контролируемой импульсной схемы и через элемент задержки-с вторым входом эталонной импульсной схемы.

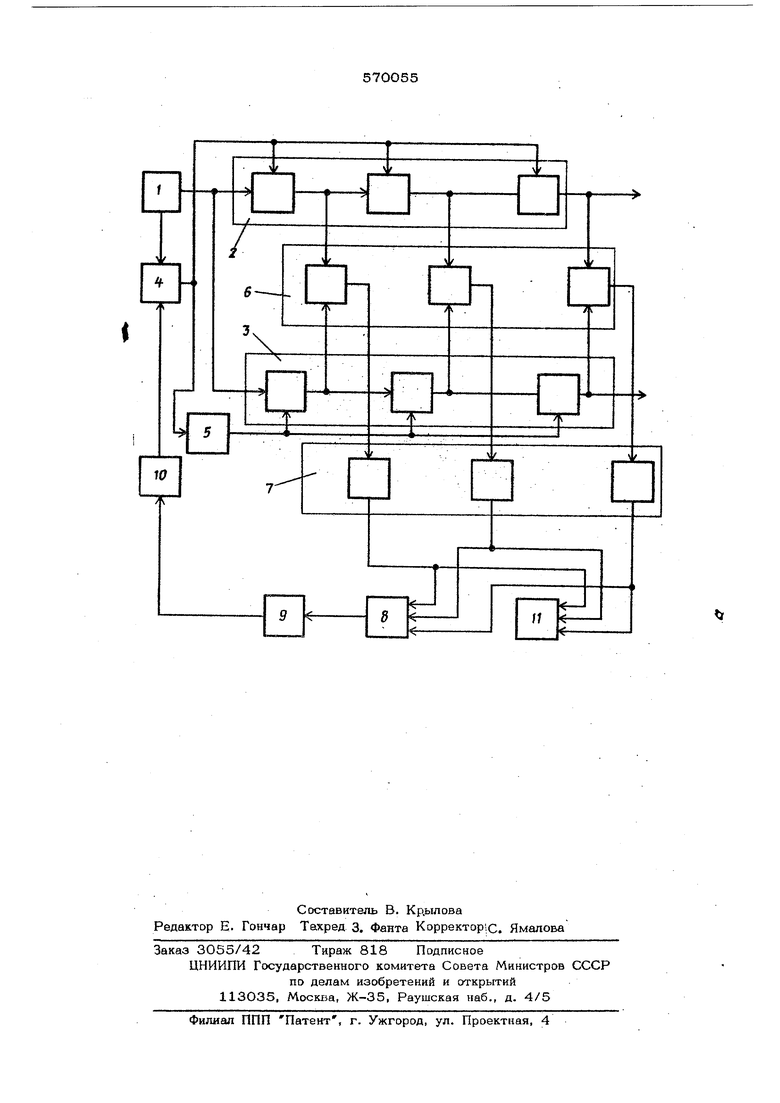

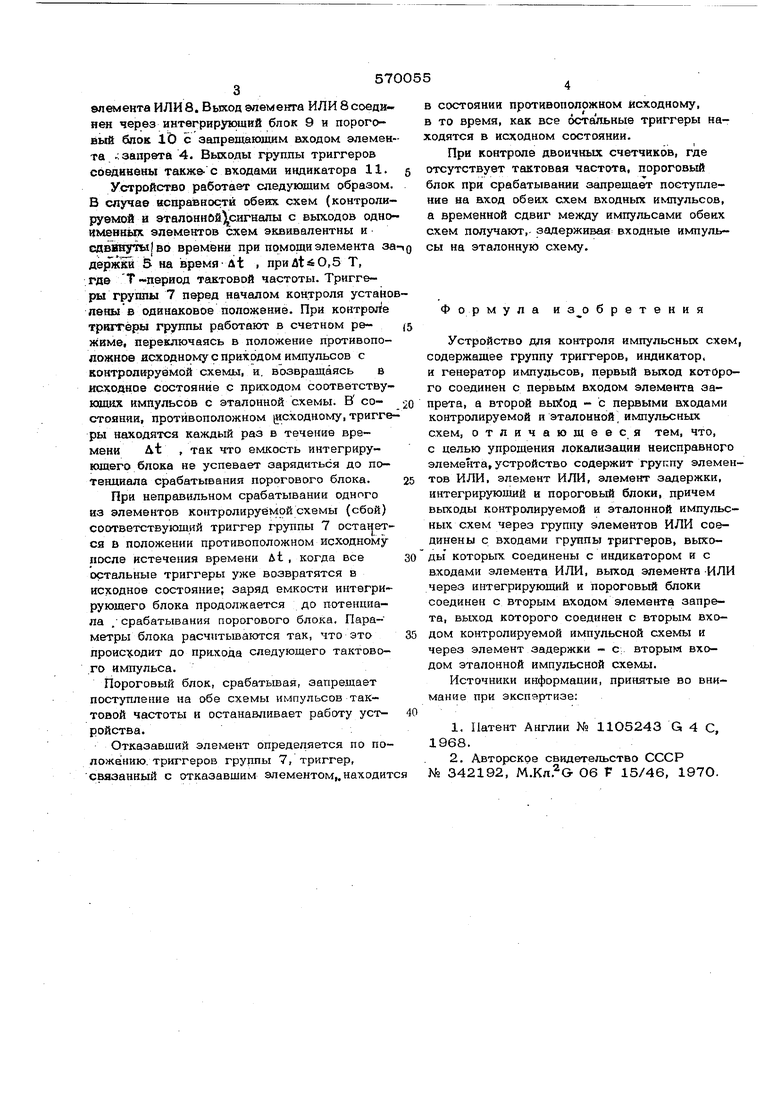

На чертеже дана блок-схема предложенного устройства.

Генератор импульсов 1 соединен с входами контролируемой 2 и эталонной 3 схем. Тактовая частота с генератора импульсов подана на обе схемы через элемент запрета 4 и на эталонную схему через элемент задержки 5. Выходы 1 одноименных элементов контролилуемойи эталонной схем соединеныс входами группыб элементов ИЛИ, выхоцыкоторых соединены с входами группы 7 триггеров, Выходыгруппы триггеров соединеныс входам элемента ИЛИ 8. Выход aneweirra ИЛИ 8 соединен через интегрирующий блок 9 и пороговый блок 1.0 с запрещающим входом элемен та -запрета 4. Выходы группы триггеров соединены также- с входами индикатора 11. Устройство работает следующим образом. В случае исправности обеих схем (контролируемой и эталоннйй сигнапы с выходов одно Нмавньгх элементов схем эквивалентны и едввнуты|во времени при помощи элемента за яернс1й 5 на время At npHat O,5 Т, где Т период тактовой частоты. Тригге ры группы 7 перед началом контроля устано лены в одинаковое положение. При контроле триггеры группы работают в счетном режвме| переключаясь в положение противоположное исходному с приходом импульсов с контролкруёмой схемы, и, возвразцаясь в JHCXOAHoe состояние с приходом соответствующах импульсов с эталонной схемы. В соСТОЯНИИ, противоположном ИСХОДНОМУ, тригге ры находятся каждый раз в течение времени At , так что емкость интегрируюшего блока не успевает зарядиться до потенциала срабатывания порогового блока. При неправильном срабатывании одного из элементов контролируемой схемы (сбой) соответствующий триггер группы 7 останется в положении противоположном исходному после истечения времени &t , когда все остальные триггеры уже возвратятся в исходное состояние; заряд емкости интегрирующего блока продолжается до потенциала . срабатывания порогового блока. Параметры блока расчнтьтаются так, что это проист одит до прикода следующего тактово.го импульса. Пороговый блок, срабатывая, запрещает поступление на обе схемы импульсов тактовой частоты и останавливает работу устройства. Отказавший элемент определяется по положению, триггеров группы 7, триггер, связанный с отказавшим элементом,.находитс в состоянии противоположном исходному, в то время, как все остальные триггеры находятся в исходном состоянии. при контроле двоичных счетчиков, где отсутствует тактовая частота, пороговый блок при срабатывании запрещает поступление на аход обеих схем входных импульсов, а временной сдвиг между импульсами обеих схем получают, задерживая входные импульсы на эталонную схему. Формула и бретения Устройство для контроля импульсньи схем, содержащее группу триггеров, индикатор. и генератор импульсов, первый выход которого соединен с первым входом элемента запрета, а второй выХод - с первыми входами контролируемой и эталонной импульсных схем, отличающееся тем, что, с целью упрощения локализации неисправного элемента, устройство содержит группу элементов ИЛИ, элемент ИЛИ, элемент задержки, интегрирующий и пороговый блоки, причем вьпсоды контролируемой и эталонной импульсных схем через группу элементов ИЛИ соединены с входами группы триггеров, выходы которых соединены с индикатором и с входами элемента ИЛИ, выход элемента -ИЛИ через интегрирующий и пороговый блоки соединен с вторым входом элемента запрета, выход которого соединен с вторым входом контролируемой импульсной схемы и через элемент задержки - с вторым входом эталонной импульсной схемы. Источники информации, принятые во внимание при экспертизе: 1.Патент Англии № 1105243 G 4 С, 1968. 2.Авторское свидетельство СССР № 342192, М.Кл.О 06 F 15/46, 1970.

«

fn

f

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для испытания электронных логических схем | 1984 |

|

SU1262430A1 |

| Устройство для контроля группы цифровых узлов | 1987 |

|

SU1534461A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для управления реверсивным тиристорным широтноимпульсным преобразователем | 1976 |

|

SU657568A1 |

| Многоканальное устройство для программного управления | 1978 |

|

SU739478A1 |

| Устройство для контроля производитель-НОСТи ОдНОКОВшОВОгО эКСКАВАТОРА | 1977 |

|

SU812891A1 |

| Ультразвуковой уровнемер | 1985 |

|

SU1364889A1 |

| Устройство для контроля параметров объектов | 1989 |

|

SU1695270A1 |

| Устройство для контроля скорости вращения вала электродвигателя | 1981 |

|

SU966595A1 |

| Многоканальное устройство для контроля систем регулирования | 1977 |

|

SU734624A1 |

11

Авторы

Даты

1977-08-25—Публикация

1971-03-22—Подача