1

Изобретение относится к /передаче информации и может использоваться в адаптивных многоканальных цифровых телеметрическах системах для помехоустойчивости передачи сообщений с малой избыточностью.

Известно устройство для передачи цифровых многоканальных сообщений, содержаще синхронизатор, аналого-цифровой преобразова ель, элемент равнозначности, генераторы М-последовательностбй , блоки элементов И и элемент ИЛИ i .

Однако в известном устройстве снижается помехоустойчивость передачи сообщений при сокращении избыточности исходного сигнала.

Цель -изобретения - повьииение помехоустойчивости передачи при сокращении избыточности исходного сигнала.

Для этого в устройство для(передачи циф ровых многоканальных сообщений, содержащее синхронизатор, аналого-цифровой преобразователь, элемент равнозначности, генераторы М последовательностей, блоки элементов И в элемент ИЛИ, коммутатор и анали;затор каналов ,блок памяти, преобразбватель параллельного кода в последовательный, ,старт-стопный .запоминающий блок, задержки и последовательно соединенные счетчик и дешифратор. Выход коммута тора каналов подключен к входу аналогоцифрового преобразователя, выходы которог подключены к анализатора каналов непосредственно и через блок памяти, а через последовательно соединенные первый блок элементов И и преобразователь :параллельного кода в последовательный -;к входу элемента равнозначности. При этом анализатора каналов подклкиен к дру;гим входам первого блока элементов И и через элемент задержки к входам второго блока элементов И. Его входысоединены с

выходами дешифратора, а выходы второго блока элементов И подключены через соответствующие iгенераторы М-последова. тельностй к входам элемента ИЛИ, выход которого подключен к другому входу элемента равнозначности, В1яход которого подключен к аходу старт-стопного запоминающего блока, второй вход которого соединен с выходом другого генератора М-последовательности, управляюший вход которого и управляющие входы коммутатора каналов, блока памяти и счетчика соединены с соответствуюшими выходами сиахрониэа ора.

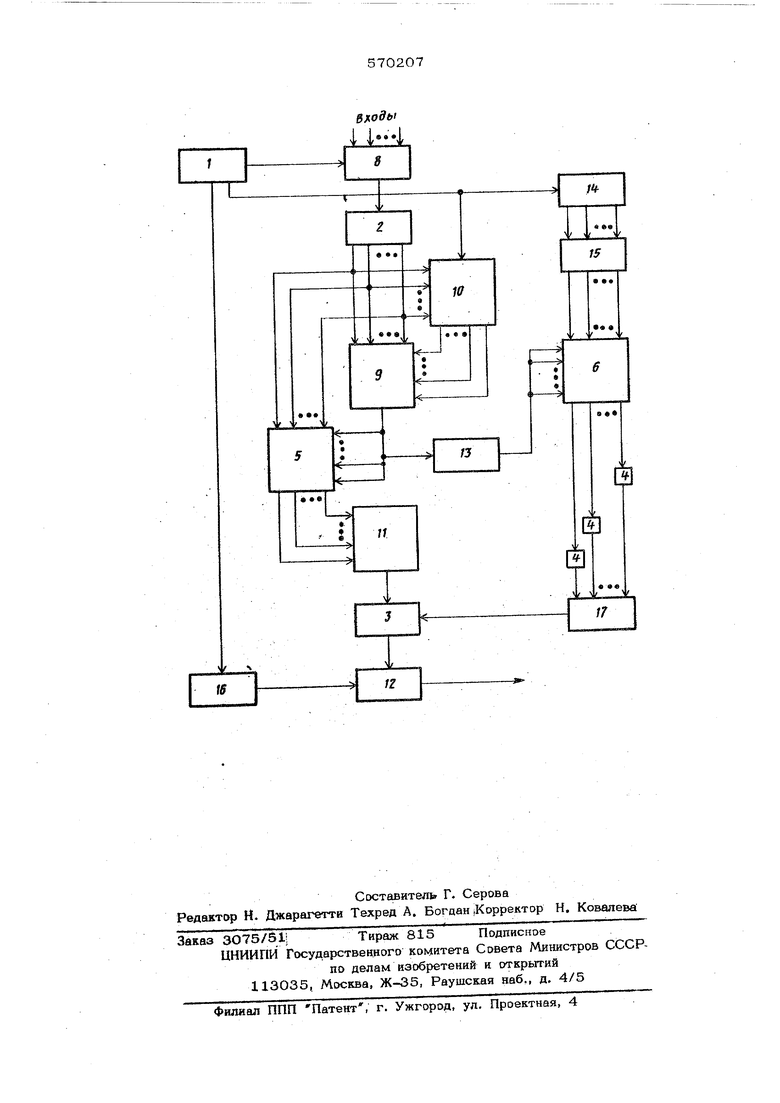

На чертеже изображена структурная электрическая схема предлагаемого устройства. Оно содержит синхронизатор 1, аналогоцифровой преобразователь 2, элемент равноаначностн 3, генераторы М - последовательнс стей 4, блоки элементовИ 5,6 и элемент ИЛИ 7, коммутатор 8, анализатор. 9 каналов, блок памяти 10, преобразовател параллельного кода в последовательный 11, старт-стопный запом1гааюший блок; 12, эле- мен задержки 13 и последовательно соединенные счетчик 14 и дешифратор 15, причем выход коммутатора 8 каналов под5и}Ючен к входу аналого-цифрового преобразова :епя 2, выходы которого ппдк 1ючены к входам анализатора 9 каналов непосредственно и через блок памяти 10, а через последовательно соединенные первый блoк элементов И 5; и преобразователь параллельного кода в последовательный 11 к входу элемента равнозначности 3, Выход анализатора 9 каналов подключен к другим входам первого блока элементов И 5, и через элемент задержки 13 к входам второго блока элементов И 6, другие входы которого соедииены с выходами дешифратора 15, а выходы Второго блока элементов И 6 подключены через соответствующие генераторы М-последовательностей 4 к входам элемента ИЛИ 7 выход которого подключен к другому входу элемента равнозначности 3, выход которого подключен к входу старт стопного запоминающего блока 12, второй вход которого соединен с выходом другого генератора Мпоследовательности 16, Его управляюший вход и управляющие входы коммутатора каналов 8, блока памяти 10 и счетчика 14 соединены с соответствующими выходами синхронизатора 1.

Устройство работает следующим образом Сигналы си1кронизатора 1 управляют работой коммутатора 8 каналов с помощью которого на вход аналого-цифрового преобразователя 2 поочередно поступают сигналы всех W канапов, авсчетчйке 14будетфик- сирова/гься двоичный адрес текущего канала. Аналого-цифровой преобразователь 2 в соответствии с амплитудой входного сигнала вырабатывает кодовую комбинацию в виде параллельного двоичного кода.Разряды кодовых комбинаций по соответствующим шинам подаются на входы анализатора -Q 1саналов к блока памяти 10, С его выхода снимается кодовая комбнз ация в параллель- ном коде, отображающая, значение сигнала

4

данного канала в точке отсчета, нредшествуюшей рассматриваемой и отстоящей на время равное периоду опроса. В.ходная и выходная кодовые комбинации сравниваются в анализаторе 9 . .каналов. Если абсолютная величина разности ах значений меньше заданной величины.то на выходе анализатора 9 каналов сигнал отсутствует,при этом блоки элементов И 5 и 6 будут закрыты по управляющим входам. Вследствие этого разряды информационной кодовой комбинации на входы преобразователя параллельного кода в последовательный 11 не поступают. По этой же причине не может поступить запускающий сигнал с выхода данного канала дешифратора 15 на вход соответствующего генератора М-последоват льности 4. Если указан- ная разность превышает по асболютной величине заданную, то на выходе анализатора каналов 9 образуется управляюший сигнал, который открывает первый блок, элементов И 5, и текущая кодовая комбинация поступает на В.ХОД преобразователя параллельного кода в последовательньШ 11, Этот же управляющий сигнал с выхода анализатора 9 , каналов, задержанный элементом задержки 13 на время преобразования параллельного кода в ;-последовательный, поступает на входы второго блока элементов И 6, и запускающий сигнал данного канала с соответствующего выхода дешифратора 15 подается для запуска генератора М-последовательности 4 данного канала, который вырабатывает циклическую М-последовательность, длительность которой равна длительности одного символа (О или 1) информационной двои1ной комбинации, а количество циклов равно числу разрядов информационной двоичной Комбинации,

Таким оразом, на входы элемента равнозначности 3 одновременно подаются один двоичный разряд информационной комбинации с выхода. преобразователя параллельного кода в последовательный 11 и М-последовательность с выхода элемента ИЛИ 7 струтуры, присущей только номеру данного ка. нала. На выходе элемента равнозначности 3 б5Дут последовательно сформированы Мпоследовательности структуры данного номера канала, промодулированные инфсрмационно двоичной кодовой комбинацией также данного канала (символу i соответствует прямая М-последовательность, а символу О обратная). Аналогичным образом в предлагаемом устройстве будут сформированы Мпоследовательности структур, соответствук щнх номерам каналов, по которым текущие информационные кодовые комбинации являются существенными (неизбыточными). Стартстопный запоминающий блок 12 обеспечи Вает сдвиг М-послбдовательностей|неизбыто ных каналов к началу кадра передачи инфор .мании за счет свободных канальных интерв лов с избыточными выборками и равномерную вьщачу сообщений в канал связи. В старт-стопный запоминающий блок 12 с вы.хода Другого генератора М-последовательно ти 16 (маркера кадра) периодически с частотой опроса каналов поступает синхронизирующая последовательность, которая nep дается в начале каждого кадра и испотьзуется на приемной стороне для синхронизации местного яронизатора. ормула изобретения . Устройство для передачи цифровых многоканальных сообщений, содермсашее синхронизатор, аналогс5-цифров1гй Преобразователь элемент равнозначности, генераторы Мпоследовательностей, блоки элементов И и аяемент ИЛИ, отличаюшееся тем, что, с целью повышения помехоустойчивости передачи при сокращении избыточности исходного , введень коммутатор каналов, анализатор каналов, блок памяти, преобразователь параллельнсяго кода в последовательный, старт-стопный запоминаю щий блсук, элемент задержки н последовател но соединенные счетчик и дешифратор, причем выход Коммутатора каналов подключен к входу аналого-цифрового преобразоватея я, выходы которого подключены ч входам анализатора каналов непосредственно и черс блок памяти, а через последовательно соединенные первый блок элементов И и преобразователь параллельного кода в последовательный - к входу элемента равноаначности, при этом выход анализатора каналов подключен к входам первого блока элемеиITOB И и через элемент задержки - к входак второго блока элементов И, другие входы которого соединены с выходами дешифруетера, а выходы второго блока элементов И подключены через соответствующие генера-, торы М-последовательностей к входам элемента ИЛИ, выход которого подключен к другому входу элемента равнозначности, выход которого подключен к входу стартстопного запоминающего блока, второй вход которого соединен с выходом друго- го генератора М-сгоследовательности, управляющий вход которого и управляющие входы коммутатора каналов, блока памяти и счетчика соединеиъ с соответствующими выходами синхронизатора. 1. Венедиктов М. Д. и др. Асинхронные адресные системы связи. М,, Связь , 1968, с. 49-5О.

елоды

U±i4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи многоканальных сообщений разностными сигналами | 1984 |

|

SU1223386A1 |

| Устройство для уплотнения многоканальных сообщений с кодоимпульсной модуляцией | 1986 |

|

SU1365106A1 |

| Система передачи и приема сообщений | 1977 |

|

SU734781A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для уплотнения многоканальных сообщений с кодо-импульсной модуляцией | 1977 |

|

SU619944A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ОБРАБОТКИ ИНФОРМАЦИИ МНОГОКАНАЛЬНОЙ ТЕЛЕМЕТРИЧЕСКОЙ СИСТЕМЫ | 1967 |

|

SU215267A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

Авторы

Даты

1977-08-25—Публикация

1975-12-16—Подача