1

Изобретение относится к технике связи и телеметрии.

Известны устройства для сжатия данных путем дельта-модул$щии jl , содержащее коммутатор, преобразователи, логические элементы. В этом устройстве в линию связи передают дельта-посылки 1 61 , а для уменьшения ошибок накопления периодически посылают П-значные кодовые сигналы, отображающие полные значения выборок. Недостатком устрой- . ства является появление ошибок перегрузки.

В другом устройстве для сжатия сообщения используются синхронизатор, коммутатор каналов, преобразователь аналог-цифра, блок сокращения избыточности, а также блоки кодирования времени и адреса. Поток существенных выборок, наделенных адресной и временной инфор- мшхией, записывается в старт-стопном запоминающем устройстве .

Наиболее близким по технической сущности к предложенному является система передачи и приема сообщений З , содержащая на передающей стороне коммутатор каналов, входы которого подключены к входам системы, синхрони31ФУЮЩИЙ вход - к первому выходу син)фонизатора, вторрй выход которого и выход коммутатора каналов соответ ственно соединены с первым и вторым входами аналого-цифрового преобразователя, преобразователь параллельного кода в последовательный, выход которого через канал свази подключен на приемной стороне ко входу преобразователя последовательного кода в параллельный .

К недостаткам известных устройств относится формирование неравномерного потока существенных выборок, которые должны наделяться адресной частью и привязываться к временной шкале. Дпя выравнивания этого потока требуется буферное запоминающее устройство.

Для значительного числа сообщений частота дискретизации обьгчно выб1фается завышенной. При этом Р { А О)Р (А ±1) Р (л 12) где Р(д 0)

вероятность того, что для данного процесса приращения между соседними выборками , для Р (А il) величина 2 и т.д. В этом случае можно сжимать объем цифрового сигнала путем преобразования п- аарядных слов (кодовых комбинаций), отображающих значения выборок, а {п-1)-разрядные при погрешности квантования еньг,,где б„вп 6 в среднеквадратические погрешности соответственно для п u(n-l) - разрядного кодов. Указанное сжатие объема сигнала можно реализовать как в синхронных, так и в асинхронных системах. Во втором случае преполагается, что асинхронный поток п -разрядных выборок получается после сжатия с использованием экстрапошггора нулевого порядка, если ширина зоны допустимых отклонений исходного сообщения А (t ) относительно последней существенной выборки Д 1.

Целью изобретения является повышение информативности и надежности системы.

Указанная цель достигается тем, что в систему на передающей стороне . введены блоки ключевых элементов, преобразователь сигнала, элемент ИЛИ и триггер, счетный вход которого соединен с третьим выходом синхронизатора. Инверсный и прямой выходы триггера подключены к управляющим входам соответственно первого и второго блоков ключевых элементов, п -1 выходов аналого-цифрового преобразователя соединены с информационными входами первого и второго блоков ключевых элементов, п-й выход подключен к соответствующем входу второго блока ключевых элементо П -1 выходов первого и п выходов второго блоков ключевых элементов под-, ключены соответственно к первым входа -1 элементов ИЛИ и к п входам преобразователя сигнала, п -1 выходов которого соединены со вторыми входами г -1 элементов ИЛИ, выходы которых подключены ко входам преобразователя параллельного кода в последоватвльный} на приемной стороне введены блок задержки, сумматор, блоки элементов И, HHBejrrop, элементы ИЛИ и блок анализа, первые входы которого, первые входы сумматора, п -1 входов первогчэ

блока элементов И и блока задержки подключены к выходам преобразователя Iпоследовательного кода в параллельный, выходы блока задержки соединеньг со

вторыми Входами блока анализа и сумматора, выходы которого подключены ко входам второго блока элементов И, управляющий вход которого и вход инвертора соединены с выходом блока анализа, выходинвертора подключен к управляющему входу первого блока элементов И, п -1 выходов которого и второго блока элементов И соединены с соответствующими входами элементов И,

5 выходы которых и п -и выход второго блока элементов И подключены к выходам системы.

Блок анализа содержит группы элементов равнозначности, элементы И и

0 ИЛИ, группу элементов И, инверторы, выходы которых соединены с первыми входами элементов равнозначности первой группы, вторые входы которых и первые входы элементов равнозначности вто рой группы подключены ко вторым входам блока анализа. К первым блока анализа подключены входы инверторов и вторые входы элементов равнозначности второй группы, выходы которых соедине ны через элемент И с управляющим входом элемента ИЛИ, Выходы элементов равнозначности первой и второй групп подключень к соответствующим входам группы элементов И, выходы которых

5 соединены с п -1 входами элемента ИЛИ, выходом подключенного к выходу блока анализа.

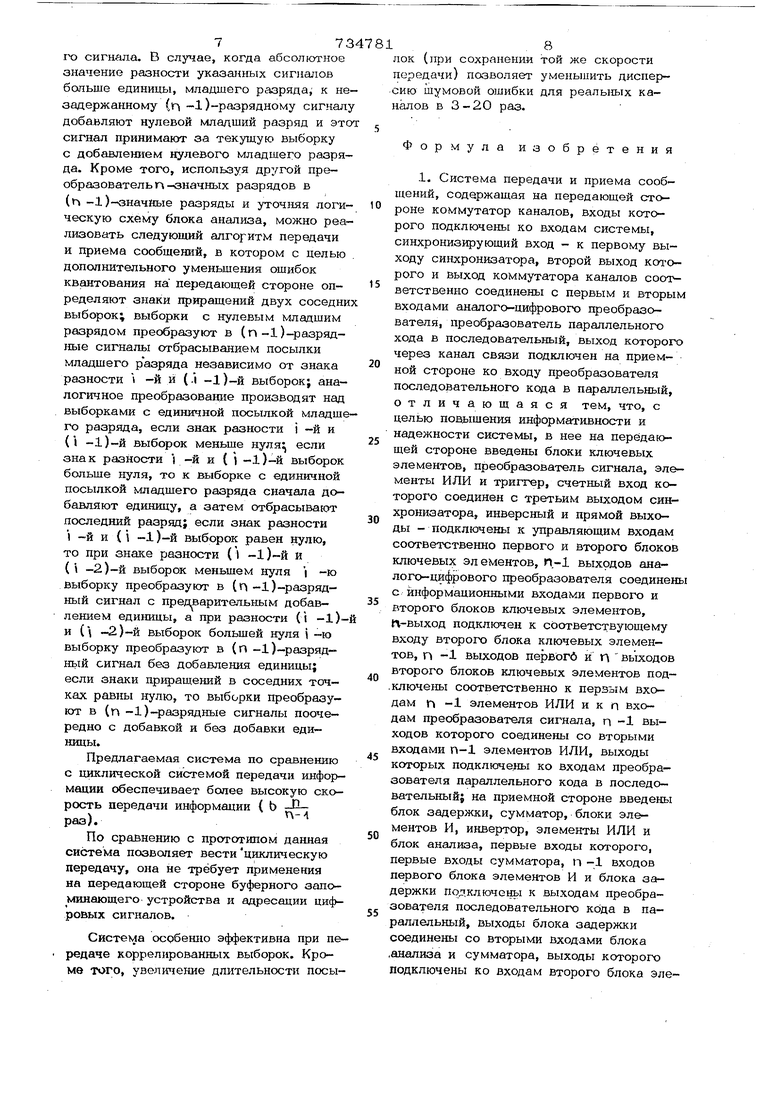

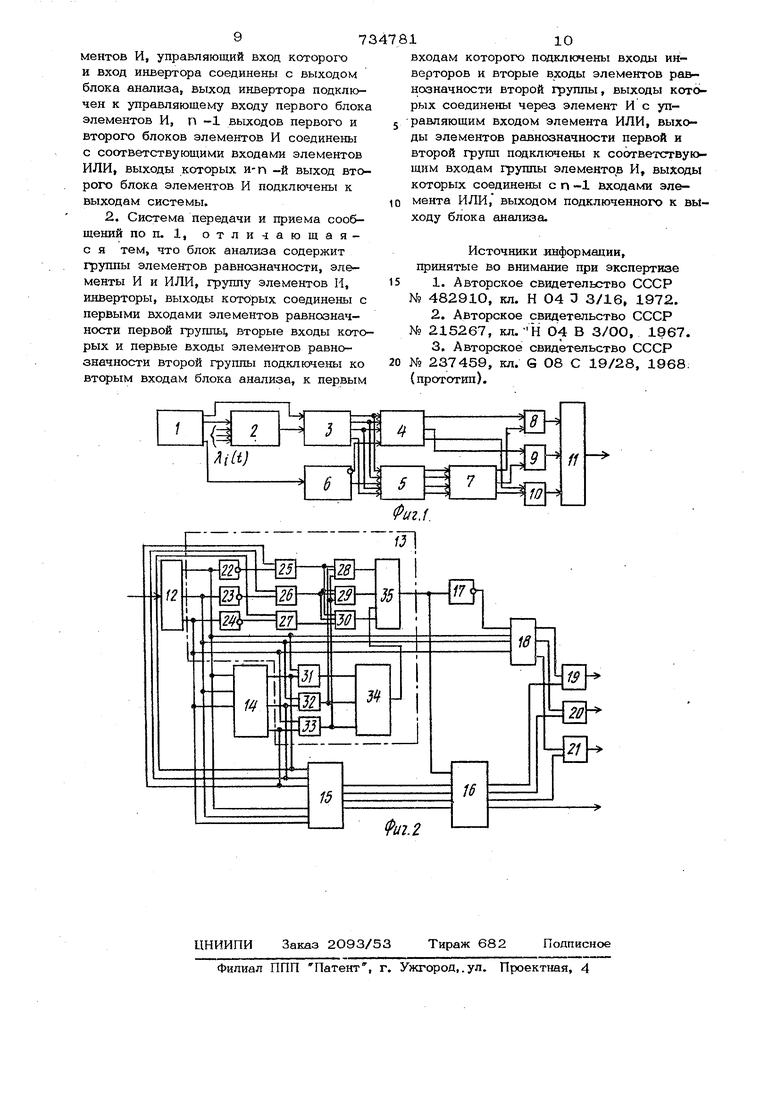

Видеотракт предлагаемой системы передачи сообщений состоит из передающей стороны (фиг. 1) и приемной стороны (фиг. 2).

Передающая сторона (фиг. 1) содержит синхронизатор 1, коммутатор 2 каналов, аналого-цифровой преобразователь 3, блоки 4 и 5 ключевых элементов (первый и второй), триггер 6, преобрагзователь 7 сигнала, элементы ИЛИ 8-1О Щ)еобразователь 11 параллельного кода в последовательный.

Приемная сторона (фиг. 2) включает в себя преобразователь 12 последовательного кода в параллельный, блок анализа 13, блок задержки 14, сумматор 15, первый блок 16 элементов И, инвертор 17, второй блок 18 элементов И, элементы ИЛИ 19-21. Блок анализа 13 содержит инверторы 22-24, элементы равнозначности 25-27 первой группы. эпементы И 28-30, элемокты равкознач ностн 31-33 второй группы, элемегпИ 34, элемент ИЛИ 35, Рассмотрим работу системы. Преобразователь 3 формирует п -разрядшзсе сигналы с nocTOHHHoff частотой FQ . С той же частотой перебрасывается триг гер 6. С выхода преобразователя 3 t -разр5щный сигнал поступает в блок 5 ключевых элементов, ключи которого отпираются сигналами с прямого выхода триггера 6. Этот же сигнал, но без последнего младшего разряда, подается в блок 4 ключевых элементов, ключи ксугорого отпираются сигналами с инверс ного выхода триггера 6. Выход блока 5 связан с преобразователем 7, в котором из п -разрядного сигнала фор у1ируется ()-разрядный сигнал. Если входной сигнал содержит в младшем разряде О, то эта посылка отбрасывается. Если посылка младшего разряда 1, то, добавляя к числу, которое отображается этим сиг налом, единицу, получают новый сигнал с нулем в младшем разряде, а затем посылку младшего разряда отбрасывают. На выходе переда ощей стороны получает ся поток чередующихся (п-1)-разр5Здных сигналов, поступающих с выхода блока 4 и преобразователя. Принятые )-разр1Вдные сигналы помощью преобразсжателя 12 (фиг. 2) преобразуются в параллельную форму. Затем эти сигналы подаЕотся параллельно на первую группу входов блсжа 13 анализа, сумматора 15, блока 18 элементов И и блока задержки 14 с выхода которого сигнал подается на вторую группу входов сумматора 15 и блока 13 анализа. В сумматоре 15 прямой и задержанный на период повторе ния сигналы суммируются и формируются п-разрядные сигналы. В блоке 13 анализа путем сравнения прямого н задержанного сигналов вьфабатывается сигнал со ветствия, который равен 1, если разность двух )-разрядных сигналов не превышает единицы младшего разряда. Если разность больше единицы младшего (H-l)-разрядного сигнала, то вьфабаты- вается сигнал О. Сигнал 1 отпирает блок 16 элементов И, через который проходит П -раз рядный сигнал суммйтора 15. Этот же сигнал через инвертор 17 поступает в блок 18 элементов И, который при этом остается запертым. Сигнал О, пройдя через инвертор 17, отпирает блок 18, через который проходит ()разрядшяй сигнал, полученный на выходе преобразователя 12. BBsiay того, что при управляющем сюгнале блока 13, равном О, блок 16 заперт, то (п -1)разряд1и--1й сигнал с выхода блока 18 поступает поразрядно на эле менты ИЛИ 19-21 и проходит чарез шсс на выход системы, Младший разряд выходного п-разрядного сигнала при этом пол чается равным нулю. Уменьшение объема сигнала за счет перехода к (п-1)-значнь1м кодовым сигналам ведет к возрастанию дисперсии ошибок квантования в 4 раза, в предложенной системе осуществляется уменьшение объема сигнала при передаче коррелированных выборок путем перехода к (п-1)-значнь1м кодовым сигналам с погрешностью квантования .меньшей, чем для (п -1)- начного кода. При коррелированности выборок для дискретно-квантованного сообщения вероятности Р ()Р )Р ()... т.е. вероятность нулевого приращения . квантованной выборки относительно предьщущей больше вероятности приращения. на величину, равную шагу квантования (Д 1) и т.д. В предложенной системе могут быть реализованы различные алгоритмы преобразования (п -1)-значных кодовых сигналов, отображающие величины выборок, например, поочередным тфеобразованием в (п-1)-значные си1 налы двумя методами, используя различные преобразователи из п-в (п -1)- значные сигналы. Первый метод применяют по отношению к четным выборкам (по порядку их следования), а второй - к нечетным. Первый - связан с отбрасыванием посылки младшего разряда п-разрядного сигнала независимо от его качества. При втором методе такую же операцию производят с сигналами, оканчивающимися нулевой посылкой, а к сигналам, оканчивающимся единичной посылкой, перед отбрасыванием посылки младшего разряда добавляют по модулю вторую единицу. На приемной стороне сравнивают между собой два соседних (п -1)-разрядных сигнала, для чего один из них задерживают на величину, равную его длительности. В случае их равенства или отличия на единицу младшего (п -1)-разрядного сигнала производят суммирование по модулю два этих двух си гналов с представлением текущей выборки в виде п -разрядно73го сигнала. В случае, когда абсолютное значение разности указанных сигналов больше единицы, младшего разряда; к не задержанному С п -1)-разрядному сигнал добавляют нулевой младший разряд и это сигнал принимают за текущую выборку с добавлением нулевого младшего разряда. Кроме того, исполкзуя другой преобразователь п-значных разрядов в ( -1)-значйые разряды и уточняя логи ческую схему блока анализа, можно реа лизовать следующий алгоритм передачи и приема сообщений, в котором с целью дополнительного уменьшения ошибок квантования на передающей стороне определяют знаки приращений двух соседни выборок; выборки с нулевым младшим разрядом преобразуют в (п-1)-разрядные сигналы отбрасыванием посылки младшего разряда независимо от знака разности -и и (.1 -1 )-й выборок; аналогичное преобразование производят над выборками с единичной посылкой младш го разряда, если знак разности i -и и (l -1)-и выборок меньше нуля если знак разности 1-й и ( -1)-й выборок больше нуля, то к выборке с единичной посылкой младшего разряда сначала добавляют единицу, а затем отбрасывают последний разряд; если знак разности 1 -и и ( -1 )-й выборок равен нулю, то при знаке разности (| -1)--й и ( -2)-и выборок меньшем нуля i -ю выборку преобразуют в (п-1)-разрядный сигнал с предварительным добавлением единицы, а при разности (i -l) и ( -2)-и выборок большей нуля i -ю выборку преобразуют в (п -1)разряд- нь1й сигнал без добавления единицы; если знаки приращений в соседних точках равны нулю, то выборки преобразуют в (п -1)-разрядные сигналы поочередно с добавкой и без добавки единицы. Предлагаемая система по сравнению с циклической системой передачи информации обеспечивает более высокую скорость передачи информации ( b -ЕЦ Т т По сравнению с прототипом данная система позволяет вести циклическую передачу, она не требует применения на передающей стороне буферного запоминающего устройства и адресации циф ровых сигналов. Система особенно эффективна при пе редаче коррелированных выборок. Кроме того, увеличение длительности посы ок (при сохранении той же скорости ередачи) позволяет уменьшить дисперию шумовой ошибки для реальных каалов в 3-20 раз. Формула изобретения 1. Система передачи и приема сообщений, содержащая на передающей стороне коммутатор каналов, входы которого подключены ко входам системы, синхронизирующий вход - к первому выходу синхронизатора, второй выход которого и выход коммутатора каналов соответственно соединены с первым и вторым входами аналого-цифрового преобразователя, преобразователь параллельного хода в последовательный, выход которогх через канал связи подключен на приемной стороне ко входу преобразователя последовательного кода в параллельный, отличающаяся тем, что, с целью повышения информативности и надежности системы, в нее на передающей стороне введены блоки ключевых элементов, преобразователь сигнала, элементы ИЛИ и триггер, счетный вход которого соединен с третьим выходом синхронизатора, инверсный и прямой выходы - подключены к управляющим входам соответственно первого и второго блоков ключевых элементов, П-1 выходов аналого-цифрового преобразователя соединены с информационными входами первого и второго блоков ключевых элементов, Л-выход подключен к соответствующему входу второго блока ключевых элементов, п -1 выходов пе рвог6 и п выходов второго блоков ключевых элементов под.ключены соответственно к первым входам п -1 элементов ИЛИ и к п входам преобразователя сигнала, п -1 выходов которого соединены со вторыми входами п-1 элементов ИЛИ, выходы которых подключе.ны ко входам преобразователя параллельного кода в последовательный; на приемной стороне введены блок задержки, сумматор, блоки элементов И, инвертор, элементы ИЛИ и блок анализа, первые входы которого, первые входы сумматора, п -1 входов первого блока элементов И и блока задержки подключень к выходам преобразователя последовательного кода в параллельный, выходы блока задержки соединены со вторыми входами блока .анализа и сумматора, выходы которого подключены ко входам второго блока элементов И, управляющий вход которого и вход инвертора соединены с выходом блока анализа, выход инвертора подключен к управляющему входу первого блока элементов И, п -1 выходов первого и второго блоков элементов И соединены с соответствующими входами элементов ИЛИ, выходы которых и-п -и выход второго блока элементов И подключены к выходам системы. 2. Система передачи и приема сообщений ПОП.1, отлитсающаяс я тем, что блок анализа содержит группы элементов равнозначности, элементы И и ИЛИ, группу элементов И, инверторы, выходы которых соединены с первыми входами элементов равнозначности первой группы. Вторые входы кото рых и первые входы элементов равнозначности второй группы подключены ко вторым входам блока анализа, к первым 7 1 входам которого подключены входы инверторов и вторые входы элементов рав нозначности второй группы, выходы которых соединены через элемент И с управляющим входом элемента ИЛИ, выходы элементов равнозначности первой и второй групп подключены к соответствующим входам группы элементов И, выходы которых соединены с п -1 входами элемента ИЛИ, выходом подключенного к выходу блока анализа. Источники лнфор мадии, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N9 482910, кл. Н 04 О 3/16, 1972, 2.Авторское свидетельство СССР № 215267, кл. -Н О4 В 3/00, 1967. 3.Авторское свидетельство СССР № 237459, кл. G О8 С 19/28, 1968. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Устройство для передачи информации с защитой от ошибок | 1989 |

|

SU1669080A1 |

| Устройство преобразования дискретных сигналов | 1977 |

|

SU738146A1 |

| Устройство передачи информации с защитой от ошибок | 1984 |

|

SU1188893A1 |

| Устройство передачи сообщений | 1985 |

|

SU1506555A1 |

| Устройство для многоканальной передачи сигналов с коррекцией ошибок | 1978 |

|

SU720734A1 |

| Устройство для измерения ортогональных составляющих сигнала | 1982 |

|

SU1091082A1 |

| УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ИЗМЕРИТЕЛЬНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2007760C1 |

| Устройство для передачи информации с контролем ошибок высокой кратности | 1987 |

|

SU1480129A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1562971A1 |

Авторы

Даты

1980-05-15—Публикация

1977-05-27—Подача