(54) ФОРМИРОВАТЕЛЬ БИПОЛЯРНЫХ ИМПУЛЬСОВ

отдельности к одномуИз двух выходов 15, 16 регистра 17 записи и считьшания.

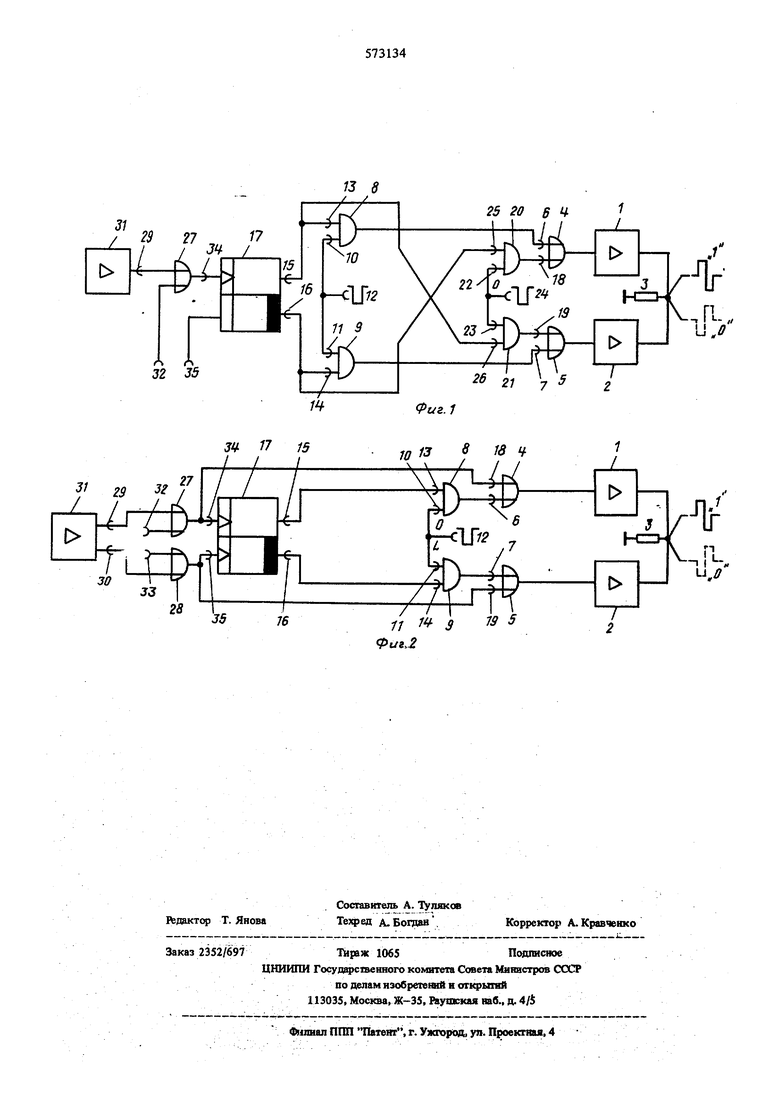

В зависимости от полярности первого разрядного импульса к первому входу 18 и 19 одной из схем ИЛИ подводится управляющий импульс для пуска первого разрядного импульса, который получается из какой-либо одной схемы И 20, 21 (фиг. 1). Каждая из схем И 20, 21 имеет первый и второй входы. Первые входы 22, 23 связаны между собой, на их точку соединения подается тактовый импульс 24 для пуска первого разрядного импульса. Вторые входы 25, 26 подключены к выходам 15, 16 регистра 17.

Таким образом, к каждому выходу 15, 16 регистра 17 подключено всего две схемы И 8, 21 (9, 20), причем схемы И 8, 20 принадлежат к усилителю 1, а схемы И 21, 9 - к усилителю 2.

Управляющий импульс для пуска первого разрядного импульса (фиг. 2) получается из какой-либо одной схем ШШ 27, 28. Каждая схема ИШ. 27, 28 имеет первый и второй входы. Первый вход схемы 27 связан с одним выходом 29, а первый вход схемы 28 связан с другим выходом 30 выходного каскада нелинейного усилителя считьшания 31. Вторые входы 32, 33 схем ИЛИ 27, 28 служат для записи внеицшх информации. Регистр 17 используется в качестве регистра записи (считьшания), следовательно, на его входы 34, 35 управления через схемы ИЛИ 27, 28 и связывающие звенья, например конденсаторы (на чертежах не показаны), поступает выходной сигнал выходного каскада нелинейного усилителя 31 считьшания кхш же внеи-кий сигнал, поданный на вход 32, 33. Выходной каскад усилителя 31 счктьюания (фиг. 1) имеет только один выход 29, вследствие чего необходимо производдть перед каждой новой операцией записк .ГйЖ сброса регистра 17 на его входе 35.

Ра.бота устройства протекает следующим образом.

Перед каждой операцией записи внешних или считываемых информации регистр 17 приводится подачей импульса сброса на его вход 35 в свое состояние покоя, в котором на выходе 15 появляется сигнал 1, а на выходе 16 - сигнал О, При записи информащш на выходе 29 выходного каскада нелинейного усилителя 31 считьшания или же на входе 32 схемы ИЛИ появляется импульс, который переводит регистр 17 в рабочее состояние, характеризуемое сигналом О на выходе 15 и соответственно, сигналом 1 на выходе 16.

Появивщийся теперь на первых входах 22, 23 схем И 20, 21 тактовый импульс 24, который соответствует сигналу 1, вызьтает на выходе схемы И 20 импульс, который через схему ИЛИ 4 поступает на усидштель 1, при этом положительный первый разрядный импульс появляется на нагрузке 3. За тактовым импульсом 24 непосредственно следует соответствующий сигналу 1 тактовьш импульс 12, который аналогичным образом через схему И 9 и схему ИЛИ 5 поступает на усилитель 2. При загшси информации О на входе 34 регистра 17 управляющий импульс отсутгствует, следовательно, на нагрузку 3 подаются отрицательный первый разрядный импульс и непосредственно следующий за ним полохжтеяьный второй разрядный импульс.

Аналогично работает и электрическая схема на фиг. 2. Однако управляю1ций иштульс для пуска первого разрядного импульса появляется на выходе одной из схем ИЛИ 27, 28. Сигнал на выходе 29 или 30 выходного каскада нелинейного усилителя 31 считывания или внешний сигнал на входе 32 или 33 уже имеет необходимую для щштельноаи первого разрядного импульса ишрину. Операщ я сброса регистра 17. для перевода его в С9стояние покоя отпадает. Электрические схемы Ki фиг. 1 и 2 связаны известным образом.

Формула изобретения

Формирователь Биполярных импульсов, содержащий не шнейный усилитель с одним или с двумя выходами, оконечньЬ усилители, нагруженные на общую нагрузку, внеишие источники сигналов, первые к вторые cxe.lЬI ИЛИ, регистр записи и считывания, входы которого соединены с выходагии первых схем ИЛИ, а его выходы - с входами схем И, отличающийся тем, что, с целью упрощения формирователя, каждый выход нелинейного усилителя соединен с входом одной из первых схем ИЛИ, пртчем их вторые входы и параллельно соединенные входы И подключены к внешним источникам сигналов, выходы схем И соединены через вторые схемы ИЛИ с оконечными усилителями, а остальные ьходы вторьк схемИШ соединены с входамн регистр.1 записи и считывання. / 2S 27 , /7 - 34-/ 21 7

гЧ

Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1984 |

|

SU1265776A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

Авторы

Даты

1977-09-15—Публикация

1970-09-23—Подача