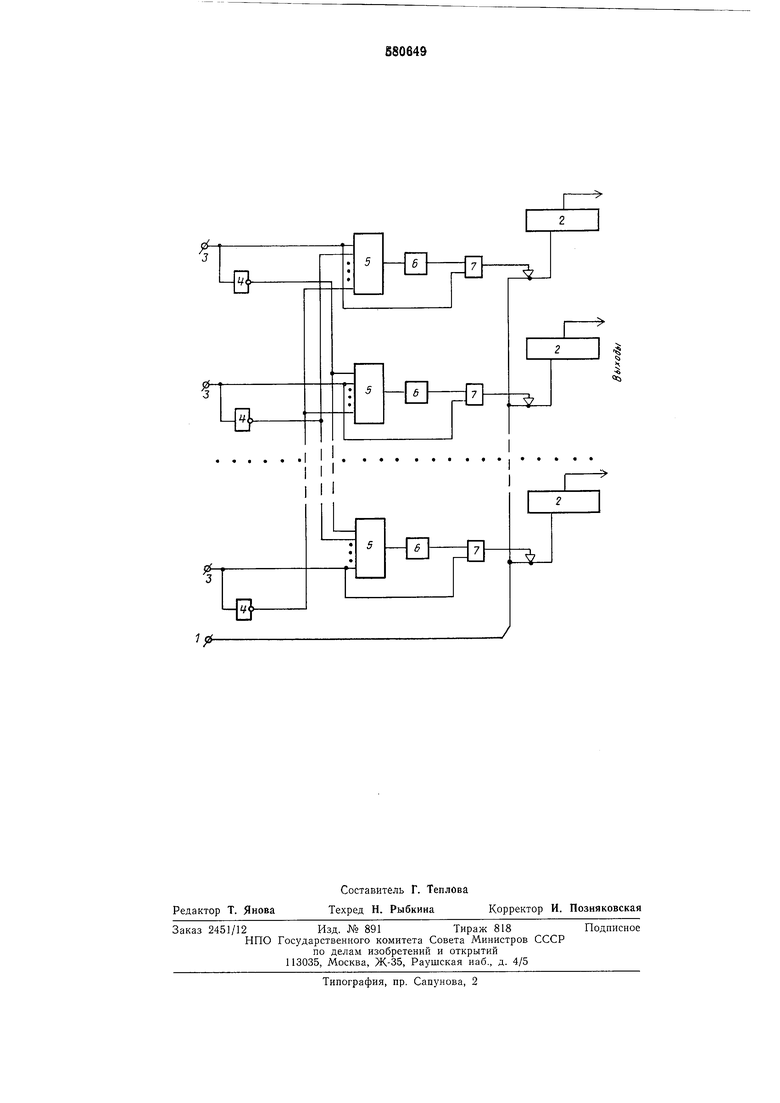

из управляющих шин 3 информация, совпадающая во времени с этим имиульсом записи, заносится в статический регистр 2, связанный с этой управляющей шиной 3.

Когда на одну из управляющих шин 3 приходит импульс записи, то он через инвертор

4этого канала в виде сигнала «Запрет поступает на входы многовходовых элементов И

5всех остальных каналов.

Этот же импульс записи поступает на соответствующий вход элемента И 5 и второй вход элемента И 7 этого канала. На первый вход этого элемента И 7 импульс записи поступает через элемент И 5 и линию задержки 6, в результате чего на выходе элемента И 7 появляется уменьшенный по длительности импу.тьс, задний фронт которого совпадает с задним фронтом импульса записи, а передний фронт задержан на время, определяемое линией задержки 6. С помощью импульса на выходе элемента И 7 происходит запись информации в статический регистр 2 этого канала.

Таким образом, если на заправляющие шины 3 канала поступает импульс помехи длительностью меньше времени задержки в линии задержки 6, то на выходе элемеита И 7 не появляется импульс записи, а статический регистр 2 не принимает ложную информацию. Величина времени задержки линии задержки

6выбирается больше длительностей возможных помех по управляющим шинам 3, кроме того, длительность импульса на выходе элемента И 7, равная разности длительности импульса записи и времени задержки, должна быть достаточной для надежного приема информации статическим регистром 2.

При одновременном возникновении на двух

или более управляющих, шинах 3 импульсов помехи через инверторы 4 этих каналов ложные импульсы в виде сигналов «Запрет поступают на входы многовходовых элементов

И 5 всех каналов, и ни в один из статических регистров 2 в момент действия такой помехи не записывается ложная информация.

Предлагаемое устройство иовыщает помехоустойчивость быстродействующих вычислнтельных устройств, содержащих системы регистров ириема информацин, имеющих единую входную магистраль информации и раздельные управляющие шины.

Формула изобретения

Устройство приема цифровой информации, содержащее общую шину входной информации, соединенную с первыми входами п статических регистров, и п управляющих щин, о тличающееся тем, что, с целью повышения помехоустойчивости, к управляющему входу калчдого статического регистра подключены введенные инвертор и последовательно соединенные многовходовый элемент И, линия задержки и двухвходовый элемент И, причем каждая управляющая шина соединена с первыми входом многовходового элемента И, входом инвертора и вторым входом двухвходового элемента П, выход инвертора соединен с другими входами каждого п-1 многовходового элемента И.

Источники информации,

принятые во внимание при экспертизе

1. Майоров С. А. Принципы организации цифровых машин. Л., «Машиностроение, 1974, с. 123.

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Преобразователь двоичного кода в число-импульсный код | 1977 |

|

SU734671A1 |

| Регистр сдвига | 1978 |

|

SU780046A1 |

| Устройство для синхронизации импульсов | 1979 |

|

SU841099A1 |

| Логическое переключающее устройство для раздельного управления группами тиристорного циклоконвертора | 1980 |

|

SU1010715A1 |

| Входное устройство для электронных часов | 1990 |

|

SU1774471A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU875606A1 |

| Устройство для определения порядковых номеров ванн гальваноаппарата с диагностикой цепей элементов считывания | 1987 |

|

SU1421812A1 |

| Устройство для контроля серий импульсов | 1987 |

|

SU1534751A1 |

Авторы

Даты

1977-11-15—Публикация

1976-05-17—Подача