вход которого подключен через инвертор к выходу генератора тактовых импульсов, а третий вход подключен ко входу логического элемента ИЛИ и к выходу формирователя импульсов, причем выход логического элемента ЗИ подкл{очен ко второму входу дополнительного формирователя импульсов , первый вход которого подклюjieH к шине синхронизирующих импульсов , а выход подключен ко входам синхронизации 0-триггеров статического регистра, D-входы которых подключены к выходам п-тактного распределителя импульсов, при этом вход D п-го D-триггера подключен к выходу п-1 п-тактного распределителя импульсов.

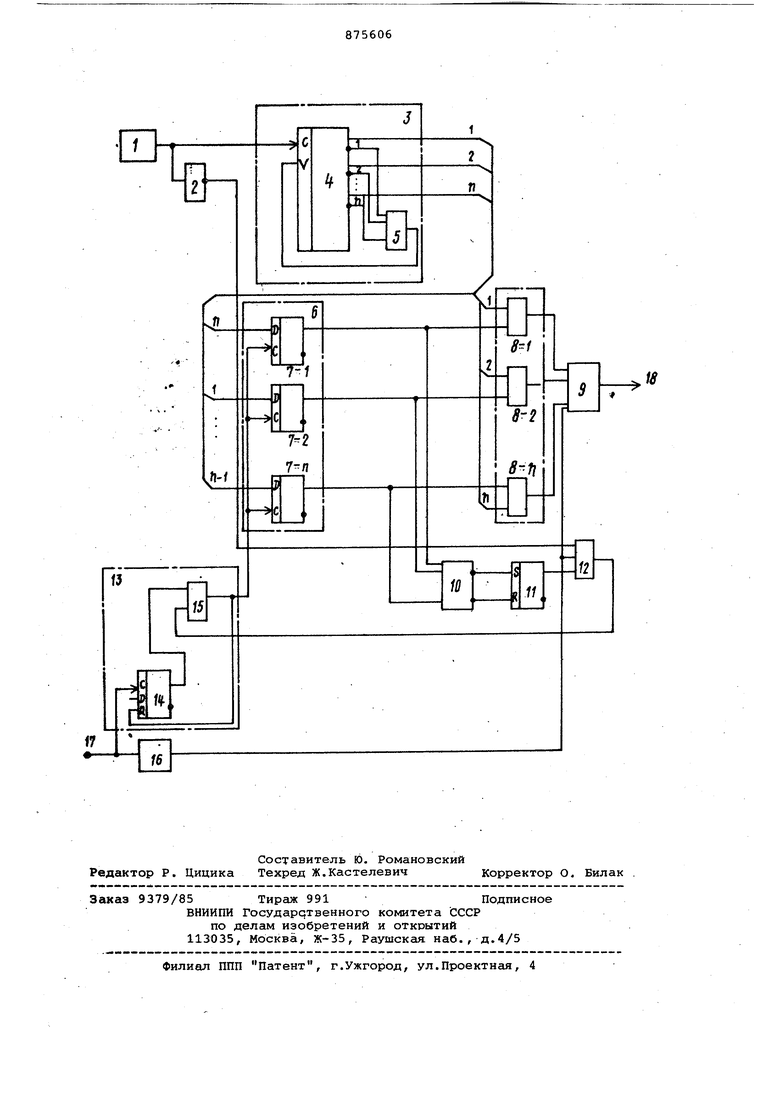

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство для синхронизации импульсов содержит генератор 1 тактовых импульсов, инвертор 2, п-тактный распределитель 3 импульсов, состоящий из регистра 4 сдвига и п-входового логического элемента И 5, статический регистр б из о-триггеров 7-1 - 7--П, блок сравнения из логических элементов 2И 8-1 - 8-п, логический элемент ИЛИ 9, блок 10 контроля четности, RS-триггер 11, логический элемент ЗИ 12, дополнительный формирователь 13 импульсов, содержащий 0-триггер 14 и логический элемент ИЛИ 15, формирователь 16 импульсов., шину 17 синхронизирующих импульсов, выходную шину 18.

/

Устройство работает следующим образом. .

При поступлении импульса синхронизации на шину 17 формирователь 16 формирует по переднему .фронту импульса синхронизации сигнал, длительность которого равна периоду тактовых импульсов Т, генерируемых генератором 1. Данный импульс с выхода формирователя 16 снимает блокировку -ПО Одному из входов логического элемента ЗИ 12 на время, равное периоду тактоврх импульсов Т и через.логический элемент ИЛИ 9 проходит на выход устройства - шину 18. По переднему фронту импульса синхронизации срабатывают последовательно включенные 0-триггер 14 и логический элемент ИЛИ 15 дополнительного формирователя 13. По переднему фронту сигнала с выхода дополнительного формирователя 13 происходит запись информации с выхода п-тактного распределителя 3 в О-триггеры статического регистра 6. Распределитель 3 импульсов реализован на регистре 4 сдвига, счетный вход которого соединен с выходом генератора 1, а вход V записи единищл в первый разряд подключен к выходу дешифратора 5. Этим обёспечивается. контроль состояний регистра 4 сдвига, т.е. возможность циркуляции в регистре сдвига 4 п-тактного распределителя 3 импульсов только одной единицы (высокий уровень напряжения). Реализация п-тактного распределителя импульсов может быть выполнена любыми известными средствами, например с помощью многоотводной линии задержки .

Сигнал, вызыва;ющий запись информации в статический регистр 6, поступает на вход R D-триггера 14 и производит установку последнего в исходное (нулевое) состояние. Длительность вышеуказанного сигнала с выхода формирователя 13 превьшает время срабатывания D-триггера данной элементной базы на время задержки включения одного элемента (логический Элемент ИЛИ 15), что обеспечивает уверенное срабатывание Dтриггеров - статического регистра 6. При правильной перезаписи информации с выхода п-тактного распределителя 3 в статический регистр 6 на параллельных выходах последнего присутствует только одна единица. При этом состояния выходов блока 10 контроля четности, представляющего собой блок полусумматоров (см. микросхемы серии 100, 155 100ИЕ 160, К155 ИП2) , определяют установку RS-триггера 11 в нуль. Низкий уровень напряжения с выхода RS-триггера 11 запрещает работу логического элемента ЗИ 12. В этом режиме импульсная последовательность с 1-го выхода п-тактного распределителя 3 поступает через логический элемент 2И из блока сравнения и логический элемент ИЛИ 9 на шину 18. Открытое состояние данного логического элемента 2И обеспечивается при срабатывании 0-триггера статического регистра 6. Такое опережение по фазе на интервал, равный периоду тактового импульса Т, необходимо для обеспечения компенсации суммарной задержки срабатывания последовательно включенных D-триггера 14, логического элемента ИЛИ 15, Dтриггера статического регистра, логического элемента 2И блока сравнения. Данная суммарная задерж а может превысить время, равное периоду Т, если период Т выбран минимально допустимым для некоторой элементной базы, что необходимо из условий достижения высокой точности синхронизации.

При записи ложной информации в статический регистр 6 (например, все D-триггеры статического регистра 6 установлены в нулевое состояние или присутствует высокий уровень на выходе двух D-триггеров, что возможно при совпадении фронтов импульса синхронизации и тактового сигнапа) с помощью блока контроля четности 10, выявляющего наличие ложной информации в статическом регистре 6, обеспечивается установка RS-триггера 11 в единичное состояние. Дополнительный (повторный) сигнал для записи информации с параллельных выходов п-т ктного распределителя 3 импульсов .в статический регистр 6 формируется в момент, когда информация на выходах п-тактного распределителя импульсов не меняется, т.е. со сдвигом на 180 относительно сигнала, производящего сдвиг 1 в регистре 4 сдвига п-тактного распределителя 3. Данный дополнительный сигнал, поступающий на входы синхронизации D-триггеров - статического регистра 6 с выхода элемента ЗИ 12 через элемент ИЛИ 15 формируется в момент совпадения следующих трех сигнс1лЬв на входах логического элемента ЗИ i2; сигнала с выхода формирователя 16, длительность которого равна периоду тактовых импульсов Т, сигнала с выхода инвертора 2 с длительностью Т/2, представляющего собой инверсию тактовой последовательности (скважность 2), сигнала постоянного уровня с выхода RS-триггера 11. После исправления ошибки в информации, .записанной в статический регистр 6 блок 10 контроля четности выключает RS-триггер 11 и блокирует логический элемент ЗИ 12. Таким образом, в предлага1емом устройстве обеспечивается определение наличия ложньох состояний и исправления ошибки в режиме достижения максимальной точнсэсти синхронизации, допускаемой быстродействием выбранной элементной базы.

Формула изобретения

Устройство для синхронизации импульсов, содержащее :генератор тактовых импульсов, выход которого соединен со входом п-тактного распределителя импульсов, п параллельных выходов которого подключены к первому входу каждого логического элемента 2И блока сравнения, выходы которых подключены ко входам логического элемента ИЛИ, выход которого является: выходом устройства, формирователь импульсов, вход которого подключен к шине синхронизации импульсов, статический регистр из п-триггеров, о тличающееся тем, что, с

0 целью повышения надежности, в него дополнительно введены- формирователь импульсов, инвертор, RS-триггер, логический элемент ЗИ и блок контроля четности, п входов которого подклю5чены к соответствующим выходам Dтриггеров статического регистра и вторым входам логических элементов 2И блок сравнения, а первый и второй выходы блока контроля четности

0 подключены к соответствующим входгии RS-триггера, выход которого подключен к первому входу логического элемента ЗИ, второй вход которого подключен через инвертор к выходу генератора тактовых импульсов, а тре5тий вход подключен ко входу логического элемента ИЛИ и выходу формирователя импульсов, причем выход логического элемента ЗИ подключен ко второму входу дополнительного

D формирователя импульсов, первый вход которого подключен к шине синхронизирукяцих импульсов, а выход подключен ко входам синхронизации Dтриггеров статического регистра, D5входы которых подключены к выходам п-тактного распределителя импульсов, при этом вход D п-го D-триггера подключен к выходу п-1 п-тактного распределителя импульсов.

0

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 474926, кл. Н 03 К 5/18, 1973.

2.Авторское свидетельство СССР

5 617834, кл. Н 03 К 5/18, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| Генератор псевдослучайных последовательностей | 1985 |

|

SU1298868A1 |

| Система управления стендом для диагностирования технического состояния транспортных средств | 1988 |

|

SU1553875A1 |

| Устройство для формирования пачек импульсов | 1991 |

|

SU1812617A1 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Устройство для измерения частоты вращения | 1989 |

|

SU1666964A1 |

| Многофазный резонансный стабилизатор напряжения | 1990 |

|

SU1800451A1 |

Авторы

Даты

1981-10-23—Публикация

1980-02-29—Подача