1

Изобретение относится к вычислительной технике и может быть использовано в различных устройствах автоматики и специализированных вычислительных устройствах, в которых крутизна ириращеиия функции меняется в 2 раз (где k - целое положительное число) при изменении входной информации на один дискрет для разных участков функции.

Известно устройство для перекодирования дискретной информации 1, содержащее ячейку памяти п-разрядного кода, блок преобразования значения двоичного кода в разрядные весовые эквиваленты десятичной системы, узел оиеративиой памяти, блок считывания и иреобразования кода сумматора в заданный код, временной распределитель сигналов синхронизации, узел формирования исполнительных команд.

Указанное устройство имеет такие недостатки, как низкое быстродействие и сложность.

Известно также наиболее близкое по технической сущиости к нзобретеиию устройство для воспроизведения фуикции с крутизной, не превышающей 2«, содержащее регистр адреса, вход которого соедииен с входной щиной устройства, а первый выход регистра адреса через дешифратор - с входом шифратора 2.

Иедостатком его является наличие многоразрядиых дешифратора и шифратора. Цель изобретения - упрошение устройства. Это достигается тем, что в него введены сумматор и два регистра сдвига, иервые входы которых соединены с вторым выходом регистра адреса, вторые входы регистров сдвига - с выходом дешифратора, а выходы первого регистра сдвига и шифратора подключены к соответствующим входам сумматора, выход которого и выход второго регистра сдвига соединены с выходной шииой устройства.

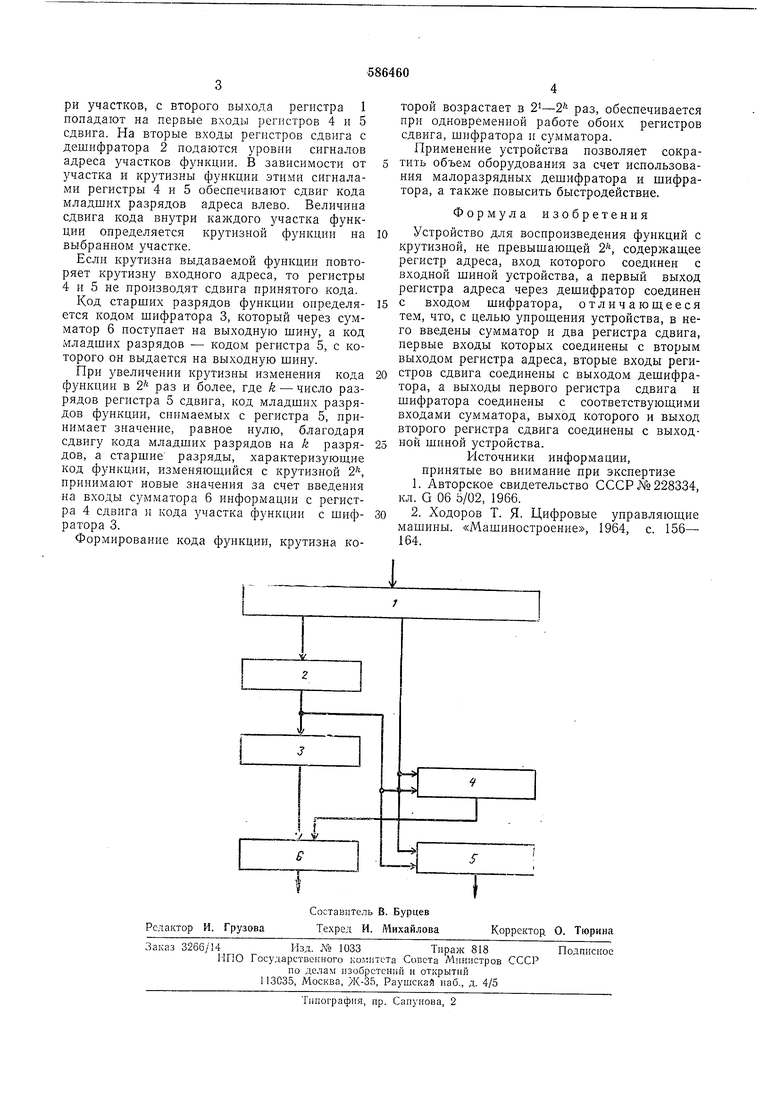

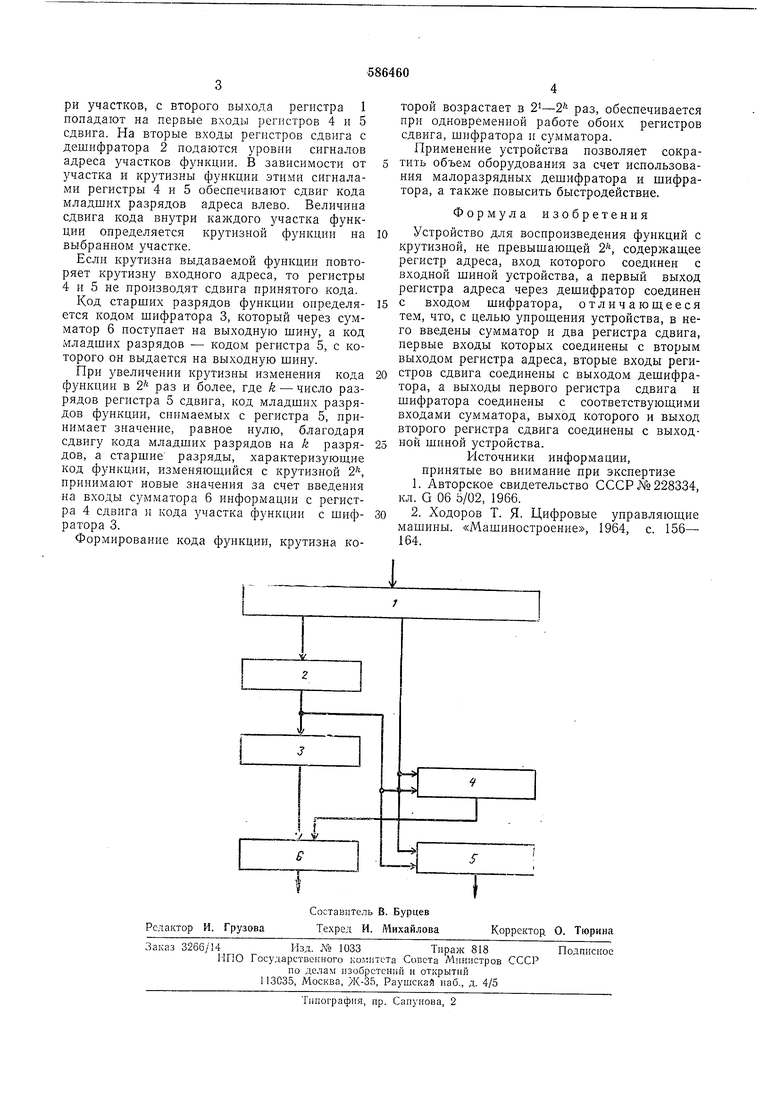

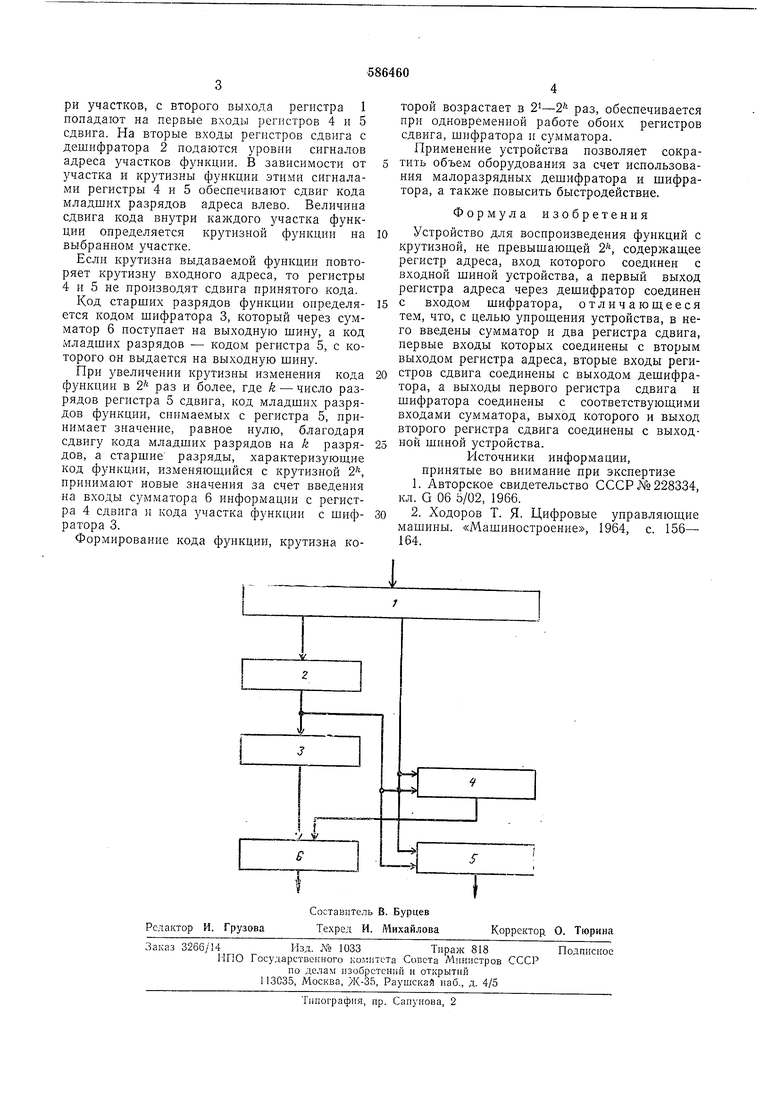

Структурная схема устройства представлена на чертеже.

Она содержит регистр 1 адреса, деи1ифратор 2, шифратор 3, первый 4 и второй 5 регистры сдвига, сумматор 6.

Работает устройство следующим образом. Код адреса фуикции с входной шины устройства подается на вход регистра 1. Старшие разряды кода адреса, опре.о;еляющие линейные участки адреса функции, ностуиают с регистра 1 на дешифратор 2, с выхода которого адрес участка функции проходит на шифратор 3 кода адреса участка фуикции.

С выхода шифратора 3 сформированный для выбранного участка код адреса функции выдается на сумматор 6. Младшие разряды адреса, онределяющие адрес функции виутри участков, с второго выхода регистра 1 попадают на первые входы регистров 4 и 5 сдвига. На вторые входы регистров сдвига с дешифратора 2 подаются уровии сигналов адреса участков функции. В зависимости от участка и крутизны функции этими сигналами регистры 4 и 5 обеспечивают сдвиг кода младших разрядов адреса влево. Величина сдвига кода внутри каждого участка функции определяется крутизной функции на выбранном участке.

Если крутизна выдаваемой функции повторяет крутизну входного адреса, то регистры 4 и 5 не производят сдвига принятого кода.

Код старших разрядов функции определяется кодом шифратора 3, который через сумматор 6 поступает на выходную шину, а код младших разрядов - кодом регистра 5, с которого он выдается на выходную шину.

При звеличении крутизны изменения кода функции в 2 раз и более, где k - число разрядов регистра 5 сдвига, код младших разрядов функции, снимаемых с регистра 5, принимает значение, равное пулю, благодаря сдвигу кода младших разрядов на k разрядов, а старшие разряды, характеризуюшие код функции, изменяющийся с крутизной 2 принимают новые значения за счет введения па входы сумматора 6 информации с регистра 4 сдвига и кода участка функции с шифратора 3. Формирование кода функции, крутизна которой возрастает в раз, обеспечивается при одновременной работе обоих регистров сдвига, шифратора и сумматора.

Применение устройства позволяет сократить объем оборудования за счет использования малоразрядных дешифратор а и шифратора, а также повысить быстродействие.

Формула изобретения

Устройство для воспроизведения функций с крутизной, не превышающей 2, содержащее регистр адреса, вход которого соединен с входной шиной устройства, а первый выход регистра адреса через дешифратор соединен

с входом шифратора, отличающееся тем, что, с целью упрошения устройства, в него введены сумматор и два регистра сдвига, первые входы которых соедипены с вторым выходом регистра адреса, вторые входы регистров сдвига соединены с выходом дешифратора, а выходы первого регистра сдвига и шифратора соедипены с соответствующими входами сумматора, выход которого и выход второго регистра сдвига соединены с выходпой шиной устройства.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №228334, кл. G 06 5/02, 1966.

2. Ходоров Т. Я. Цифровые управляющие машины. «Машиностроение, 1964, с. 156- 164.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1975 |

|

SU568052A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

| Запоминающее устройство | 1978 |

|

SU769622A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Конвейерное буферное запоминающее устройство для систем обработки изображений | 1989 |

|

SU1751769A1 |

| Цифровой нелинейный масштабирующий преобразователь | 1981 |

|

SU1057953A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для ввода информации | 1978 |

|

SU746484A1 |

Авторы

Даты

1977-12-30—Публикация

1975-12-19—Подача