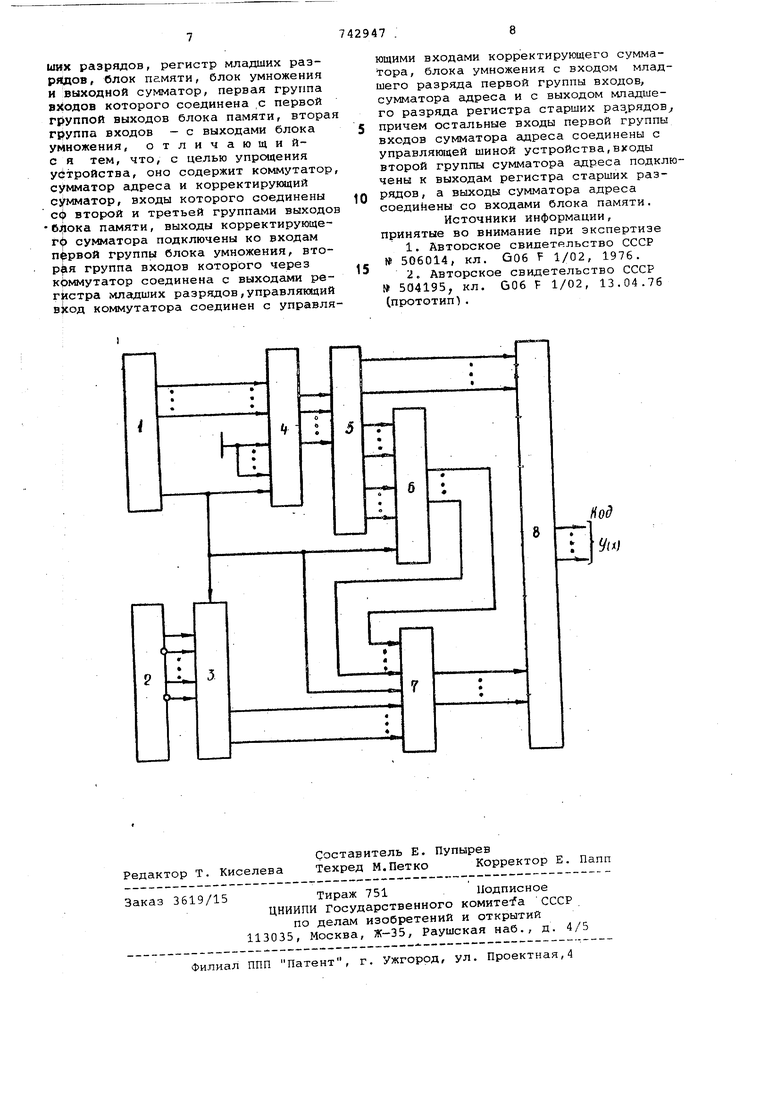

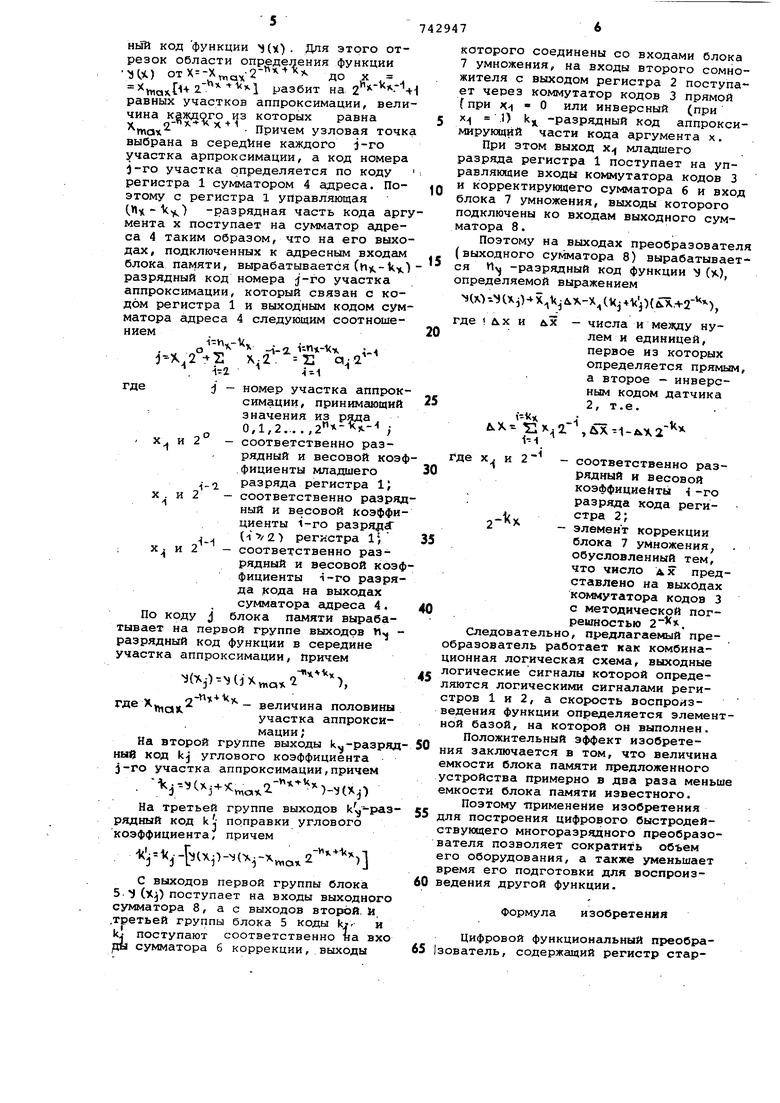

Изобретение относится к вычислительной технике и может быть использовано для сопроизведения различных функций (например синусов и косинусов) одного аргумента изменяющегося с высокой скоростью. Известен цифровой функциональный преобразователь, имеющий в своем составе оперативные или постоянные запоминающие устройства. Так,самыми быстродействующими из них являются специализированные устройства, выпол ненные на основе постоянных запоминающих устройств ЗУ) или устройств типа дешифратора-шифратора,выполненные на логических комбинационных эле ментах ij . Наиболее близким к предлагаемому является цифровой фукнциональный пре образователь, содержащий регистр старших разрядов, регистр младших разрядов, блок памяти, блок умножени и выходной сумматор, первая группа входов которого соединена с первой группой выходов блока памяти, вторая группа входов - с выходами блока умножения. Запоминающий блок известного устройства содержит дешифратор блок памяти значений функции в узло.г вйх точках участков .аппроксимации, блок памяти угловых коэффициентов участков аппроксимации, два блока логических элементов И и две группы логических элементов ИЛИ, с первой из которых снимается код значения функции в узловой точке j-ro участка аппроксимации, а со второй - код углового коэффициента j-ro участка аппроксимации. Причем номер j-ro участка аппроксимации определяется выражением j.-r,2-1 1. И может принимать значения из ряда 0,1,) где .. - разрядность регистра старших разрядов; разрядность регистра . младших разрядов , X; и 2 - соответственно разрядный и весовой коэффициенты 1-го разряда регистра млсщших разрядов. Следовательно, емкость ЗУ генератора составляет (n-i kv,) dUw, где Vlsj - разрядность воспроизводимой генератором функции, k - разрядность углового коэффициента, вырабатываемого .на выходах второй группы ЗУ Работа генератора (преобразователя) основана на принципах кусочнолинейной аппроксимации, при этом он обладает быстродействием, близким к бы(5тродействию устройств, выполненны на основе ЗУ или логических устройст дешифратора-шифторатора и простору и точность устройств, построенныЦ по методу кусочно-линейной аппр4ксимации 2 . (Однако, так как при построении уст ройства узловые точки выбра;ны в йачале .участков аппроксимации,числ определяется точностью воспроизведения функции, то ЗУ генерато ра ; имеет значительную емкость, что Выбывает определенные трудности при построении на основе этого генераTOjba устройства для воспроизведения многоразрядной функции. Цель изобретения упрощение устройства. Поставленная цель достигается те что устройство содержит коммутатор, сумматор адреса и корректирукяций су , входы которого соединены со втброй и третьей группами выходов блока памяти, выходы корректирующег сумматора подключены ко входам первой группы блока умножения, вторая группа входов которого через коммутатор соединена с выходами регистра младших разрядов., управляющий вход коммутатора соединен с управляющими входами корректирующего сумматора, блока умножения, со входом младшего разряда первой группы входов сумматора адрес и с выходом младшего раЬряда регистра старших разрядов, причем остальные входы первой группы: входов сумматора адреса соединены с управляющей шиной устройства входы второй группы сумматора адрес подключены к выходам регистра старших разрядов, а выходы сумматора ад реса соединены со входами блока памяти . На чертеже приведена схема цифрового функционального преобразователя . Схема содержит регистр 1 старших разрядов и регистр 2 младших разрядов, коммутатор 3, подключенный к пр}йиым и инверсным выходам регистра 2, кзумматор 4 адреса, входы первой группы которого подключены к выхода старших разрядов регистра 1, выход младшего разряда которого соединен со входом младшего разряда первой группы входов сумматора адреса 4, входы остальных разрядов второ группы которого подключены к шине Логического нуля блопамяти,имеющего три группы ыходов и группы адресных входов, одключенных к выходу переполнения к выходам суммы сумматора 4 адреса , корректирующий сумматор 6, у коорого входы первой и второй группы соответственно соединены с выходами второй и с выходами третьей групп блока 5, блок 7 умножения, выходной сумматор 8. Регистр старших разрядов определяет старшие разряды - i-разрядного кода аргумента ( и), которые определяют j-тый участок, на котором аппроксимируется функция (%-}Регистр младших разрядов определяет те младшие разряды аргумента, по которым производится аппроксимация функции на -том участке. Сумматор 4 адреса представляет i собой (, --1) -разрядный параллельный комбинационный сумматор. Адрес сумматором 4 адреса определяется () -разрядным кодом,старший разряд которого снимается с выхода переполнения сумматора 4. Блок памяти универсального преобразователя может быть выполнен на основе оперативного ЗУ или постоянного ЗУ с электрической перезаписью информации, а блок памяти специализированного преобразователя может быть выполнен, напрлмер по схеме дешифратора-шифратора на комбинационных логических элементах. Дешифратор такого блока имеет () входов и (2 -«-1) выходов и управ ляет работой шифратора таким образом, что на выходах первой группы блока памяти вырабатывается п, -разрядный код функции (рв узловой точке середины j-ro участка аппроксимацииj на выходах второй группы блока памяти вырабатывается k разрядный код углового коэффициента k , представляю- ющий собой приращение функции на правой (левой) половина j-ro участка аппроксимации; на выходах третьей группы блока памяти вырабатывается Ц разрядный код kj поправки углового коэффициента, представлякяций собой разность приращений функции на полуучастках j-ro участка аппроксимации. Следоват ьно, емкость блока памяти предлагаемого устройства составляет С2 (Пч,,,) 2 V11C5-UTТак как Ц в несколько раз меньше , то емкость блока памяти предложенного преобразователя примерно в два раза меньше емкости блока памяти прототипа. Работа преобразователя основана на принципах кусочно-линейной аппроксимации, при этом преобразователь по П -разрядному коду аргумента х, изменяющемуся., например от |цо д вырабатывает п -разрядный код функции (к) . Для этого отрезок области определения функции П) отХ-Х „ 2 ДО .г . . разбит на 2 равных участков аппроксимации, вели чина из которых равна Причем узловая точк выбрана в середине каждого -j-ro участка арпроксимадии, а код номера j-ro участка определяется по коду регистра 1 сумматором 4 адреса. Поэтому с регистра 1 управляющая .) -разрядная часть кода арг мента X поступает на сумматор адреса 4 таким образом, что на его выхо дах, подключенных к адресным входам блока памяти, вырабатывается (,-1,t разрядный код номера -го участка аппроксимации, который связан с кодом регистра 1 и выходным кодом сум матора адреса 4 следующим соотношениемo- x-Ч -.2. i-nn-V-. : r-, Х:2. S О2 . 1-2 где j - номер участка аппрок симации, принимающий значения из ряда 0,1,2... ., ; х и 2 - соответственно разрядный и весовой коэ .фициенты младшего - разряда регистра i; X . и 2 - соответственно разря ный и весовой коэффи циенты i-ro разрядгг ( регистра 1, ; X и 2 - соответственно разрядный и весовой коэ фициенты i-ro разря да кода на выходах сумматора адреса 4. По коду j блока памяти вырабатывает на первой группе выходов Y( разрядный код функции в середине участка аппроксимации. Причем }{%.j)--M(), где X,j, - величина половины участка аппроксимации ; На второй группе выходы k -разряд ные код kj углового коэффициента j-ro участка аппроксимации,причем . .),(x) На третьей группе выходов k( рядный код ki поправки углового коэффициента, причем V .(.i-x,2- С выходов первой группы блока 5. (Х) поступает на входы выходного сумматора 8, а с выходов второй, и. .третьей группы блока 5 коды и k| поступают соответственно тла вхо сумматора б коррекции, выходы 7 которого соединены со входами блока 7 умножения, на входы второго сомножителя с выходом регистра 2 поступает через коммутатор кодов 3 прямой Гпри х « О или инверсный (при х .) k -разрядный код аппроксимирукхдий части кода аргумента х. При этом выход х младшего разряда регистра 1 поступает на управляющие входы коммутатора кодов 3 и корректируницего сумматора 6 и вход блока 7 умножения, выходы которого подключены ко входам выходного сумматора 8. Поэтому на выходах преобразователя (выходного сумматора 8) вырабатывается -разрядный код функции У (х), определяемой выражением MX)-SU.j)- .j лх-Х CKj+Vp(/.), где t л,х и x - числа и мелзду нулем и единицей, первое из которых определяется прямым, а второе - инверсным кодом датчика 2, т.е. Л .1-л.х2 де Xj и 2 -соответственно разрядный и весовой коэффициенты -го разряда кода регистра 2; -элемент коррекции блока 7 умножения, обусловленный тем, что число дх представлено на выходах коммутатора кодов 3 с методической погрешностью 2. Следовательно, предлагаемый пребразователь работает как комбинаионная логическая схема, выходные огические сигналы которой опредеяются логическими сигналами регитров 1 и 2, а скорость воспроизедения функции определяется элементой базой, на которой он выполнен. Положительный эффект изобретеия заключается в том, что величина мкости блока памяти предложенного стройства примерно в два раза меньше мкости блока памяти известного. Поэтому -применение изобретения ля построения цифрового быстродейтвующего многоразрядного преобразоателя позволяет сократить объем го оборудования, а также уменьшает ремя его подготовки для воспроизедения другой функции. Формула изобретения Цифровой функциональный преобраователь, содержащий регистр старших разрядов, регистр младших раэря(дов, блок памяти, блок умножения и выходной сумматор, первая группа входов которого соединена с первой группой выходов блока памяти, вторая группа входов - с выходами блока умножения, отличающийс я тем, что, с целью упрощения устройства, оно содержит коммутатор, сумматор адреса и корректирукяций сумматор, входы которого соединены сф второй и третьей группами выходов 6j(iOKa памяти, выходы корректирующег сумматора подключены ко входам первой группы блока умножения, втор|1Я группа входов которого через кЪммутатор соединена с выходами регистра младших разрядов,управляющий коммутатора соединен с управляющими входами корректирующего сумматора, блока умножения с входом младшего разряда первой группы входов, cyiviMaTopa адреса и с выходом младшего разряда регистра старших раз,рядов причем остальные входы первой группы входов сумматора адреса соединены с управляющей шиной устройства,входы второй группы сумматора адреса подключены к выходам регистра старших разрядов , а выходы сумматора адреса соедийены со входами блока памяти,

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетр.льство СССР № 506014, кл. G06 1 1/02, 1976.

2.Авторское свидетельство СССР 504195, кл. G06 F 1/02, 13.04.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU928347A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Функциональный преобразователь кода угла | 1978 |

|

SU716042A1 |

| Цифровой синусно-косинусный преобразователь | 1978 |

|

SU800923A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

Под Уti)

Авторы

Даты

1980-06-25—Публикация

1977-05-04—Подача